# 19MZC12&19RAC12 / MICROPROCESSOR AND APPLICATIONS

# Prepared by

Mr.C.RAMKUMAR,

Assistant Professor,

Department of Electrical and Electronics Engineering,

Muthayammal Engineering College (Autonomous),

Rasipuram – 637 408.

# **Course Objective**

- 1.To study the basic concept of 8085 microprocessor

- 2.To study the basic concept of 8051 microcontroller

- 3.To introduce the PIC microcontroller and programming of 8085 and 8051

- 4. To study the basic concept of interfacing

- 5. To study the application of Processors and controllers

# DIFFERENCE BETWEEN MICROPROCESSOR AND MICROCONTROLLER

| MICROPROCESSOR                                               | MICROCONTROLLER                                               |  |

|--------------------------------------------------------------|---------------------------------------------------------------|--|

| A microprocessor is a general purpose device is called a CPU | A microcontroller is a dedicated chip is called a single chip |  |

| Microprocessor based system design is complex                | Microcontroller based system design is simple                 |  |

| It is flexible which means we can change the size            | It is not flexible                                            |  |

| Microprocessor do not have power saving features             | Microcontrollers have the power saving mode                   |  |

| Size of RAM / ROM can vary                                   | Size of the RAM / ROM fixed                                   |  |

| It does not contain internal memory                          | It contain internal memory                                    |  |

| Cost is high                                                 | Cost low                                                      |  |

# UNIT 1 – 8085 PROCESSOR

# INTRODUCTION

- A Microprocessor is known as a Central Processing Unit.

- It is fabricated on a single chip

- The first microprocessor was Intel 4004 introduced in 1971. It is a 4 bit processor.

- The first microprocessor to make into a home computer was Intel 8080.It is a 8 bit computer on one chip introduced in 1974.

- In 1976 updated the intel 8080 design with 8085 by adding two instruction to enable / disable the interrupt and serial port

- In 1978 introduced the intel 8086. It is a 16 bit processor.

- In 1980 introduced the intel 8087.

# INTRODUCTION TO MICROCOMPUTER SYSTEM

Microcomputer system is the interconnection of CPU, memory and input / output device CPU

Central Processing unit is the brain of the microcomputer system. It coordinate the entire microcomputer operation.

It accept input and output device depending on the instruction permanent programs stored in ROM or temporary program stored in RAM execute the program and finally result will be displayed through output device.

The CPU chip of the microcomputer is know as microprocessor

# **MEMORY**

- It is a two types of Memory

- RAM Random Access Memory

- ROM Read Only Memory

- RAM is used for temporarily storing the program

- ROM is used for permanently storing the program

## PERIPHERAL DEVICE

The input and output devices called peripheral device. The input device is used to fed the data and the output device is used to display the result

#### **BUSES**

- The input output and memory device are connected to CPU by a group of line is called buses.

- They can be divided into three types

- 1. Address bus

- 2.Data bus

#### 3. Control bus

The address bus carries a address of the memory location or I/O devices that the CPU want to access.

Data bus is used to transfer the data between CPU, memory and I/O device.

Control bus is used to control the signal between CPU, memory and I/O device.

#### INTRODUCTION TO MICROPROCESSOR

The CPU built on a single IC is called microprocessor.

The internal architecture of microprocessor determine how and what operation can be performed with the data. To perform any operation microprocessor requires

- 1. Arithmetic Logic unit

- 2. Control Logic Unit

- 3. Register

- 4. Instruction register

- 5. Program counter

- 6.Internal bus

- 1.ALU is the computational unit of microprocessor which performs arithmetic and logic operation on binary unit

- Register array is the internal storage device

- The control unit is generating the control signal for internal and external operation of microprocessor

- Program counter is used to hold the memory address for the next instruction to be executed

#### ADVANTAGE OF MICROPROCESSOR

- 1.Low cost

- 2.Low size

- 3.Low power consumption

- 4. High reliability

# FEATURES OF 8085

- 8085 is an 8 bit general purpose microprocessor.

- It is a 40 pin dual in line package single chip integrated circuit

- Only one +5V power supply is needed for operation

- It can operate with a 3MHz single phase clock

- It provides Serial Input data and Serial Output Data Line for simple serial interface

- In 8085 microprocessor has the following register

- 1. One 8-bit Accumulator (ACC) register A

- 2. Six 8-bit general purpose register B,C,D,E,H,L

- 3. One 16 bit stack pointer SP

- 4. One 16-bit program counter, PC

- 5. Instruction register

- 6. Temporary register

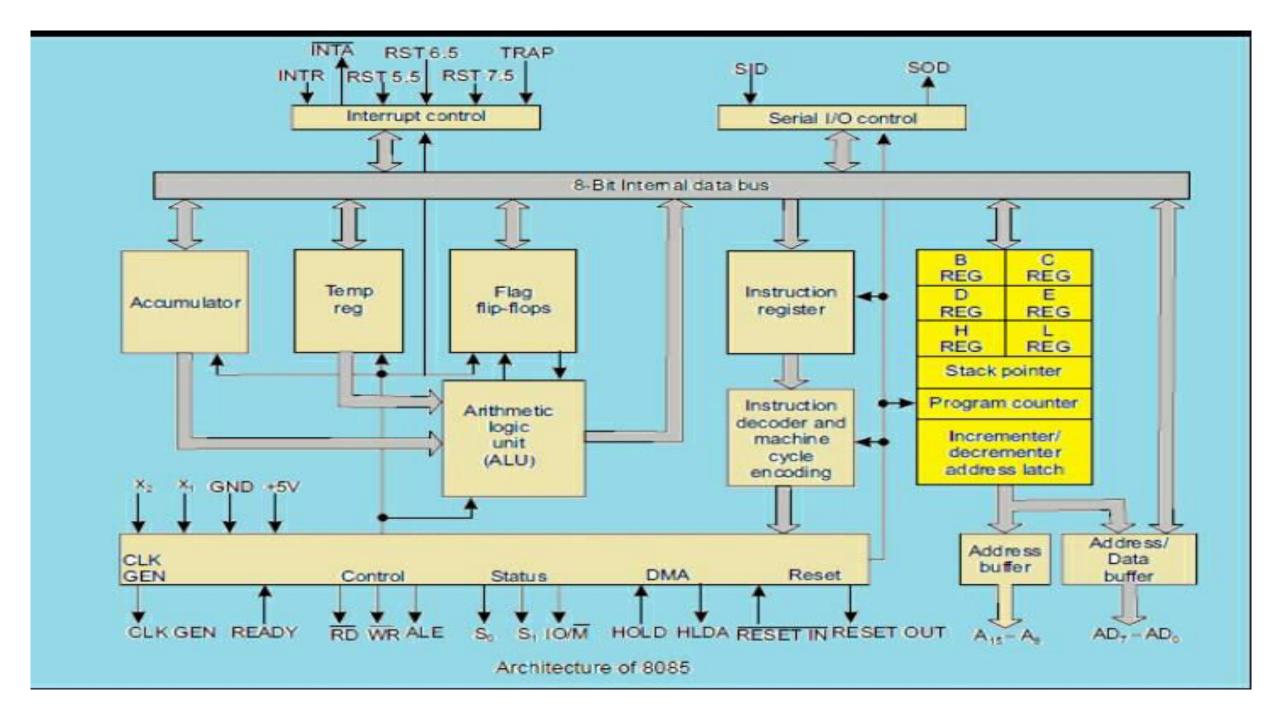

# ARCHITECTURE OF 8085 MICROPROCESSOR

The architecture of 8085 has the following components

- 1. Accumulator

- 2. General Purpose register

- 3. Program Counter

- 4. Stack pointer

- 5. Arithmetic and Logic Unit

- 6. Temporary register

- 7. Flags

- 8. Instruction register and Decoder

- 9. Timing and Control unit

- 10. Interrupt control

- 11. Serial I?O control

- 12. Address buffer and Address Data buffer

- 13. Address bus and data bus

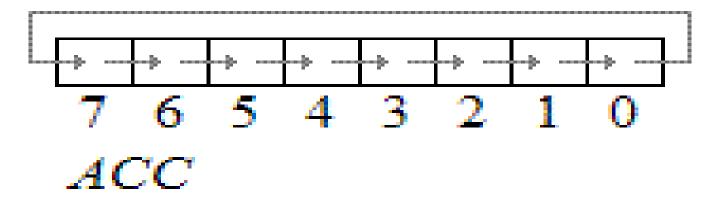

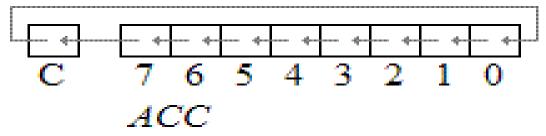

# **ACCUMULATOR**

- Accumulator is an 8-bit register.

- It hold one of the data to be processed by Arithmetic and Logic unit

- It also stores the result of the operation

- The accumulator is also called a A-register

- It is connected to 8\_bit internal data bus

- The bi-directional arrow between the accumulator and the bus.

- It allows the accumulator to send and receive the data

# GENERAL PURPOSE REGISTERS

- The 8085 microprocessor contain six 8 bit general purpose register

- They are B,C,D,E.H,L register

- A combination of two 8 bit registers is a 16 bit data

- The combination og two 8 bit registers is known as register pair

- The register pair in 8085 are B-C,D-E and H-L pair

- H-L pair is act as a memory pointer

# PROGRAM COUNTER(PC)

- It is a 16-bit special-purpose register.

- It is used to hold the memory address of the next instruction to be executed

- The microprocessor increment the content of program counter during the execution of instruction

# **STACK POINTER(SP)**

- It is a 16-bit register

- It is used as a memory pointer

- Stack pointer is decremented each time when data is loaded into the stack and incremented when the data is retrieved from stack

# ARITHMETIC AND LOGIC UNIT(ALU)

- It is a 8- bit register

- ALU carries only the arithmetic and logic operation

- Arithmetic operation such as addituion, subtraction, multiplication, division

- Logic operation such as AND,OR and EXOR.

- ALU results is stored back in the accumulator

# **TEMPORARY REGISTER**

- It is an 8-bit register

- It is associated with ALU

- It hold data during an arithmetic and logical operation

# **FLAG**

- Flag register is a group of five individual flip-flops

- The five status flag of intel 8085 are

- 1.Carry flag (CY)

- 2.Parity flag(P)

- 3. Auxiliary Carry flag(AC)

- 4.Zero flag(Z)

- Sign flag(S)

# INSTRUCTIO REGISTER AND DECODER

- It is a 8-bit register.

- The instruction decoder decodes the content of the instruction register

- During fetch cycle,opcode of an instruction is stored in the instruction register

## TIMING AND CONTROL UNIT

This unit has the following signal

Control signal: READY,RD,WR,ALE

Status signal: S0,S1,IO/N

DMA signal : HOLD

RESET signal: RESET IN RESET OUT

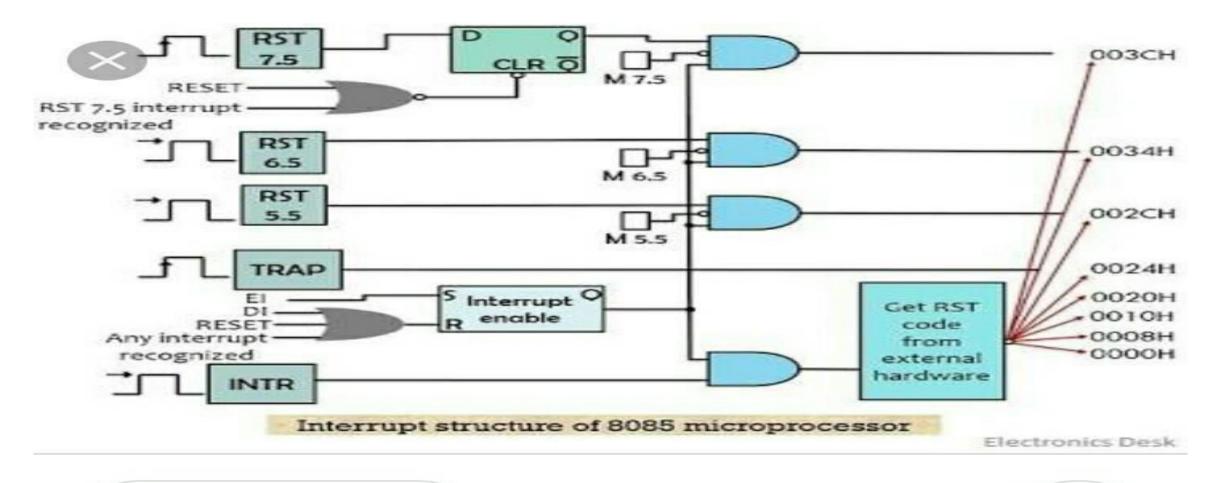

### INTERRUPT

It has two types

1.Maskable

2.Non maskable

Maskable contain contain RST 5.5,6.6,7.5

Non maskable contain TRAP,INTR

SERIAL I/O CONTROL

Serial Input Data

Serial Output Data

The Serial input data enter into the instruction then the Serial Output data can be leave

## ADDRESS BUFFER AND ADDRESS DATA BUFFER

The Stack pointer and program counter can be loaded into the address buffer and address data buffer

The 8-bit internal data bus is also connected to the address data buffer

The bidirectional arrow indicates the three connection that allow address data buffer t send or receive data from 8-bit internal data

# ADDRESS BUS AND DATA BUS

The Intel 8085 requires a 16 bit address.

The 8 most significant bit are address are transmitted by the address bus

The 8 least significant bit are address are transmitted by address data bus

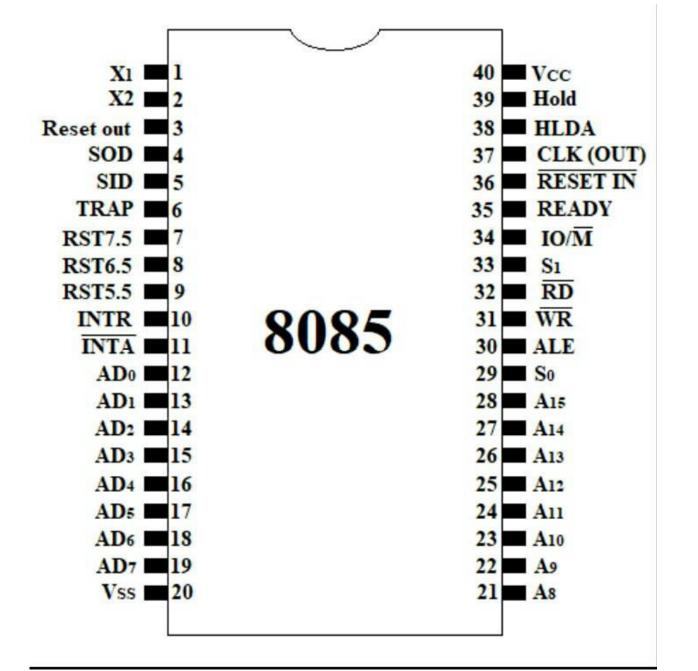

# PIN DIAGRAM OF 8085

The Pin of 8085 can be classified as given below

- 1. Power supply and frequency signal

- 2. Address signals

- 3.Data signals

- 4. Control and status signal

- 5.Interrupts

- 6. Serial I/O signals

- 7. Acknowledgement signals

# Address bus

A8-A15 are address bus and are used for most significant bits of the memory address

# Address/Data buffer

AD0-AD7 are the address /data bus. They are used least significant 8 bits of the memory address

# Address Latch enable (ALE)

It goes High during first clock of a machine cycle and enables the lower 8-bit of the address to be latched

# IO/M

It is a status signal which distinguish whether the address is for memory or I/O.

When it goes high the address on the address bus is for an I/O device.

When it goes low the address on the address bus is for a memory location.

#### WR

This active LOW signal is used to control WRITE operation.

When it goes low, the data on the data bus is written into the selected memory or I/O location.

#### **READY**

It is used by the microprocessor to sense whether a peripheral is ready to transfer data or not.

A peripheral may be connected to the microprocessor through READY line.

If READY is high the peripheral is ready. If it is low the microprocessor waits till it goes high.

#### **HOLD**

It indicates that another device is requesting for the use of the address and data bus.

Having received a HOLD request the microprocessor relinquishes the use of the buses as soon as the current machine cycle is completed

#### **HLDA**

If is a signal for HOLD acknowledgement.

It indicates that the HOLD request has been received.

After the removal of a HOLD request the HLDA goes low.

#### **INTR**

It is an interrupt request signal. Among interrupts it has the lowest priority. When it goes high the program counter does not increment its content.

After completing the instruction at hand it attends the interrupting device.

#### **INTA**

It is an interrupt acknowledgement sent by the microprocessor after interrupt (INTR) is received.

# RST 5.5, 6.5, 7.5

RST 7.5, RST 6.5 and RST 5.5 are the restart interrupts. They cause an internal restart to be automatically inserted. Each of them has a programmable mask.

#### **TRAP**

TRAP is the highest priority interrupts it is a non mask able interrupts

| TRAP    | HIGHEST PRIORITY |  |

|---------|------------------|--|

| RST 7.5 |                  |  |

| RST 6.5 | •                |  |

| RST 5.5 | LOWEST PRIORITY  |  |

#### **RESET IN**

It reset the program counter to zero

It also interrupt enable and HLDA flip-flop

#### **RESET OUT**

It indicates that the CPU is being reset.

# X1, X2

These are terminals to be connected to an external crystal oscillator which drives internal circuitry of the microprocessor to produce a suitable clock for the operation of microprocessor.

# **CLK**

It is a clock output for user, which can be used for other digital ICs. Its frequency is same at which processor operates

# **SID**

It is data line for serial input. The data of this line is loaded into the 7th bit of the accumulator when RIM instruction is executed.

# **SOD**

It is a data line for serial output. The 7th bit of the accumulator is output on SOD when SIM instruction is executed

# Vcc

It is +5 Volts supply pin

# Vss

It is a ground pin.

#### **INSTRUCTION SET**

Instruction

An instruction is a binary pattern designed inside a microprocessor to perform a specific

**Function**

Instruction Set

The entire group of instructions, called the instruction set, determines what functions the microprocessor can perform

8085 Instruction Set

The 8085 instructions can be divided into five different groups based on the function the instruction carry out. They are

- 1. Data Transfer Instructions

- 2. Arithmetic Instructions

- 3. Logical Instructions

- 4. Branching Instructions

- 5. Machine Control Instructions

#### **Data Transfer Instructions**

This group of instructions are used for loading data into registers, moving data in between registers and moving data between registers and memory location.

# Examples:

MOV B,D

LDA 4000 H

STA B

MOV M,C

**XCHG**

#### **Arithmetic Instructions**

This group of instructions are used for addition, subtraction, increment or decrement or data in registers or in memory.

Example

ADD M

SUB C

INR M

DCX B

DAA

# **Logical Instructions**

This group of instructions execute the logical operations like AND, OR, XOR or comparing data between registers or between register and memory, rotating or complementing data in registers or memories.

Examples

ANA B

ORA M

RAL

RRc

CPI A5 H

## **Branch Instructions**

The group of instructions perform

Subroutine CALL

Conditional and unconditional JUMP Return and

Restart

Examples

JMP 9000H

JNC LOOP 1

CC LOOP 2

**RET**

RST 0

#### **Machine Control Instructions**

This group of instructions are used for transferring data between stack and the registers exchanging the contents of SP and HL with the stack top moving data to and from I/O ports enabling or disabling or masking interrupts

Examples

PUSH D

**SPHL**

IN 80H

OUT 07H

**RIM**

#### **Data Transfer Instructions**

MOV

Move the content from source to Destination

MOV destination, source

The content of the source register is moved to the destination register. The content of the source register are not altered. If one of the operand is memory location. It is specified by the contents of HL registers

MOV r1,r2  $[r1] \leftarrow [r2]$

MOV r,M  $[r] \leftarrow [[HL]]$

MOV M,r  $[[HL]] \leftarrow [r]$

#### Examples

1. MOV B,A Before execution

After execution

A

В

A

В

MVI

18

Move Immediate 8 bit data

MVI destination, data

The given data is moved to the destination register or memory.

MVI r,data [r] data

MVI M,data [[HL]] data

Example

MVI B,18 H

B 18H ←

18

18

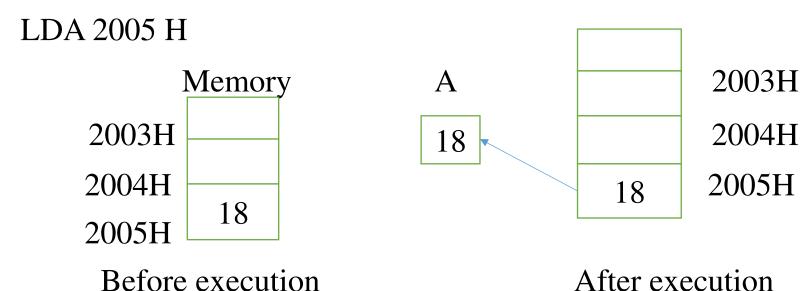

#### **LDA**

Load Accumulator Direct

#### LDA address

The content of the memory location, whose address is specified by the 2nd and 3rd bytes of the instruction is loaded into the accumulator. The contents of the source are not altered.

$[A] \leftarrow [address]$

Examples

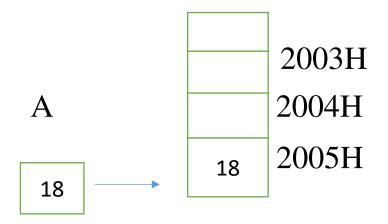

#### **STA**

Store Accumulator Direct

STA address

The contents of the accumulator are stored to a memory location specified by the 2nd and 3rd byte of the instruction.

$[address] \leftarrow [A]$

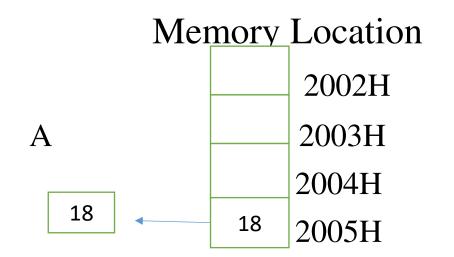

Example

| STA 2005A | Memory     |          |

|-----------|------------|----------|

| A         | 2002H      | 2003H    |

| 18        | 2003H A    | 2004H    |

| 10        | 2004H 18 → | 18 2005H |

|           | 2005H      |          |

Before execution

After execution

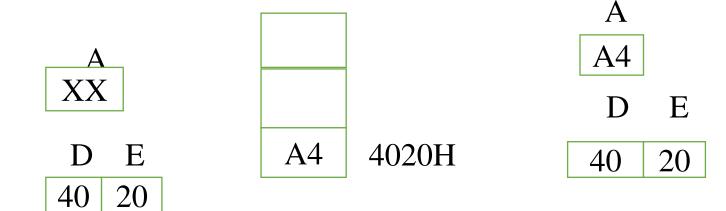

#### LDAX

Load Accumulator Indirect

LDAX register pair

The content of the memory location, whose address is in the register pair (B-C or D-E) is loaded into the accumulator.

$[A] \leftarrow [[rp]]$

Example

LDXA D

Memory

# **STAX**

Stored Accumulator Indirect

STAX register pair

The content of accumulator is stored in the memory location whose address is in the register pair(B-C,D-E)

[[rp]]-[A]

Example

STAX B

#### **LHLD**

Load H and L registers Direct

LHLD address

The content of the memory location, whose address is specified in the instruction, is loaded into register L. The content of next memory location is loaded into register H

$[L] \leftarrow [address]$

$[H] \leftarrow [address+1]$

Example

LHLD 2005H

Before execution

2005 18 2006 F3 2007 After execution

$\frac{H}{F3} \frac{L}{18}$

### **SHLD**

Store H and L registers Direct

SHL

The content of register L is stored in the memory location whose address is specified in the instruction. The content of register H is stored in the next memory location.

$[Address] \leftarrow [L]$

[address+1]  $\leftarrow$ [H]

Example

SHLD 2005 H

Before execution

H L

F0 B3

After execution

Memory

B3 F0 2005 H 2006 H

### LXI

Load Register Pair Immediate

LXI rp, 16 bit data

This instruction loads 16 bit immediate data into the register pair (B-C, D-E, H-L). This is a 3 byte instruction. The second byte specifies the low-order byte and the third byte specifies the high-order byte.

[rh] ←8 MSBs of data

[rl] ←8 LSBs of data

Example

LXIB,1122H

After execution

B C

11 | 12

# **XCHG**

Exchange H and L with D and E

The contents of register H are exchanged with the contents of register D and the contents of register L are exchanged with the contents of register E.

$$[H-L] \leftarrow > [D-E]$$

Example

**XCHG**

Before execution

H I

10 12

D E

30 40

After execution

H L 30 40

D E

10 12

#### **Arithmetic Instruction**

#### **ADD**

Add register or Memory or Accumulator

ADD register

The content of the register or memory is added to the content of the accumulator and the result is stored in the accumulator

$$[A] \leftarrow [A] + [r]$$

Example

ADD B

A A B

33←11+22

# **ADC**

Add Register to Accumulator with Carry

ADC register

The content of the register or memory and the carry flag are added to the content of the accumulator and the result is stored in the accumulator

$$[A] \leftarrow [A] + [r] + [CY]$$

Example

ADC B

# **ADI**

Add Immediate data to accumulator

ADI 8 bit data

The immediate 8 bit data is added to the content of the accumulator and the result is stored in the accumulator

$$[A] \leftarrow [A] + data$$

Example

ADI B2H

A A

$C4 \leftarrow 12 + B2$

### **ACI**

Add Immediate data to accumulator with carry

ACI 8 bit data

The 8 bit data and the carry flag are added to the content of the accumulator and the result is stored in the accumulator

$$[A] \leftarrow [A] + [data] + [CY]$$

Example

ACI 15H

### **DAD**

Add register pair to H-L register

DAD register pair

The 16 bit contents of the specified register pair are added with the content of the H-L register pair and the result is stored in the H-L register

$$[H-L] \leftarrow [H-L] + [rp]$$

Example

DAD B

#### SUB B

Subtract register/memory from Accumulator

Sub register/memory

The content of register or memory location is subtracted from the content of the accumulator

and the result is stored in the accumulator

$$[A] \leftarrow [A] - [r]$$

Example

SUB B

A A B

10**←**20 − 10

### **SBB**

Subtract register/memory and borrow from accumulator

SBB register/memory

The content of register or the memory and the borrow flag are subtracted from the content of the accumulator and the result is stored in the accumulator

$$[A] \leftarrow [A] - [r] - [CY]$$

Example

SBB B

$$[A] \leftarrow [A] - [r] - [CY]$$

A A B CY

$IF \leftarrow 40 - 20 - 01$

# **SUI**

Subtract Immediate Data from accumulator

SUI 8-bit data

The 8-bit data is subtracted from the content of accumulator and the result is stored in the accumulator

$$[A] \leftarrow [A]$$

- data

Example

**SUI 13 H**

A A

05**←**18 - 3

# **SBI**

Subtract Immediate data with Borrow from Accumulator

The 8 bit data and the content of borrow flag (carry flag) are subtracted from the content of the accumulator and the result is stored in the accumulator.

$$[A] \leftarrow [A)$$

—data— $[CY]$

Example:

**SBI 13H**

$$04 \leftarrow 18 - 13 - 01$$

#### **INR**

Increment contents of register/memory by 1

INR register/memory

The content of register or memory location pointed by H-L pair is incremented by 1 and the result is stored in same place

$$[r] \leftarrow [r] + 1$$

Example

INR B

B B

$IC \leftarrow IB + 1$

#### **DCR**

Decrement register/ memory content by 1

Decrement register/memory

The content of the register is decremented by 1 and the result is stored in the same place

$$[r] \leftarrow [r]-1$$

$$[HL] \leftarrow [HL]-1$$

Example

DCR C

$\mathbf{C}$

$A2 \leftarrow A3 - 1$

# INX

Increment register pair by 1

INX rp

The content of register is incremented by 1

$[rp] \leftarrow [rp] + 1$

Example

INX B

B C B C

A1  $04 \leftarrow$  A1 03 +1

# **DCX**

Decrement register pair by 1

DCX rp

The content of register is decremented by 1

$[rp] \leftarrow [rp]-1$

Example

DCX D

D E D E

FF FE ← FF FF -1

# Logical instruction

ANA

Logical AND with accumulator

AND register/memory

The contents of the accumulator are logically anded with the contents of the register or memory and the results is stored in the accumulator.

$[A] \leftarrow [A]^{r}$

$[A] \leftarrow [A]^{[HL]}$

Example

AND B

[A]  $\leftarrow$  0110 0011

$[B] \leftarrow 0100\ 1010$

Result0100 0010 stored in A

### **ANI**

AND immediate data with Accumulator

ANI 8 bit data

The contents of the accumulator are logically anded with the 8-bit data and the results is stored in the accumulator

$[A] \leftarrow [A]^{data}$

Example

**ANI 15 H**

$[A] \leftarrow 0110\ 0011$

Data← 0001 0101

Result **←** 0000 0001 stored in A

### **ORA**

Logically OR with Accumulator

ORA register/memory

The contents of the accumulator are logically ORed with the contents of the register or memory and the results is stored in the accumulator.

$[A] \leftarrow [A]v[r]$

$[A] \leftarrow [A]v[[HL]]$

Example ORA C

$[A] = 1100\ 0011$

$[C] = 0101\ 0101$

Result = 1101 0111 stored in accumulator

# **ORI**

Logically OR Immediate data

ORI 8 bit data

The contents of the accumulator are logically ORed with the 8-bit data and the results is stored in the accumulator

$[A] \rightarrow [A] v data$

Example ORI 71 H

[A] = 0110 1110

Data = 0111 0001

Result = 0111 1111

### **XRA**

Exclusive OR with Accumulator

XRA register/memory

The contents of the accumulator are logically ORed with the contents of the register or memory and the results is stored in the accumulator.

$$[A] \leftarrow [A] \vee [r]$$

$$[A] \leftarrow [A] \vee [[HL]]$$

Example XRA E

$$[A] = 1110 \ 1110$$

$$[E] = 0101\ 1010$$

Result=1011 0100 stored in accumulator

# **XRI**

Exclusive OR immediate with accumulator

XRI 8 bit data

The exclusive ORed 8-bit data with the content of accumulator and the results is stored in the accumulator

$[A] \leftarrow [A] v data$

Example XRI 18 H

$[A] = 1100 \ 0011$

$Data = 0001 \ 1000$

Result =  $1101 \ 1011$

#### **CMA**

Complement Accumulator

The content of accumulator are complemented(1's complement)

$[A] \leftarrow [A]$

Example

**CMA**

Before execution After execution

10011001 01100110

**CMC**

Complement carry

The carry flag is complemented

$[CY] \leftarrow [CY]$

Example CMC

Before execution After execution

CY

1

### **CMP**

Compare with Accumulator

CMP reg/memory

The content of the register or memory is subtracted from the content of the accumulator and the status flag are set according to the result of the subtraction .But the result is not stored . The content of the accumulator remains unchanged.

If

$$[A] < [r] ; CY = 1, Z = 0$$

If

$$[A] = [r]$$

;  $CY = 0$ ,  $Z=1$

Example CMP B

Before execution After execution

A B A B

45 75 45 75

FLG CY=1 Z=0

# **CPI**

Compare Immediate data with Accumulator

CPI 8 bit data

The 8 bit data is compared with the contents of the accumulator. The status flag are set according to the result of subtraction. But the result is discarded

[A]- data

Example

**CPI 45 H**

**STC**

Set Carry

The carry flag is set to 1

[CY]**←**1

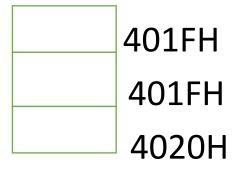

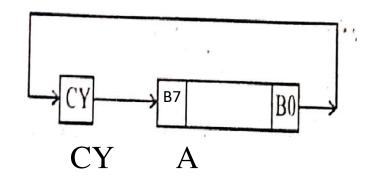

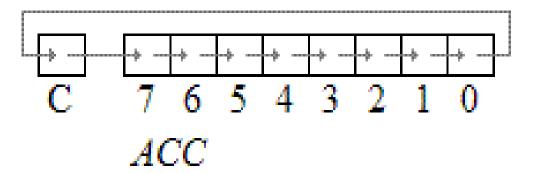

#### RLC

Rotate Accumulator Left

The content of the accumulator is rotated left by one bit. The seventh bit of the accumulator is moved to carry bit as well as to the zero bit of the accumulator

Before execution: 0 10001011

CY A

After execution : 1 00010111

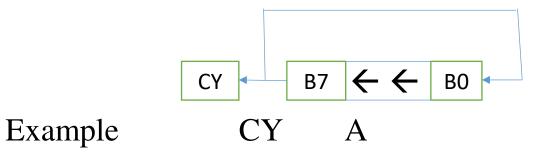

# **RRC**

Example

Rotate Accumulator Right

The content of the accumulator is rotated right by one bit. The zero bit of the accumulator (B0) is moved to the seventh bit (B7) as well as to carry bit.

Before execution: 10100111

CY A

After execution : 11010011

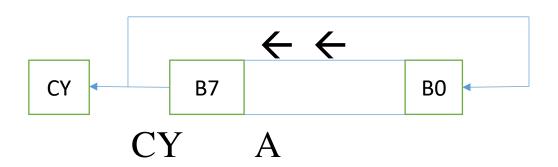

#### RAL

Rotate Accumulator Left through carry

The content of the accumulator is rotated left one bit through carry. The seventh bit of the accumulator (B7) is moved to carry and the carry bit is moved to the zero bit (B0) of the

Accumulator

Example CY A

Before execution: 11100001

CY A

After execution : 11000010

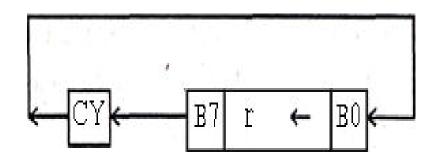

#### **RAR**

Rotate Accumulator Right through carry

The content of the accumulator is rotated right one bit through carry. The zero bit of the accumulator (B0) is moved to carry and the carry bit is moved to the seventh bit (B7) of the Accumulator

Example

Before execution: 0 00011100

CY A

After execution : 0 00001110

# **Branch Instruction**

# **JMP**

# (i) Jump Unconditionally

JMP 16-bit address

2<sup>nd</sup> byte and 3<sup>rd</sup> byte of the instruction give the address of the label where the program jumps. The address of the label is the address of the memory location of next instruction to be executed. The program jumps to the instruction specified by the address unconditionally [PC]←Label

Example

JMP 4000H

# (i)Jump conditionally

After the execution of the condition jump instruction the program jumps to the instruction specified by the address(Label) if the specified condition is fulfilled.Otherwise the program proceeds further in the normal sequence

| Instruction | Operation           |

|-------------|---------------------|

| JC          | Jump on carry       |

| JNC         | Jump on No carry    |

| JP          | Jump on positive    |

| JM          | Jump on Minus       |

| JPE         | Jump on Parity Even |

| JPO         | Jump on Parity Odd  |

| JZ          | Jump on zero        |

| JNZ         | Jump on No zero     |

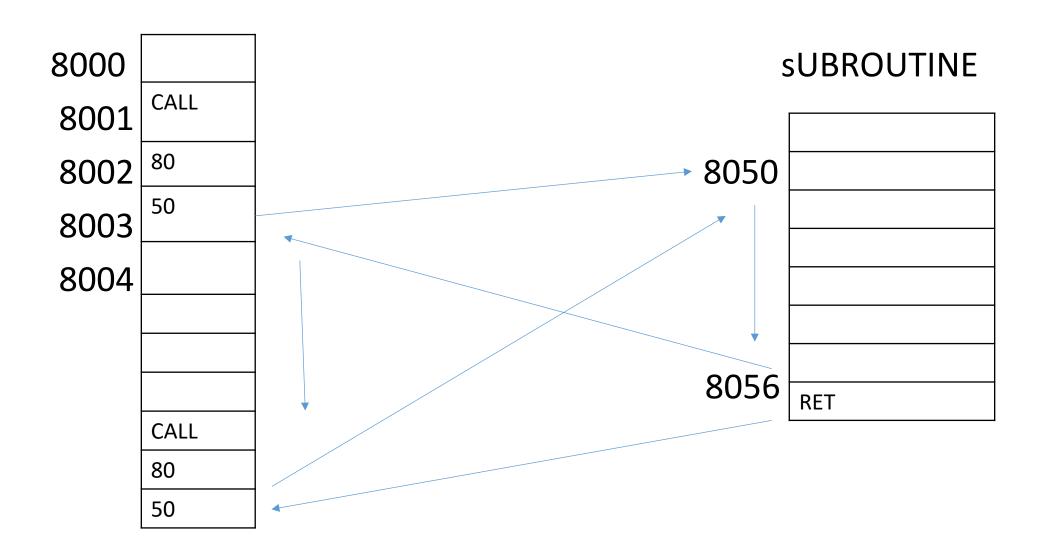

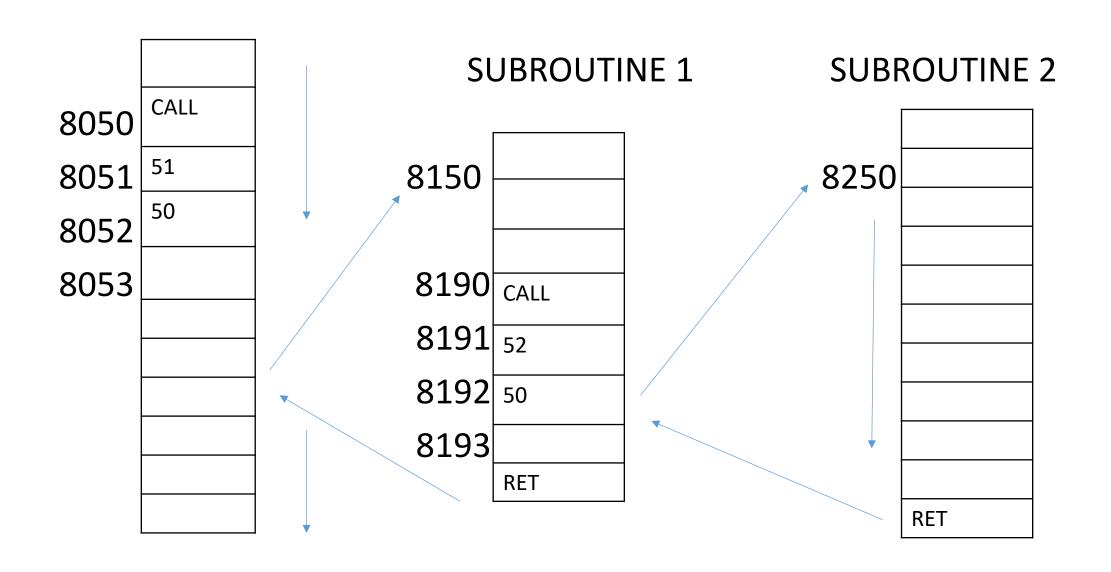

#### **CALL**

i) Unconditional Subroutine Call

CALL 16-bit address

CALL instruction is used to call a subroutine. Before the control is transferred to the subroutine the address of the next instruction of the main program is saved in the stack. The content of SP is decremented by 2 to indicate the new stack top.

$[[SP]-1] \leftarrow PCH$

[[SP]-2]←PCL

$[SP] \leftarrow [SP]-2$

[PC] ←Label (address)

Example

**CALL 5000H**

# ii)Conditional Subroutine call

| Instruction | Operation           |

|-------------|---------------------|

| CC          | Call on carry       |

| CNC         | Call on No carry    |

| CP          | Call on Positive    |

| CM          | Call on Minus       |

| CPE         | Call on Parity even |

| CPO         | Call on Parity Odd  |

| CZ          | Call on zero        |

| CNZ         | Call on non zero    |

#### RET

i) Return from subroutine Unconditionally

RET is used at the end of subroutine. Before the execution of subroutine the address of the next instruction of the main program saved the main program is saved in the stack. The content of SP is incremented by 2 to indicate the new stack top.

PCL  $\leftarrow$ SP PCH  $\leftarrow$ [[SP]+1] [SP]  $\leftarrow$ [SP]+2

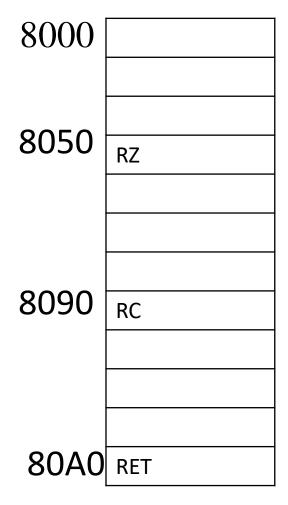

# ii) Conditional return

| Instruction | Operation             |

|-------------|-----------------------|

| RC          | Return on carry       |

| RNC         | Return on No carry    |

| RP          | Return on Positive    |

| RM          | Return on Minus       |

| RPE         | Return on Parity even |

| RPO         | Return on Parity Odd  |

| RZ          | Return on zero        |

| RNZ         | Return on non zero    |

**RST**

#### Restart

Restart is a one-word CALL instruction. The content *of* PC is saved in the stack. The Program jumps to the instruction starting at restart location

| Instruction | Restart Locations (Hex) |

|-------------|-------------------------|

| R8T0        | 0000                    |

| RST1        | 0008                    |

| RST2        | 0010                    |

| RST3        | 0018                    |

| RST4        | 0020                    |

| RST5        | 0028                    |

| RST6        | 0030                    |

| RST7        | 0038                    |

#### **PCHL**

Load PC with HL contents

The contents of registers H and L are copied into the program counter. The contents of H are placed as a high order byte and the contents of L are placed as a low order byte.

$[PCH] \leftarrow [H]$

$[PCL] \leftarrow [L]$

Stack, I/O and Machine Control Instructions

#### IN

Input Data to Accumulator from a Port

IN 8-bil Port address

The contents of the input port specified in, the operand are read and loaded into the accumulator.

$[A] \leftarrow [Port]$

Example IN 80 H

#### **OUT**

Output Data from Accumulator to a Port

**OUT 8-bit Port address**

The contents of the accumulator are copied into the output port specified by the operand.

$[Port] \leftarrow [A]$

Example :OUT 30 H

#### **PUSH**

Push Register pair onto stack

PUSH rp

The contents of the register pair are pushed into the stack. The SP is decremented and the contents of the high order register (B, D, H, A) are copied into that location. The SP is decremented again and the contents of the low order register (C, E, L) are copied to that location.

Defense execution

| Before execution | After execution | Stack   |

|------------------|-----------------|---------|

| ВС               | ВС              | 2097    |

| 23 45            | 23 45           | 45 2098 |

| SP               | SP              | 23 2099 |

| ~1               | Sr              | XX 2099 |

| 20992097         |                 |         |

#### **POP**

## POP OF Stack to Register Pair

The contents of the memory location pointed out by the SP are copied to low-ords register (C. E. L) of the operand. The SP is incremented by 1 and the contents of that memor location are copied to high-order register (A, B, D, H) of the operand. The SP is again incremented by 1.

[rL]←[SP] [rH]←[[SP]+1] [SP]←[SP]+2

Example POP H

| Before execution | After execution | Stack               |

|------------------|-----------------|---------------------|

| H L              | H L             | 2090H               |

| XX XX            | 18 5A           | <sup>5A</sup> 2091H |

| SP               | SP              | <sup>18</sup> 2092H |

| 2090             | 2092            |                     |

HLT

Halt

The execution of the instruction HLT stops the microprocessor. The MPU finishes executing the current instruction and halts any further execution. The registers and Status flags remain unaffected.

#### **XTHL**

Exchange H and L with Stack TOP

The content of register L are exchanged with the byte of the stack top. The content of register H are exchanged with the byte below the Stack top

$$[L] \leftarrow [SP]$$

$$[H] \leftarrow [SP]+1]$$

Before execution After execution

H I

11 22

Stack

3000 33 3001 H L

33 44

Stack

3000

11 | 3001

#### **SPHL**

Copy H and L to the SP

The contents of HL pair are transferred to the stack pointer register.

$[SP] \leftarrow [HL]$

EI

**Enable Interrupts**

When this instruction is executed, the interrupts are enabled.

#### $\mathbf{DI}$

Disable Interrupts

When this instruction is executed, the interrupts are disabled.

#### **NOP**

NO operation

When this instruction is executed, no operation is performed. The register and flags remain unaffected. The instruction is used to fill in time delays or to delete or insert instruction with trouble shooting

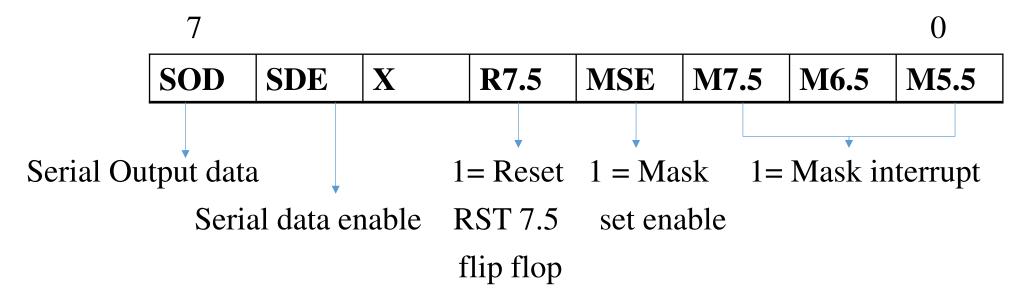

#### SIM

Set Interrupt Mask

SIM is a multipurpose instruction and used to implement the 8083 interrupts (RST 7.3,6.5 and S.5) 2nd serial data output. Time instruction interprets the accumulator contents as follows:

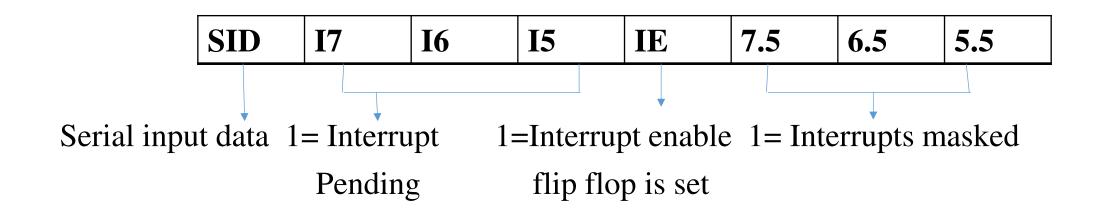

#### **RIM**

Read Interrupt Mask

RIM is a multipurpose instruction used to real the status of interrupts (RST 7.5,6.5 and 5.5) and to read serial data input bit. The instruction interprets the accumulator contents, as follows:

#### **ADDRESSING MODES**

- Every instruction of a program has to operate on a data. The method of specifying the data to be operated by the instruction is called Addressing.

- Addressing mode is the way the microprocessor identifies the operands for the instruction.

- The 8085 has the following addressing modes.

- Immediate addressing mode

- Direct addressing mode

- Register addressing mode

- Register indirect addressing mode

- Implicit addressing mode

### **Immediate Addressing Mode**

In immediate addressing mode, the data (Operand) is specified within the instruction itself.

### Examples:

MVI A, 18 H

ADI 09 H LXI H, 50AB H MVI A, 18 M

Accumulator

18 ----

Move the data 18H to the Accumulator

### **Direct Addressing Mode**

In direct addressing mode, the address of the data (operand) is specified in the instruction itself.

Examples:

STA 2005 H

**OUT 05 H**

LDA 4100 H

#### STA 2005 H

Memory Location

Store the content of the accumulator in the memory location 2005 H. 2005 H is it memory address where the data is to be stored. It is given in the instruction itself.

### **Register Addressing Mode**

In register addressing mode, the instruction specifies the name of the register in which the data is available.

The opcode specifies the address of the register in addition to the, operation to be performed.

Examples

MOV A, B

ANA B

SUB H

MOV A,B

A B

Move the content of register B to A

### **Register Indirect Addressing Mode**

In register addressing mode, the instruction specifies the name of the register in which the data is available.

Examples

MOV A, M

SUB M

DCR M

MOV A,M

# **Implicit addressing Mode**

Some instruction operate on the content of the accumulator. Such instruction do not requires the address of operand.

Example

**CMA**

RAL

RAR

# 8085 Addressing mode

Type Instruction

Direct STA 2005H

Register MOV A,B

Register Indirect MOV A,M

Immediate MVIA,18H

Implicit CMA

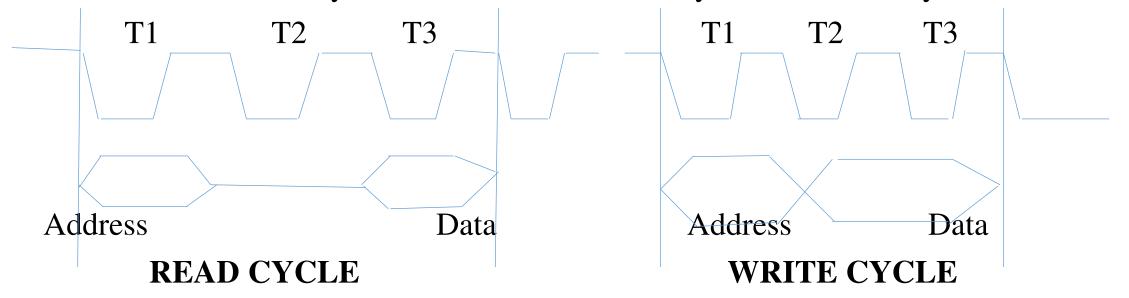

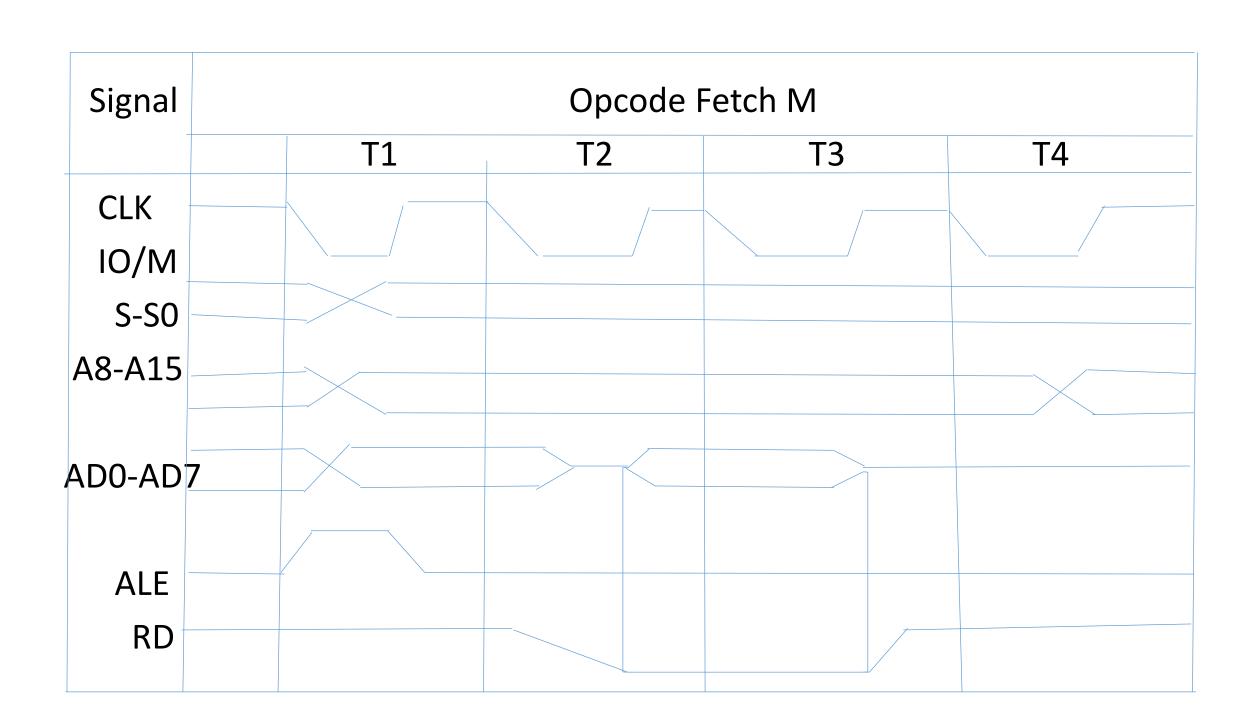

### **Timing diagram**

The timing diagram provides the information about the various condition of the signal in which the machine cycle is executed

The timing diagram matches the peripheral devices like memories, ports etc.. Can be selected to form a system with microprocessor as CPU

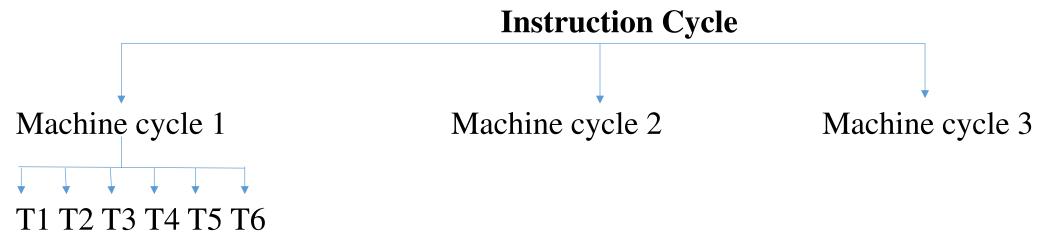

### **Instruction cycle**

It is defined as the time required to complete the execution of an instruction.

The 8085 instruction cycle consist of one to six machine cycles.

## Machine cycle

It is defined as the time required to complete one operation of accessing memory, I/O or acknowledgement an external request. This cycle may consist of 3 to 6 T-states

#### **T-state**

It is defined as one subdivision of the operation performed in one clock period

These subdivision are internal state synchronized with system clock.

One T – state – One clock period

Each instruction of the 8085 microprocessor can be divided into a few basic operation called machine cycle and each machine cycle can be divided into T-states

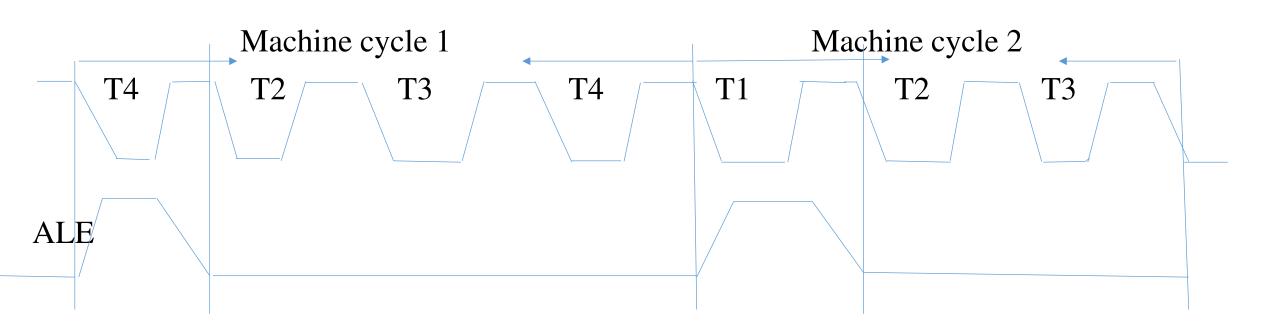

### **ALE(Address Latch Enable)**

This signal is high active signal. It is activated in the beginning of the T1 state of each machine cycle, except bus idle machine cycle, and it remains active in the T1 state

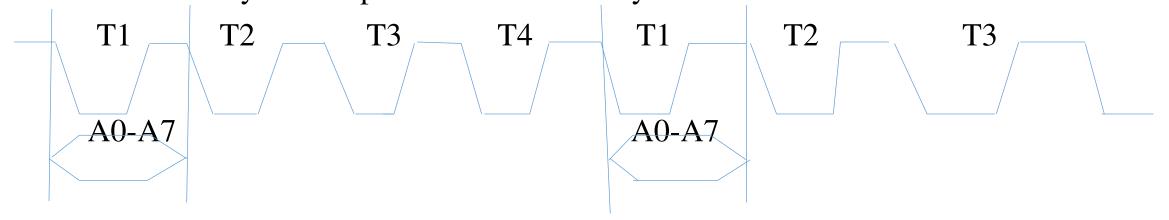

### A0-A7(Lower byte address)

The lower byte of address is available on the multiplexed addressed / data bus during T1 state of each machine cycle except bus idle machine cycle

#### D4-D7(Data bus)

The data from memory or I/O device and from microprocessor to memory or I/O device is transferred during T2 and T3 states.

It is important to note that in read machine cycle, data will appear on the data bus during the later part of the T2-state whereas in write cycle data will appear on the data bus at the beginning of the T2-state

To read data from memory or I/O device it is necessary to select memory or I/O device

#### **A8-A15**

The higher byte of address is available on A8-A15 bus during T1,T2 and T3 states of each machine cycle , except bus idle machine cycle

### **During T2 state**

At the beginning of T2 states the microprocessor sends the control signal RD goes low to enable memory

The data which is opcode D0-D7 of the selected memory location are placed on A/D bus

### **During T3 state**

The opcode of A/D bus is transferred to the instruction register

The RD is high thus disabling the memory from A/D bus

### **During T4 state**

The fetched opcode is decoded

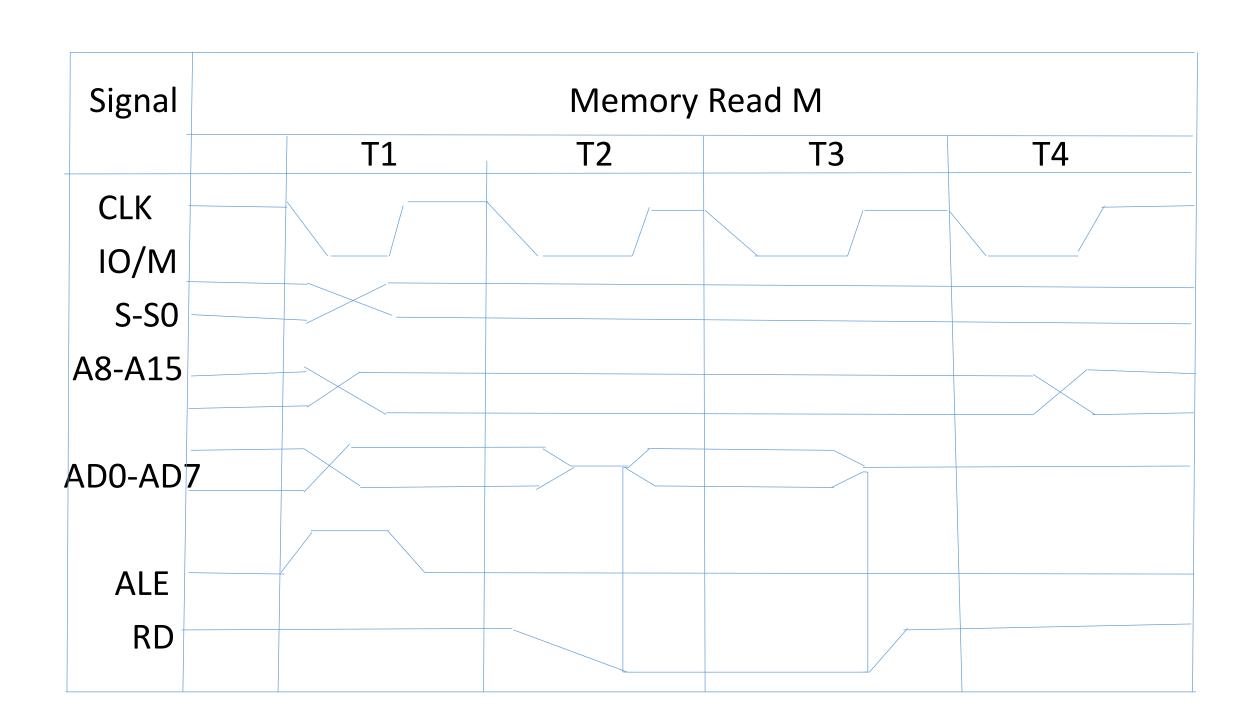

### **Memory Read Machine cycle**

If instruction is one bit in length opcode fetch cycle only one machine cycle is required for completion

When the instruction is more than one byte to transfer the operand from memory or I/O device may require a few more machine cycle

Usually these cycles have 3 states

For example

MVI D,18H

This instruction is a memory read cycle which consist of two machine cycle.

First machine cycle is to fetch the opcode and the second machine cycle is the memory read machine cycle which transfer the operand – 18 H from memory

### **During T1 state**

The content of program counter is placed on Address or Address / Data bus

- The ALE signal goes high and at middle of T1 ALE goes low

- The microprocessor recognizes the memory read machine cycle by the status signal For memory read cycle IO/M=0 S1=1,S0=0

#### **During T2 state**

The content of (D0-D7) of selected memory location are placed on the A/D bus

### **During T3 state**

The data loaded on the A/D bus is moved to microprocessor

In the middle of the T3 state RD goes high and disables the memory read operation

### I/O Read Machine Cycle

It is similar with read operation

For example IN 80 H

It is a two byte I/O read instruction

The first machine cycle is opcode and fetch and the second is I/O read machine cycle is used where content of the port address is transferred to the microprocessor. The status information for I/O read is IO/M = 1,S1=0,S0=0

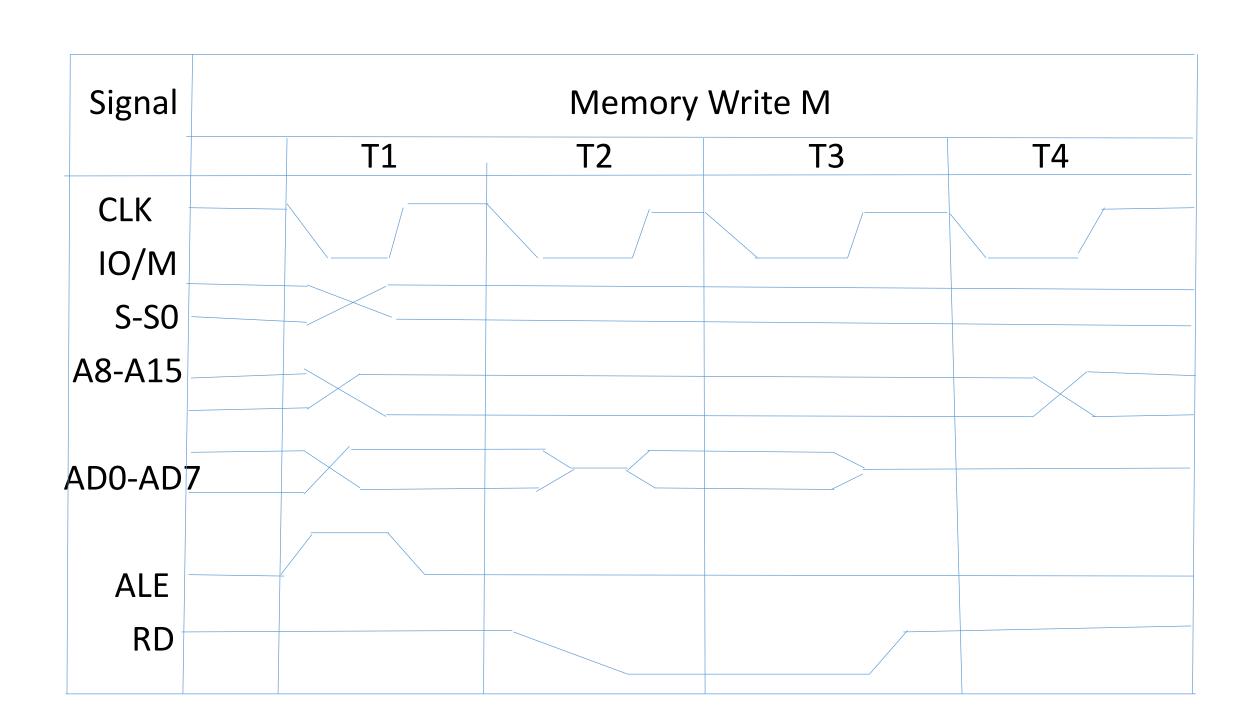

### Memory write machine cycle

A memory write or I/O write cycle is used for sending data from one of the microprocessor register to the memory or I/O device

For example

MOV M,A

This requires two machine cycle

The first is opcode fetch machine cycle. The second is the write machine cycle used for

Transferring the content of accumulator to the memory location.

### **During T1 state**

- The microprocessor place 16-bit address of the memory location on the address or Address / data buffer

- The ALE goes high and at the middle of T1 state it goes low which is used to latch the address bit in the memory

- The microprocessor recognizes the memory write machine cycle, from the status signal For the memory write machine cycle IO/M = 0, S1=0,S0=1

#### **During T2 state**

At the beginning of T2 state WR goes low to enable write operation In this state the content of the register C is placed on data bus

### **During T3 state**

The data on the data bus is transferred to the specific memory location In the middle of T3 state the control signal WR goes high and disable the memory

I/O Write Machine cycle

It is similar with memory write operation

Example OUT 03 H

The I/O write machine cycle is used for sending data from accumulator to the output device whose address is 03H

The microprocessor recognize the machine cycle from thee status signal . For I/O write machine cycle IO/M =1 , S1=0, S0=1

### **INTA Machine cycle**

When microprocessor is executing a program it checks the INTR line during execution of each instruction.

If INTR is high the microprocessor completes the current instruction and send a signal INTA.

### **Bus Idle Machine cycle**

It is a machine cycle during which data bus of the microprocessor is not used . It is in idle state

During bus idle machine cycle

READY line is not sampled by the microprocessor

No memory or I/O device is communicating with the microprocessor

No WAIT cycle are possible

The data bus is not used it is tri stated

#### **INTERRUPTS**

The process of interrupting the normal program execution to carry out a specific task / work is referred to as interrupt

The microprocessor can be interrupted

- 1. By an external signal generated by peripheral

- 2. By an internal signal generated by instruction

- 3. By an internal signal generated due to an exceptional condition which occurs while

- 4. executing an instruction.

When microprocessor receives an interrupt signal it stops executing the main program, uses the status of all registers in stack then processor executes the interrupt service routine (ISR) in order to perform the specific work requested by the interrupt.

### **Classification of interrupts**

#### **Interrupts** Maskable Hardware Software Vectored Non-vectored Non-maskable TRAP **TRAP** RST 0 **TRAP INTR RST 5.5 RST 5.5** RST 1 **RST 5.5 RST 6.5 RST 6.5** RST 2 **RST 7.5 RST 6.5** RST 3 **RST 7.5 RST 7.5 INTR** RST 4 RST 5 RST 6 RST 7

#### **Interrupt Vectored Table**

- It is not possible to give each interrupt Service Routine (ISR) a fixed slot in the memory since the different routines may be of different size.

- When an interrupt occurs the control does not go to the ISR directly.

- Instead a CALL instruction to a predetermined location on the 00 page of the memory is executed.

### **Software Interrupt**

- The syntax for software interrupt instruction is RST n

- When n range from 0 to 7 (RST1,RST2...)

- These are single byte instruction and the Hex code with the address in the Vectored Interrupt table

| <b>Instruction Op-code</b> | Hex code in Hex | Vector address |

|----------------------------|-----------------|----------------|

| RST0                       | C7              | 0000           |

| RST1                       | CF              | 0008           |

| RST2                       | D7              | 0010           |

| RST3                       | DF              | 0018           |

| RST4                       | E7              | 0020           |

| RST5                       | EF              | 0028           |

| RST 6                      | F7              | 0030           |

| RST 7                      | FF              | 0038           |

When any of these instruction are executed a CALL to the specified address is executed.

The content of the program counter is saved in stack memory.

Vector address of the instruction are spaced by 8 byte.

Usually 3 byte JMP instruction to the corresponding ISR is stored

### **Hardware Interrupts**

The 8085 CPU has 5 hardware interrupts

| Interrupt | Vector address |

|-----------|----------------|

| TRAP      | 0024           |

| RST 5.5   | 002C           |

| RST 6.5   | 0034           |

| RST 7.5   | 003C           |

| INTR      | -              |

The space between RST 5 (software interrupt) and RST 5.5 (hardware interrupt) is only 4 byte

The predetermined addresses of the hardware interrupts are in the first page of if memory area.

Note that the vector addresses of the hardware interrupt are spaced only 8 bytes

## **Vectored and Non-Vectored Interrupts**

The first 4 hardware interrupt signals (TRAP, RST5.5, RST6.5, RST7.5) are di rect ly vectored to the address specified in the interrupt vector table

They are also called **vectored interrupts.**

However the interrupt request INTR is handled slightly in different way

When INTR interrupt is activated the CPU produce an Interrupt Acknowledgement INTA signal

INTR is called **non vectored interrupt**

#### **Maskable and Non-maskable Interrupts**

- The hardware interrupts can be classified as maskable and nonmaskable interrupts.

- Except TRAP, the others are maskable interrupts.

- TRAP is a non maskable interrupt.

- The maskable interrupts may be enabled and disabled by software instructions.

- When they are disabled the CPU ignores them when they occur.

### **Priority interrupts**

- When a hardware interrupt is activated it is sensed only after completing the present cycle.

- If more than one interrupt are actuated at the same time, they are serviced basis.

- TRAP has the highest priority.

- It is always serviced first then RST 7.5, then RST 6.5 and finally RST 5.5.

- At the end of every instruction cycle, internally, the interrupt are scanned in priority

- TRAP Highest Priority

- RST 7.5

- RST 6.5

- RST 5.5

- INTR Lowest Priority

## **Interrupt Service Sequence**

- A hardy are interrupt occurs or a RST n instruction is encountered in the program.

- CPU completes the execution of the current instruction and scans the interrupt lines.

- If there is any interrupt, the contents of program counter is stored in the stack memory

- The CPU sends out an INTA signal (for hardware interrupt only) C PU branches to the vector table location.

- Execute JMP to specified ISR

- Carriers out ISR

- When RET instruction is encountered the CPU loads the return address the stack into the program counter and returns to the main program

# Working of Interrupt Control TRAP

Trap being non-maskable it used to handle the very important function

In general it is used to take care of sudden power failures. It may execute a routine to

transfer the content of the main memory to the back up memory.

It is edge and level sensitive which means input has to go high

The rising edge triggers the D flip-flop

The D flip-flop and the AND output triggers the TRAP input.

The TRAP is cleared by

The RESET signal or

Internal TRAP Acknowledgement signal

As soon as Internal TRAP Acknowledgement signal will reset the D-flipflop

#### RST 7.5,6.5,5.5

RST 7.5 is edge sensitive. The D-flipflop is actuated by the rising edge and its output become high.

The RST 7.5 interrupt is cleared by internal RST 7.5 interrupt

RST 6.5 and RST 5.5 are level sensitive interrupt

#### **MEMORY ORGANIZATION**

A Memory unit is an integral part of any microcomputer and its primary purpose is to hold the instructions and data

The major design goal of a memory unit is it allow it to operate at a speed close to that of microprocessor.

The cost of a memory unit is prohibitive and practically it is not feasible to design large memory unit with one technology.

The memory system is usually designed with different technologies such as solid state, magnetic and optical

The memory system can be divided into three groups

Microprocessor memory

Primary or main memory

Secondary memory

#### **Microprocessor memory**

It comprises a set of microprocessor register. The registers are used to hold temporary memory .

There is no speed between the register and microprocessor

## Main memory

It is the storage area in which all the program are executed.

Primary memory is the computer memory that is accessed directly by the CPU

These are several types of memory such as processor cache and system ROM

Primary memory is also called as primary storage

- The primary storage may also refer to internal storage device like internal hard drives.

- The operating system and applications are loaded into primary memory since RAM can be accessed much faster than storage device.

- The data can be transferred between CPU and RAM.

#### **Secondary memory**

- It refers to storage device like hard drives and solid state

- It also refers to removable storage such as USB flash drives, Ds and DVD

- Unlike primary memory, secondary memory is not accessed directly by CPU

- RAM plays an important role it provides fast data to access the speed

- Secondary memory is slower than primary memory

- Secondary memory is to store permanent data

# 19MZC12&19RAC12 / MICROPROCESSOR AND APPLICATIONS

## Prepared by

Mr.C.RAMKUMAR,

Assistant Professor,

Department of Electrical and Electronics Engineering, Muthayammal Engineering College (Autonomous), Rasipuram – 637 408.

# Unit – II 8051 Microcontroller

#### Microcontroller

- 1. 8051Microcontroller is an 8-bit microcontroller created in 1981. It is most popular and commonly used microcontroller.

- 2. An 8-bit microcontroller has an 8-bit data bus and 16-bit address bus.

- 3. It is an integrated chip designed under very large scale integration techniques.

- 4. It consist of a processor with other peripheral devices like memory, I/O ports and timer. A microcontroller contain all these component in a single chip

- 5. A microcontroller does not require much additional interfacing ICs for operation and it functions

- 6. A microcontroller clock speed is limited only to a few tens of MHz

# **Classification of microcontrollers**

| Intel 4004           | 4 bit (2300 PMOS trans, 108 kHz) | 1971 |

|----------------------|----------------------------------|------|

| Intel 8048           | 8 bit                            | 1976 |

| Intel 8031           | 8 bit (ROM-less)                 | •    |

| Intel 8051           | 8 bit (Mask ROM)                 | 1980 |

| Microchip PIC16C64   | 8 bit                            | 1985 |

| Motorola 68HC11      | 8 bit (on chip ADC)              | •    |

| Intel 80C196         | 16 bit                           | 1982 |

| Atmel AT89C51        | 8 bit (Flash memory)             | •    |

| Microchip PIC 16F877 | 8 bit (Flash memory + ADC)       | •    |

#### Various features of 8051 microcontroller

- 8-bit CPU

- 16-bit Program Counter

- 8-bit Processor Status Word (PSW)

- 8-bit Stack Pointer

- Internal RAM of 128bytes

- Special Function Registers (SFRs) of 128 bytes

- 32 I/O pins arranged as four 8-bit ports (P0 P3)

- Two 16-bit timer/counters: T0 and T1

- Two external and three internal vectored interrupts

- One full duplex serial I/O

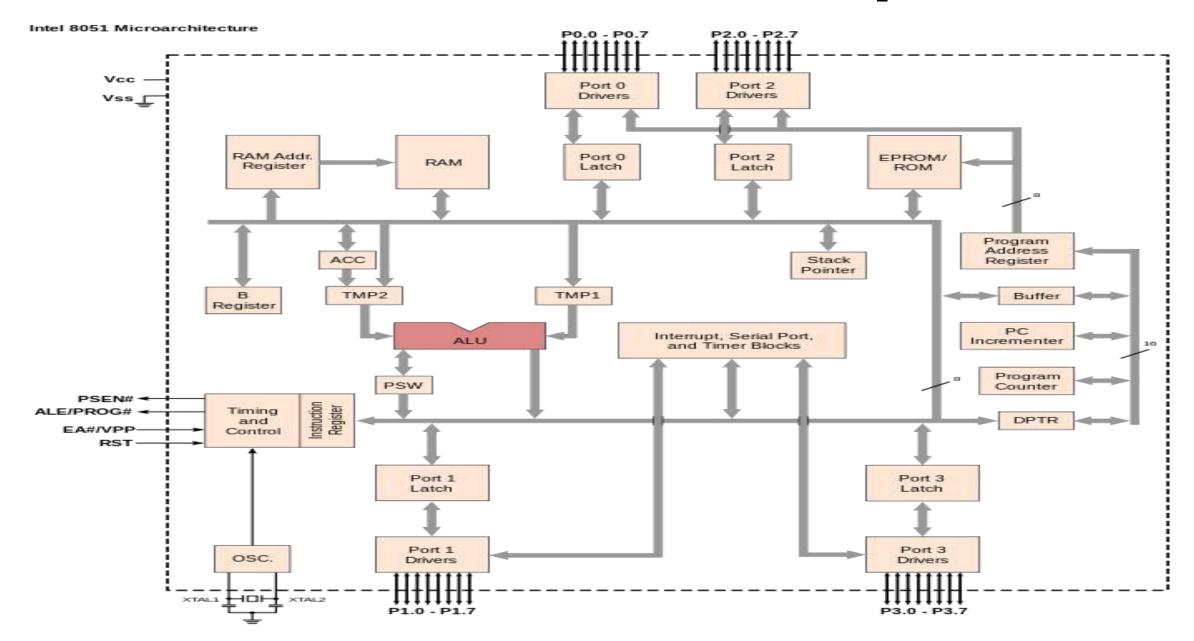

# **ARCHITECTURE OF 8051 MICROCONTROLLER:**

#### **ALU:**

- It is 8 bit unit

- It performs arithmetic operation as addition, subtraction, multiplication, division, increment and decrement.

- It performs logical operations like AND, OR and EX-OR. It manipulates 8 bit and 16 bit data

- It calculates address of jump locations in relative branch instruction.

- It performs compare, rotate and compliment operations

- 8051 micro controller contains 34 general purpose registers or working registers

## **Accumulator**(**A-reg**):

It is 8 bit register

It is bit and byte accessible

Result of arithmetic & logic operations performed by ALU is accumulated by this register.

- Therefore it is called accumulator register

- It is used to store 8 bit data and to hold one of operand of ALU units during arithmetical and logical operations

- Most of the instructions are carried out on accumulator data.

#### **B-register**

- It is special 8 bit math register. It is bit and byte accessible.

- It is used in conjunction with A register as I/P operand for ALU. It is used as general purpose register to store 8 bit data.

#### **PSW**

- It is 8 bit register.

- Its address is D0H and It is bit and byte accessible.

- It has 4 conditional flags or math flags which sets or resets according to condition of result.

It has 3 control flags, by setting or resetting bit required operation or function can be achieved.

#### FLAG:

Carry Flag(CY): During addition and subtraction any carry or borrow is generated then carry flag is set otherwise carry flag resets.

It is used in arithmetic, logical, jump, rotate and Boolean operations.

**Auxiliary carry flag(AC):** If during addition and subtraction any carry or borrow is generated from lower 4 bit to higher 4 bit then AC sets else it resets.

It is used in BCD arithmetic operations.

Overflow flag(OV): If in signed arithmetic operations result exceeds more than 7 bit than OV flag sets else resets.

It is used in signed arithmetic operations only.

**Parity flag(P):** If in result, even no. Of ones "1" are present than it is called even parity and parity flag sets.

In result odd no. Of ones "1" are present than it is called odd parity and parity flag resets.

#### **CONTROL FLAGS:**

**FO:** It is user defined flag. The user defines the function of this flag. The user can set test and clear this flag through software.

**RS1 and RS0:** These flags are used to select bank of register by resetting those flags **Program counter (PC):**

The Program Counter (PC) is a 2-byte address which tells the 8051 where the next instruction to execute is found in memory.

It is used to hold 16 bit address of internal RAM, external RAM or external ROM locations.

It is important to note that PC isn't always incremented by one and never decremented.

**Data pointer register (DTPR):** It is a 16-bit register used to hold address of external or internal RAM where data is stored or result is to be stored.

It is used to store 16 bit data.

Each register can be used as general purpose register to store 8 bit data and can also be used as memory location.

DPTR does not have single internal address.

It functions as Base register in base relative addressing mode and in-direct jump.

#### **Stack pointer (SP):**

It is 8-bit register. It is byte addressable.

Its address is 81H.

It is used to hold the internal RAM memory location addresses which are used as stack memory.

When the data is to be placed on stack by push instruction, the content of stack pointer is incremented by 1, and when data is retrieved from stack, content of stack of stack pointer is decremented by 1.

## **Special function Registers(SFR):**

The 8051 microcontroller has 11 SFR divided in 4 groups:

## **Timer/Counter register**

8051 microcontroller has 2-16 bit Timer/counter registers called Timer-reg-T0 And Timer/counter Reg-T1.

Each register is 16 bit register divide into lower and higher byte register

These register are used to hold initial no. of count.

All of the 4 register are byte addressable.

## Timer control register

8051 microcontroller has two 8-bit timer control register i.e. TMOD and TCON register.

## **TMOD Register:**

It is 8-bit register.

Its address is 89H.

It is byte addressable.

It used to select mode and control operation of time by writing control word.

## **TCON register:**

It is 8-bit register. Its address is 88H.

It is byte addressable.

Its MSB 4- bit are used to control operation of timer/ counter and LSB 4-bit are used for external interrupt control.

## Serial data register:

8051 micro controller has 2 serial data register viz. SBUF and SCON.

#### Serial buffer register (SBUF):

It is 8-bit register.

It is byte addressable.

Its address is 99H.

It is used to hold data which is to be transferred serially.

## **Serial control register (SCON):**

It is 8-bit register.

It is bit/byte addressable.

Its address is 98H.

The 8-bit loaded into this register controls the operation of serial communication.

Interrupt register: 8051 µC has 2 8-bit interrupt register.

Interrupt enable register (IE): It is 8-bit register.

It is bit/byte addressable.

Its address is A8H.

It is used to enable and disable function of interrupt.

## **Interrupt priority register (IP):**

It is 8-bit register.

It is bit/byte addressable.

Its address is B8H.

It is used to select low or high level priority of each individual interrupts.

## **Power control register (PCON):**

It is 8-bit register.

It is byte addressable.

Its address is 87H.

Its bits are used to control mode of power saving circuit, either idle or power down mode and also one bit is used to modify baud rate of serial communication.

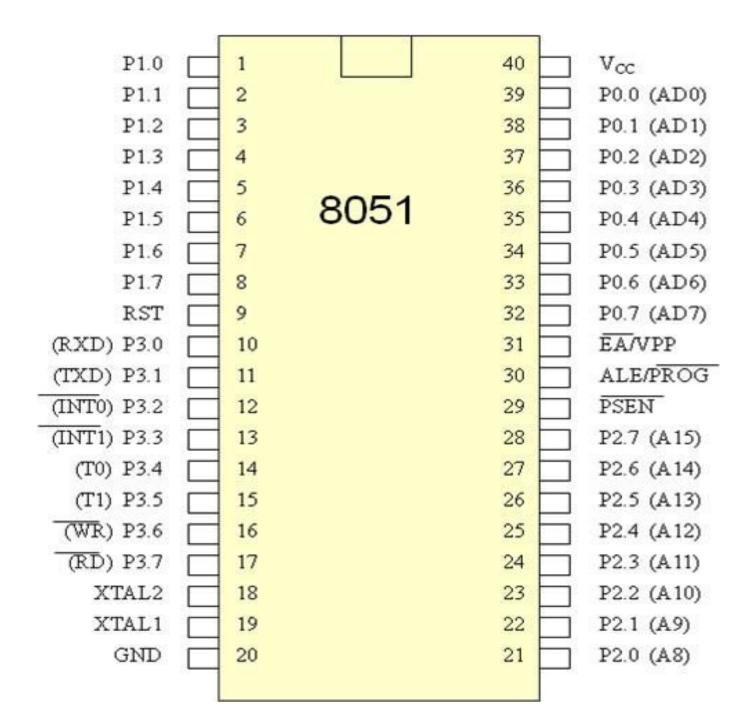

#### **PIN DIAGRAM**

# **Pinout Description**

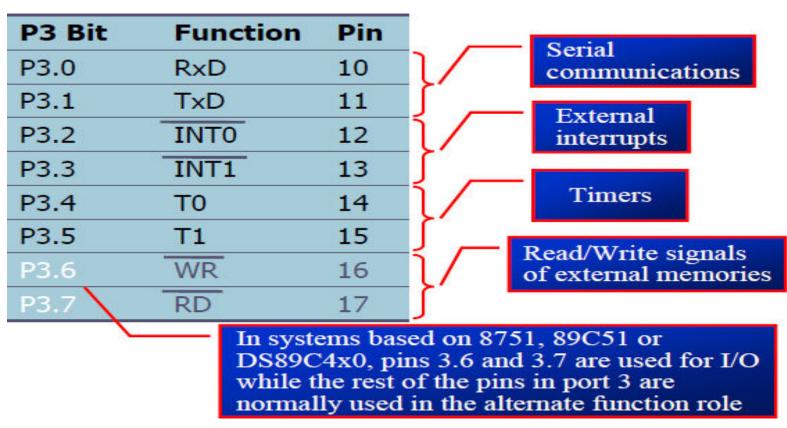

| <b>Pins 1-8</b> | PORT 1. Each of these pins can be configured as an input or an output.                                                                                                                                                                                                   |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin 9           | RESET. A logic one on this pin disables the microcontroller and clears the contents of most registers. In other words, the positive voltage on this pin resets the microcontroller. By applying logic zero to this pin, the program starts execution from the beginning. |  |

| Pins10-17       | PORT 3. Similar to port 1, each of these pins can serve as general input or output. Besides, all of them have alternative functions                                                                                                                                      |  |

| Pin 10          | RXD. Serial asynchronous communication input or Serial synchronous communication output.                                                                                                                                                                                 |  |

| Pin 11          | <b>TXD.</b> Serial asynchronous communication output or Serial synchronous communication clock output.                                                                                                                                                                   |  |

| <b>Pin 12</b>   | INT0.External Interrupt 0 input                                                                                                                                                                                                                                          |  |

| Pin 13          | INT1. External Interrupt 1 input                                                                                                                                                                                                                                         |  |

| Pin 14        | T0. Counter 0 clock input                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 15        | T1. Counter 1 clock input                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Pin 16</b> | WR. Write to external (additional) RAM                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin 17        | RD. Read from external RAM                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin 18, 19    | XTAL2, XTAL1. Internal oscillator input and output. A quartz crystal which                                                                                                                                                                                                                                                                                                                                                 |

|               | specifies operating frequency is usually connected to these pins.                                                                                                                                                                                                                                                                                                                                                          |

| Pin 20        | GND. Ground.                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin 21-28     | <b>Port 2</b> . If there is no intention to use external memory then these port pins are configured as general inputs/outputs. In case external memory is used, the higher address byte, i.e. addresses A8-A15 will appear on this port. Even though memory with capacity of 64Kb is not used, which means that not all eight port bits are used for its addressing, the rest of them are not available as inputs/outputs. |

| Pin 29        | PSEN. If external ROM is used for storing program then a logic zero (0)                                                                                                                                                                                                                                                                                                                                                    |

|               | appears on it every time the microcontroller reads a byte from memory.                                                                                                                                                                                                                                                                                                                                                     |

| Pin 31 | EA. By applying logic zero to this pin, P2 and P3 are used for data and       |

|--------|-------------------------------------------------------------------------------|

|        | address transmission with no regard to whether there is internal memory or    |

|        | not. It means that even there is a program written to the microcontroller, it |

|        | will not be executed. Instead, the program written to external ROM will be    |

|        | executed. By applying logic one to the EA pin, the microcontroller will use   |

|        | both memories, first internal then external (if exists).                      |

**Pin 32-39 PORT 0**. Similar to P2, if external memory is not used, these pins can be used as general inputs/outputs. Otherwise, P0 is configured as address output (A0-A7) when the ALE pin is driven high (1) or as data output (Data Bus) when the ALE pin is driven low (0).

Pin 40 VCC. +5V power supply.

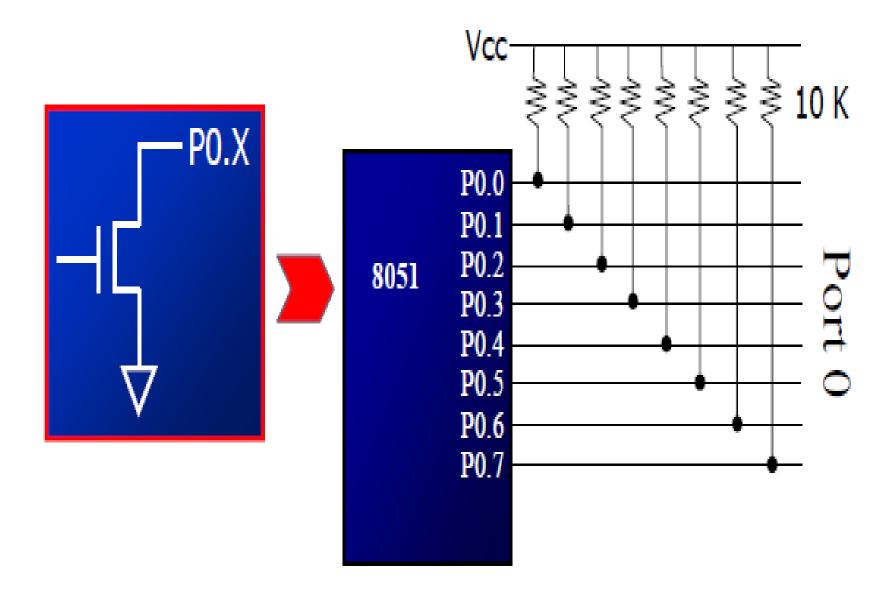

# **IO Port Usage in 8051**

- The four 8-bit I/O ports P0, P1, P2 and P3 each uses 8 pins.

- All the ports upon RESET are configured as input, ready to be used as input ports.

- When the first 0 is written to a port, it becomes an output port.

- To reconfigure it as an input, 1 must be sent to the port.

- To use any of these ports as an input port, it must be programmed.

- It can be used for input or output, each pin must be connected externally to a 10K ohm pull-up resistor.

- This is due to the fact that P0 is an open drain, unlike P1, P2, and P3.

- Open drain is a term used for MOS chips in the same way that open collector is used for TTL chips.

# Port 0 with Pull up registers

The following code will continuously send out to port 0 the alternating value 55H and AAH

BACK: MOV A,#55H

- MOV P0,A

- ACALL DELAY

- MOV A,#0AAH

- MOV P0,A

- ACALL DELAY

- SJMP BACK

- Port 0 as input

- In order to make port 0 an input, the port must be programmed by writing 1 to all the bits.

Port 0 is configured first as an input port by writing 1s to it, and then data is received from that port and sent to P1

- MOV A,#0FFH ;A=FF hex

- MOV P0,A ;make P0 an i/p port ;by writing it all 1s

- BACK: MOV A,P0 ;get data from P0

- MOV P1,A ;send it to port 1 SJMP BACK

#### **Dual role of Port 0**

Port 0 is also designated as AD0-AD7, allowing it to be used for both address and data. When connecting an 8051/31 to an external memory, port 0 provides both address and data.

## Port 1 can be used as input or output

In contrast to port 0, this port does not need any pull-up resistors since it already has pull-up resistors internally.

Upon reset, port 1 is configured as an input port.

The following code will continuously send out to port 0 the alternating value 55H and AAH MOV A,#55H

- BACK: MOV P1,A

- ACALL DELAY CPL A

- SJMP BACK

To make port 1 an input port, it must be programmed as such by writing 1to all its bits. Port 1 is configured first as an input port by writing 1s to it, then data is received from that port and saved in R7 and R5

- MOV A,#0FFH ;A=FF hex

- MOV P1,A ;make P1 an input port ;by writing it all 1s

- MOV A,P1 ;get data from P1

- MOV R7,A ;save it to in reg R7

- ACALL DELAY ; wait

- MOV A,P1 ;another data from P1

- MOV R5,A ;save it to in reg R5

#### Port 2 can be used as input or output

- Just like P1, port 2 does not need any pullup resistors since it already has pull-up resistors internally.

- Upon reset, port 2 is configured as an input port.

- To make port 2 an input port, it must be programmed as such by writing 1 to all its bits.

- In many 8051-based systems, P2 is used as simple I/O.

- In 8031-based systems, port 2 must be used along with P0 to provide the 16-bit address for the external memory.

- Port 2 is also designated as A8 A15, indicating its dual function.

- Port 0 provides the lower 8 bits via A0 A7.

# Port 3 can be used as input or output

Port 3 does not need any pull-up resistors. Port 3 is configured as an input port upon reset.

Port 3 has the additional function of providing some extremely important signals

Port 3 alternate functions

#### INSTRUCTION SET.

# **Instruction Timings**

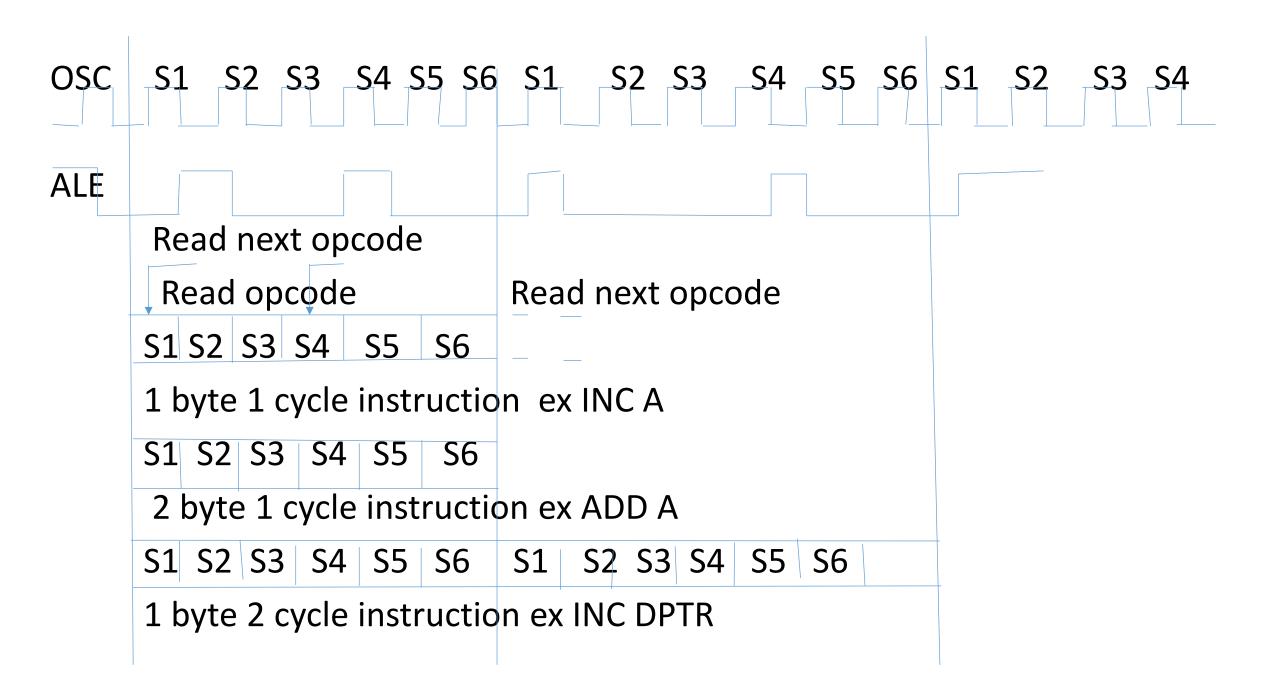

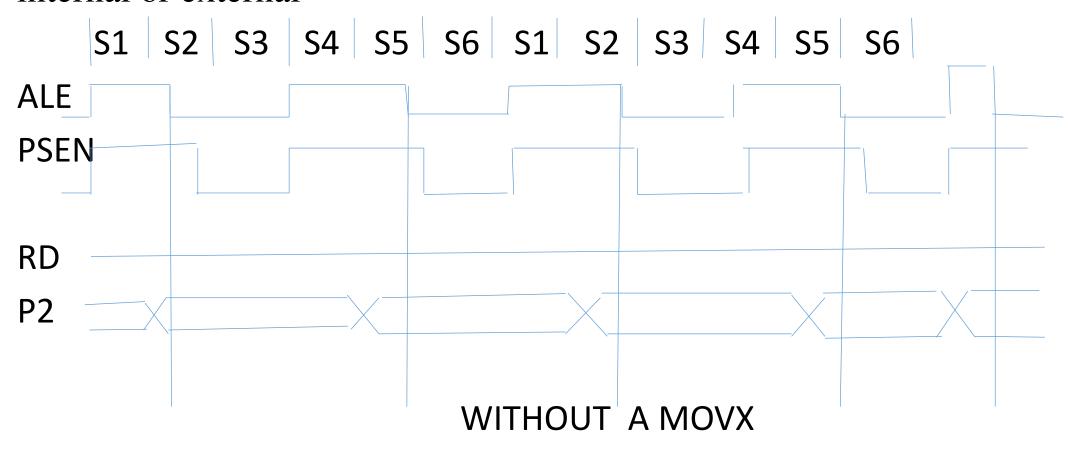

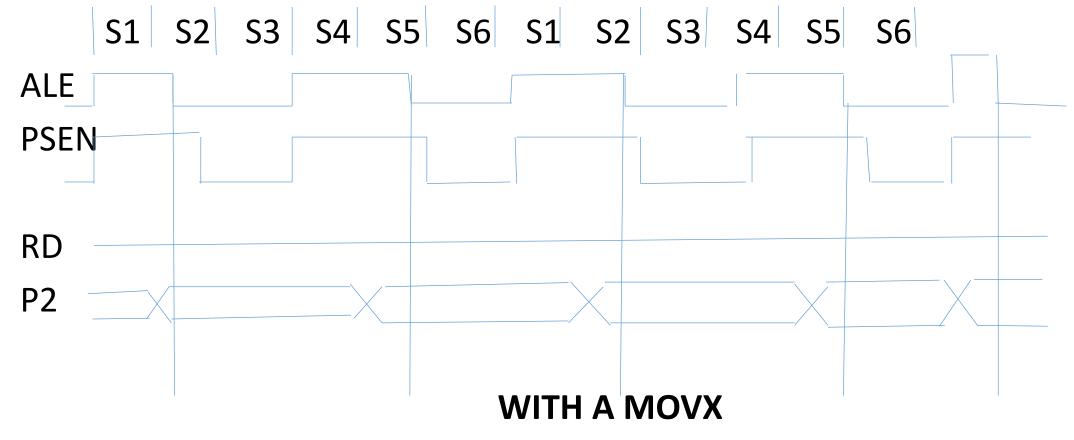

T-state, Machine cycle and Instruction cycle are terms used in instruction timings.

**T-state** is defined as one subdivision of the operation performed in one clock period. The terms 'T- state' and 'clock period' are often used synonymously **Machine cycle** is defined as 12 oscillator periods. A machine cycle consists of six states and each state lasts for two oscillator periods. An instruction takes one to four machine cycles to execute an instruction.

**Instruction cycle** is defined as the time required for completing the execution of an instruction. The 8051 instruction cycle consists of one to four machine cycles

#### 8051 Instructions

The instructions of 8051 can be broadly classified under the following headings.

- Data transfer instructions

- Arithmetic instructions

- Logical instructions

- Branch instructions

- Subroutine instructions

- Bit manipulation instructions

#### Data transfer instructions.

In this group, the instructions perform data transfer operations of the following types.

Move the contents of a register Rn to A

- MOV A,R2

- MOV A,R7

Move the contents of a register A to Rn

- MOV R4,A

- MOV R1,A

Move an immediate 8 bit data to register A or to Rn or to a memory location(direct or indirect)

MOV A, #45H

MOV R6, #51H

Move the contents of a memory location to A or A to a memory location using direct and indirect addressing

MOV A, 65H

MOV 45H, A

Move the contents of a memory location to Rn or Rn to a memory location using direct addressing

MOV R3, 65H

MOV 45H, R2

Move the contents of memory location to another memory location using direct and indirect addressing

MOV 47H, 65H

#### **Push and Pop instructions**

MOV R6, #25H

MOV R1, #12H

PUSH 6 [SP]=08[08]=[06]=25H //CONTENT OF 08 IS 25H

PUSH 1 [SP]=09 [09]=[01]=12H //CONTENT OF 09 IS 12H

PUSH 4 [SP]=0A [0A]=[04]=F3H //CONTENT OF 0A IS F3H

#### **Exchange instructions**

The content of source ie., register, direct memory or indirect memory will be exchanged with the contents of destination ie., accumulator.

XCH A,R3

XCH A,@R1

XCH A,54h

#### Arithmetic instructions.

The 8051 can perform addition, subtraction. Multiplication and division operations on 8 bit numbers.

#### Addition

In this group, we have instructions to

Add the contents of A with immediate data with or without carry.

ADD A, #45H

Add the contents of A with register Rn with or without carry.

ADD A, R5

ADDC A, R2

Add the contents of A with contents of memory with or without carry using direct and indirect addressing

**ADD A, 51H**

ADDC A, 75H

## **Subtraction**

In this group, we have instructions to

Subtract the contents of A with immediate data with or without carry.

SUBB A, #45H

Subtract the contents of A with register Rn with or without carry.

SUBB A, R5

SUBB A, R2

Subtract the contents of A with contents of memory with or without carry using direct and indirect addressing

SUBB A, 51H

SUBB A, 75H

## Multiplication

**MULAB.** This instruction multiplies two 8 bit unsigned numbers which are stored in A and B register. After multiplication the lower byte of the result will be stored in accumulator and higher byte of result will be stored in B register.

**DIV AB.** This instruction divides the 8 bit unsigned number which is stored in A by the 8 bit unsigned number which is stored in B register. After division the result will be stored in accumulator and remainder will be stored in B register.

- Eg. MOV A,#45H ;[A]=0E8H

- MOV B,#0F5H ;[B]=1BH

- DIV AB ;[A] / [B] = E8 / 1B = 08 H with remainder 10H;[A] = 08H, [B] = 10H

#### DA A (Decimal Adjust After Addition).

When two BCD numbers are added, the answer is a non-BCD number. To get the result in BCD, we use DA A instruction after the addition

Eg 1: MOV A,#23H

MOV R1,#55H

ADD A,R1 // [A]=78

DAA // [A]=78 no changes in the accumulator after da a

Eg 2: MOV A,#53H

MOV R1,#58H

ADD A,R1 // [A]=ABh

DA A // [A]=11, C=1 . ANSWER IS 111. Accumulator data is changed after DA A

#### **Increment**

Increments the operand by one.

INC increments the value of source by 1

If the initial value of register is FFh, incrementing the value will cause it to reset to 0.

#### **Decrement**

Decrements the operand by one.

DEC decrements the value of source by 1. If the initial value of is 0, decrementing the value will cause it to reset to FFh.

## **Logical Instructions**

## **Logical AND**

ANL destination, source:

ANL does a bitwise "AND" operation between source and destination, leaving the resulting value in destination

The value in source is not affected

"AND" instruction logically AND the bits of source and destination.

ANL A, #DATA

ANLA, Rn

Logical OR

**ORL** destination, source

ORL does a bitwise "OR" operation between source and destination, leaving the resulting value in destination.

The value in source is not affected. "OR" instruction logically OR the bits of source and destination.

ORL A,#DATA

ORLA, Rn

**Logical Ex-OR**

XRL destination, source

XRL does a bitwise "EX-OR" operation between source and destination, leaving the resulting value in destination.

The value in source is not affected. "XRL" instruction logically EX-OR the bits of source and destination.

XRL A,#DATA

XRL A,Rn

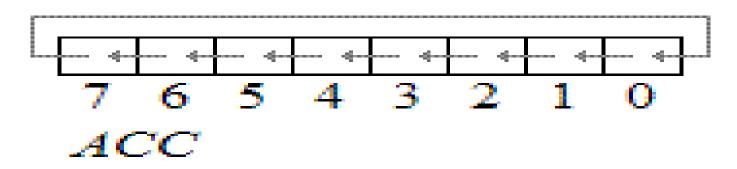

#### **Rotate Instructions RR A**

This instruction is rotate right the accumulator.

Each bit is shifted one location to the right, with bit 0 going to bit 7.

**RLA**

Rotate left the accumulator. Each bit is shifted one location to the left, with bit 7 going to bit 0

#### **RRC** A

Rotate right through the carry.

Each bit is shifted one location to the right, with bit 0 going into the carry bit in the PSW, while the carry was at goes into bit 7

#### **RLCA**

Rotate left through the carry. Each bit is shifted one location to the left, with bit 7 going into the carry bit in the PSW, while the carry goes into bit 0.

# **Branch (JUMP) Instructions**

#### **Jump and Call Program Range**

There are 3 types of jump instructions. They are:-

- Relative Jump

- Short Absolute Jump

- Long Absolute Jump

## **Relative Jump**

Jump that replaces the PC (program counter) content with a new address that is greater than or less than is called a relative jump.

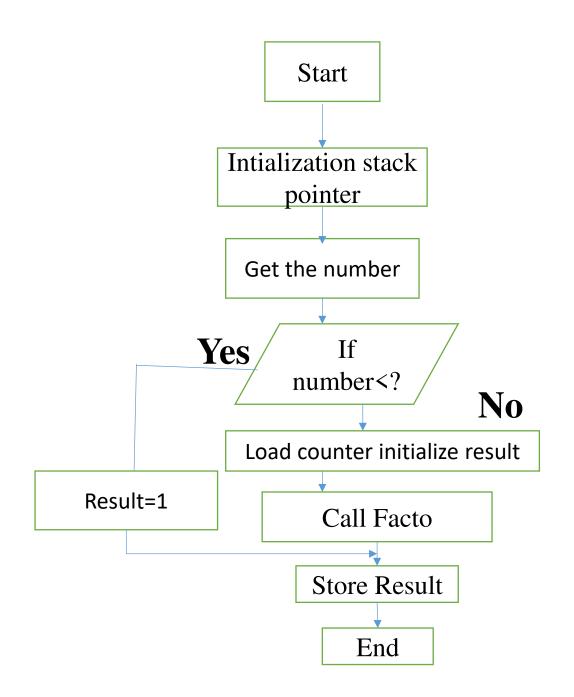

## The advantages of the relative jump are