#### MUTHAYAMMAL ENGINEERING COLLEGE Rasipuram - 637 408

#### COURSE CODE & TITLE - 19GES24/DIGITAL PRINCIPLES AND SYSTEM DESIGN

<u>UNIT-1</u>

#### **BOOLEAN ALGEBRA AND LOGIC GATES**

Presentation by Mrs.V.Hema AP-ECE

#### **SYLLABUS**

#### • UNIT I: BOOLEAN ALGEBRA AND LOGIC GATES

Review of Number Systems –Arithmetic Operations -Binary Codes– Boolean Algebra and Theorems –Boolean Functions–Simplification of Boolean Functions using Karnaugh Map and Tabulation Methods –Logic Gates–NAND and NOR Implementations.

#### • UNIT II :COMBINATIONAL LOGIC

Combinational Circuits – Analysis and Design Procedures–Circuits for Arithmetic Operations, Code Conversion – Decoders and Encoders – Multiplexers and Demultiplexers – Introduction to HDL – HDL Models of Combinational circuits.

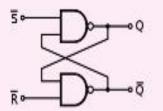

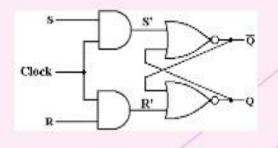

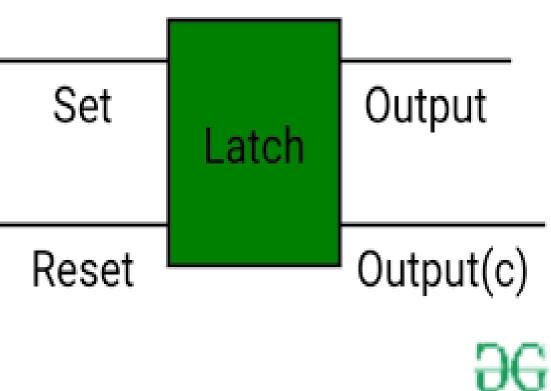

#### • UNIT III:SYNCHRONOUS SEQUENTIAL LOGIC

Sequential Circuits –Latches and Flip Flops –Analysis and Design Procedures –State Reduction and State Assignment –Shift Registers–Counters –HDL for Sequential Logic Circuits.

#### **SYLLABUS**

#### • UNIT IV:ASYNCHRONOUS SEQUENTIAL LOGIC

Analysis and Design of Asynchronous Sequential Circuits– Reduction of State and Flow Tables –Race-free State Assignment– Hazards.

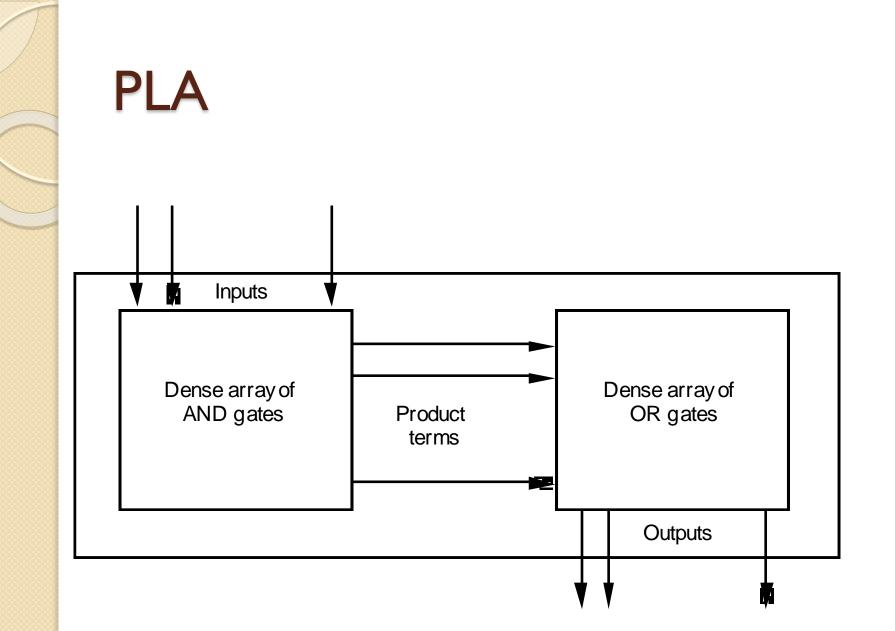

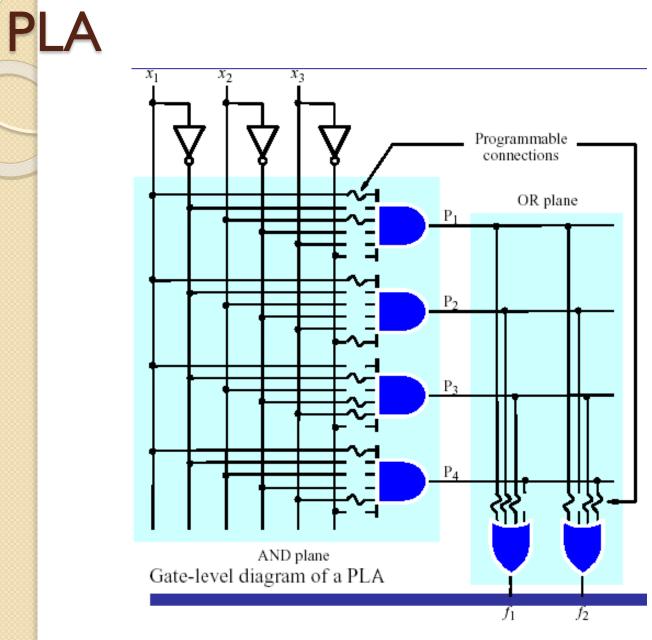

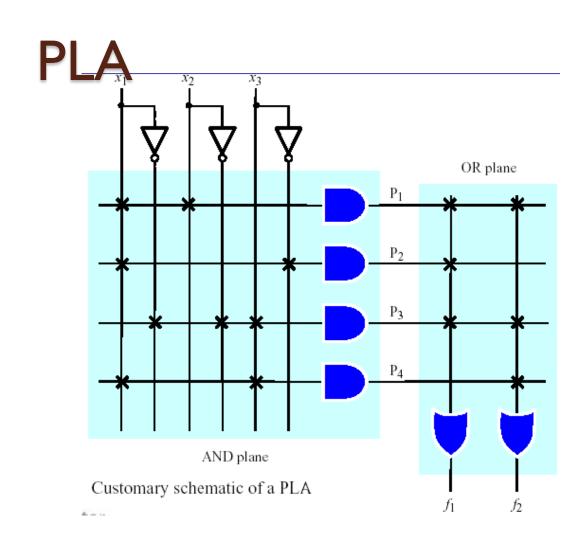

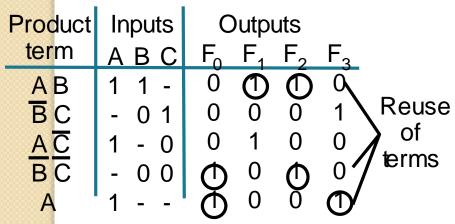

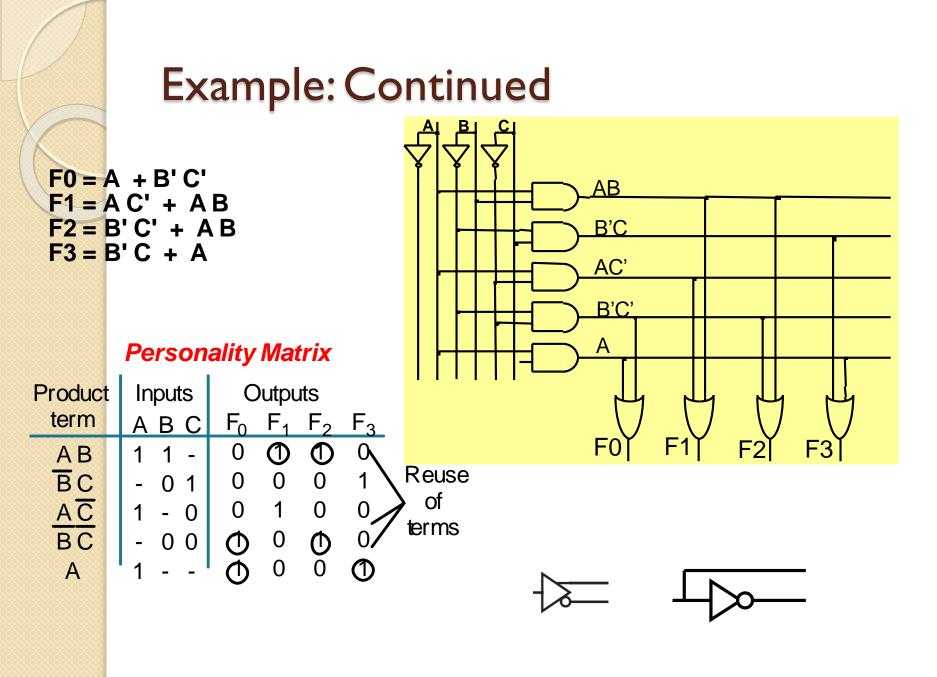

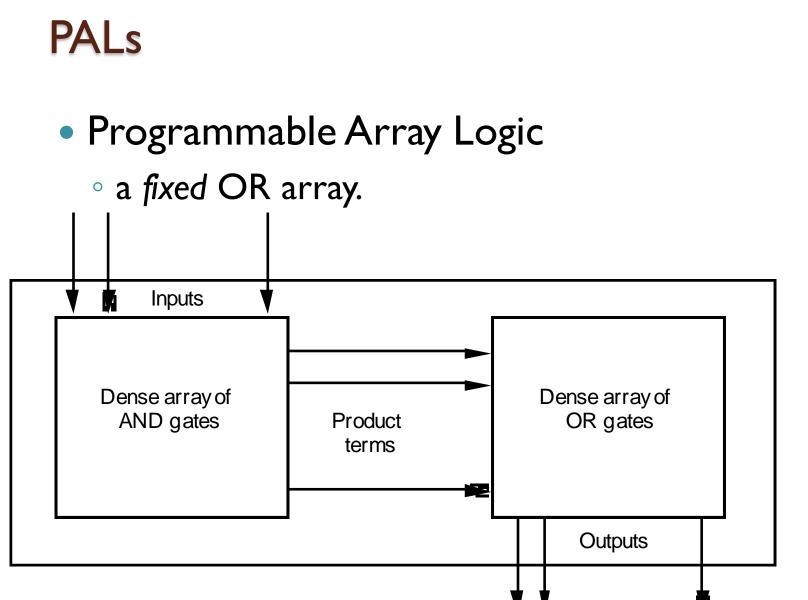

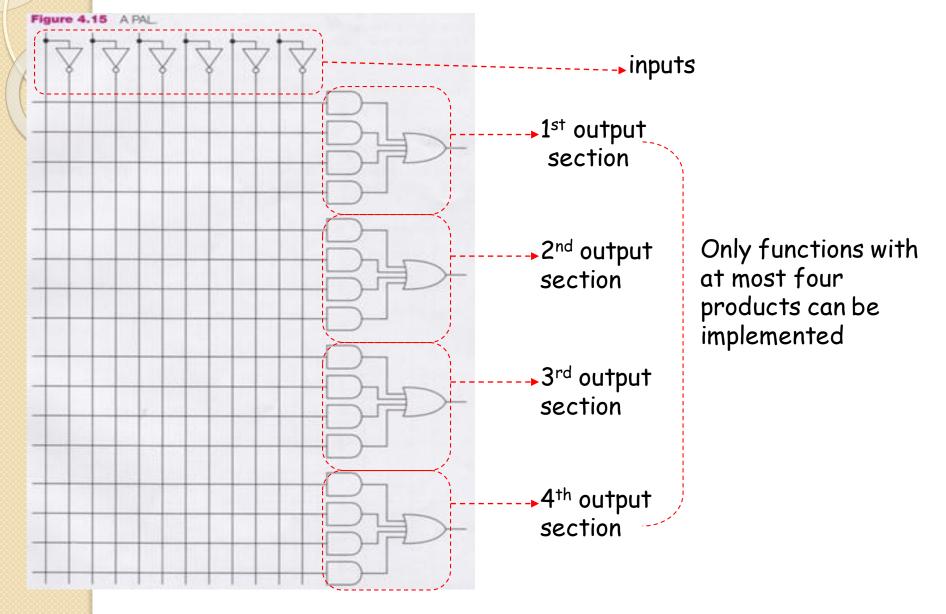

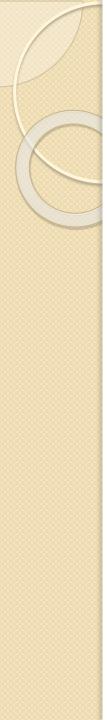

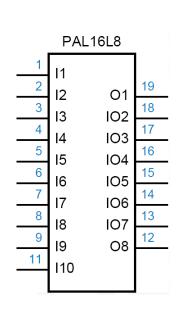

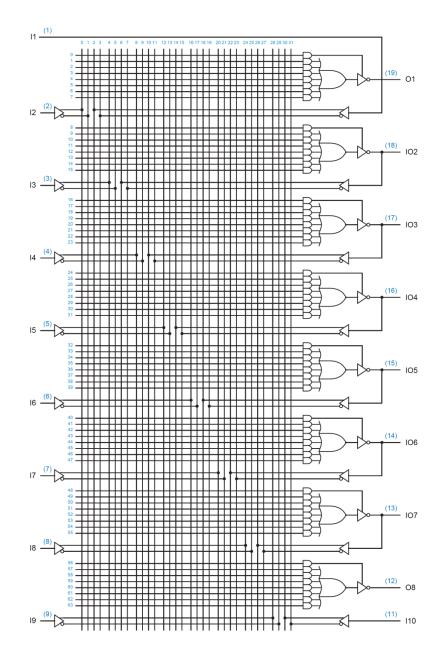

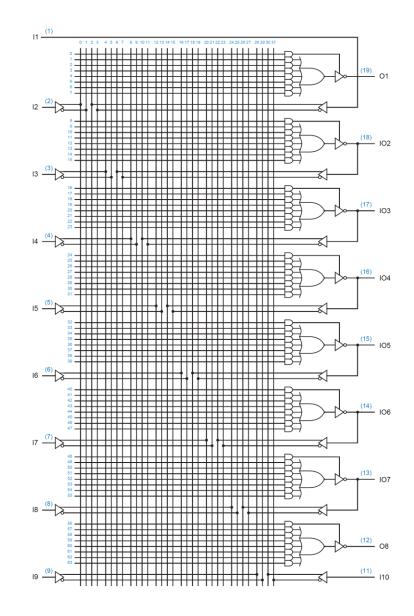

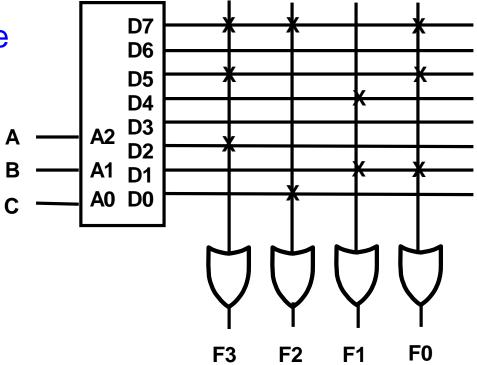

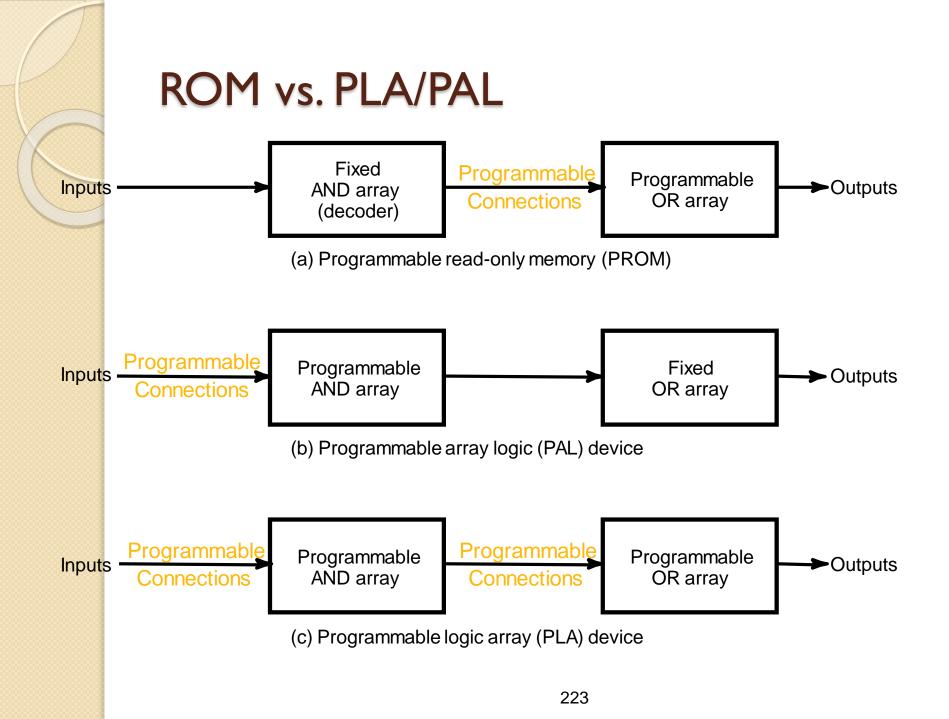

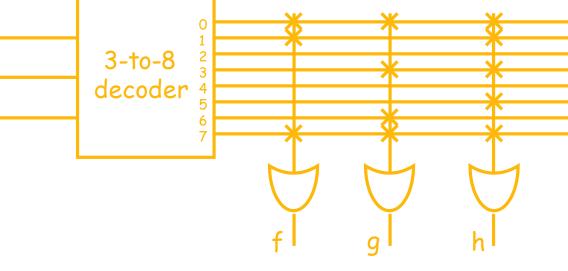

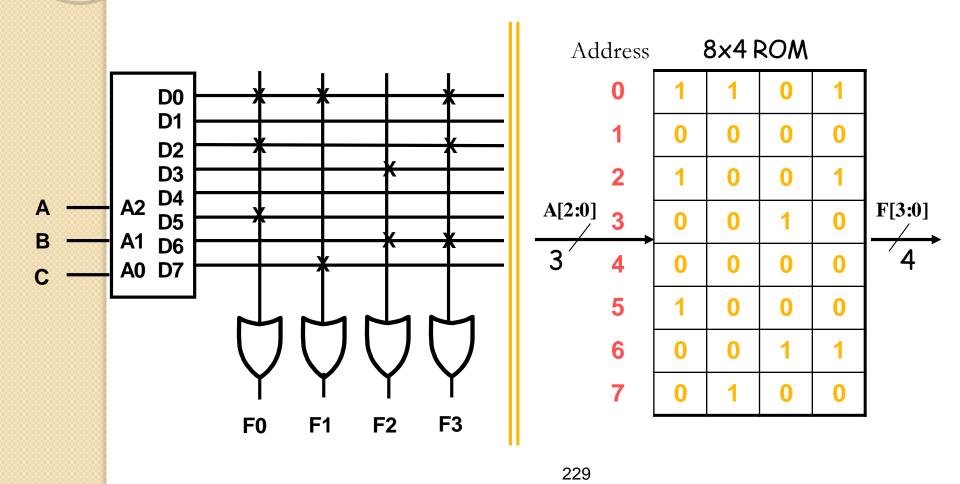

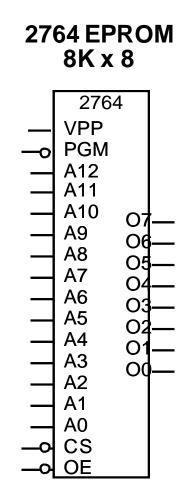

#### • UNIT V:MEMORY AND PROGRAMMABLE LOGIC

RAM and ROM –Memory Decoding –Error Detection and Correction –Programmable Logic Array –Programmable Array Logic –Sequential Programmable Devices –Application Specific Integrated Circuits.

#### • TEXT BOOKS:

1."Digital Design", Pearson Education Publication, IV

Edition 2008 by Morris Mano M. and Michael D. Ciletti

2. "Digital Design Principles and Practices", Pearson Education

Publication, IV Edition 2008 by John F.Wakerly

# INTRODUCTION

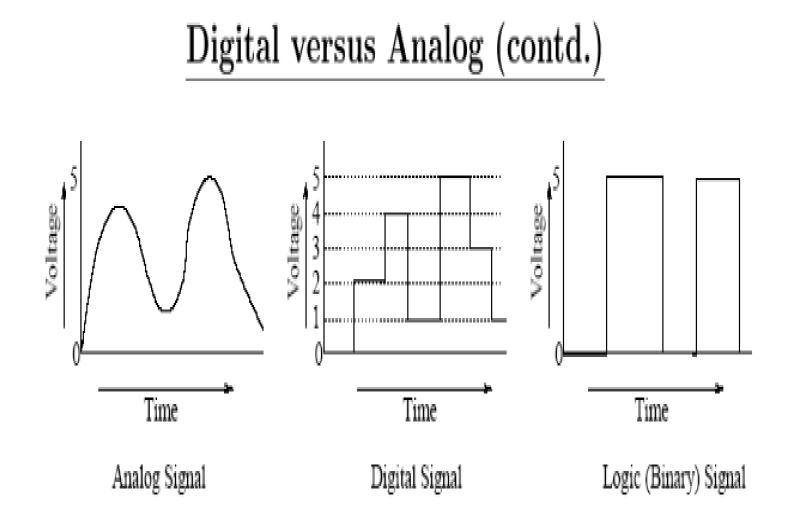

Basically there are two types of signals in electronics,

i) Analog

ii) Digital

- The term digital refers to any process that is accomplished using discrete units

- Digital computer is the best example of a digital system.

- Almost all digital circuits are really logic circuits because it is much easier to manipulate and process multiple voltage levels

# **ADVANTAGES AND DISADVANTAGES**

The usual advantages of digital circuits when compared to analog circuits are:

- Information storage can be **easier**

- Robustness

The Disadvantages of digital circuits are:

- Digital circuits are sometimes more **expensive**

- Digital systems must translate from continuous analog signals to discrete digital signals. This causes **quantization errors.**

# NUMBER SYSTEMS

- A system for representing number of certain type is called "Number System".

- Integers are normally written using positional numbering number system, in which each digit represents the coefficient in a power series.

$$N = a_{n-1}r^{n-1} + a_{n-2}r^{n-2} + \dots + a_2r^2 + a_1r^1 + a_0$$

• Where n is the number of digit, r is the radix or base and  $a_i$  is the coefficient

$$0 \le a_i < r$$

# **REVIEW OF NUMBER SYSTEMS**

- Many number systems are in use in digital technology.

- The decimal system is clearly the most familiar to us because it is tools that we use every day.

- Types of Number Systems are

- Decimal Number system

- Binary Number system

- > Octal Number system

- > Hexadecimal Number system

# **DECIMAL NUMBER SYSTEM**

- Decimal system is composed of 10 numerals or symbols. These 10 symbols are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9.

- Using these symbols as digits of a number, we can express any quantity.

- The decimal system is also called the base-10 system because it has 10 digits.

- Even though the decimal system has only 10 symbols, any number of any magnitude can be expressed by using our system of positional weighting.

Example: 3.14<sub>10</sub>, 52<sub>10</sub>, 1024<sub>10</sub>

# **BINARY SYSTEM**

- In the binary system, there are only two symbols or possible digit values, 0 and 1.

- This base-2 system can be used to represent any quantity that can be represented in decimal or other base system.

- Binary quantities can be represented by any device that has only two operating states or possible conditions.

- E.g.. A switch is only open or closed. We arbitrarily (as we define them) let an open switch represent binary 0 and a closed switch represent binary 1. Thus we can represent any binary number by using series of switches.

#### **OCTAL NUMBER SYSTEM**

- The octal number system has a base of eight, meaning that it has eight possible digits: 0,1,2,3,4,5,6,7.

- An older computer-based number system is "octal" or base eight. The digits in octal math are 0, 1, 2, 3, 4, 5, 6, and 7. The value "eight" is written as "1 eight and 0 ones" or 10<sub>8</sub>.

- Since, the octal numbers uses less number of digits as compared to decimal numbers and hexadecimal numbers therefore it is easy to do computations in fewer steps and also less chances of occurrence of error.

# HEXADECIMAL NUMBER SYSTEM

- The hexadecimal system uses base 16. Thus, it has 16 possible digit symbols. It uses the digits 0 through 9 plus the letters A, B, C, D, E, and F as the 16 digit symbols.

- Hexadecimal numbering system is often used by programmers to simplify the binary numbering system. Since 16 is equivalent to 2<sup>4</sup>, there is a linear relationship between the numbers 2 and 16.

- Computers use binary numbering system while humans use hexadecimal numbering system to shorten binary and make it easier to understand.

# Fig: Number system and their Base value

| Numbering Systems |      |                  |  |

|-------------------|------|------------------|--|

| System            | Base | Digits           |  |

| Binary            | 2    | 01               |  |

| Octal             | 8    | 01234567         |  |

| Decimal           | 10   | 0123456789       |  |

| Hexadecimal       | 16   | 0123456789ABCDEF |  |

|         | Fig: Types of | Number Systems   |             |

|---------|---------------|------------------|-------------|

| DECIMAL | BINARY        | OCTAL            | HEXADECIMAL |

| 0       | 0000          | 0                | 0           |

| 1       | 0001          | 1                | / 1         |

| 2       | 0010          | 2                | 2           |

| 3       | 0011          | 23               | 3           |

| 4       | 0100          | tes 4 🕒          | 4           |

| 5       | 0101          | 5                | 5           |

| 6       | 0110          | 6                | 6           |

| 7       | 0111          | -110 7           | 7           |

| 8       | 1000          | 10               | 8           |

| 9_      | 1001          | ь — 11           | • 9         |

| 10 0    | c f 1010r e   | Notes            | 1 11 A      |

| 11      | 1011          | $NO_{13}^{12}eS$ | B           |

| 12      | 1100          | 14               | С           |

| 13      | 1101          | 15               | D           |

| 14      | 1110          | 16               | E           |

| 15      | 1111          | 17               | F           |

# **CODE CONVERSION**

- Coding is the process of translating the input information which can be understandable by the machine or a particular device.

- Coding can be used for security purpose to protect the information from steeling or interrupting.

- Converting from one code form to another code form is called code conversion, like converting from binary to decimal or converting from hexadecimal to decimal.

# **BINARY TO DECIMAL COVERSION**

- Any binary number can be converted to its decimal equivalent simply by summing together the weights of the various positions in the binary number which contain a 1.

- The decimal number is equal to the sum of binary digits (d<sub>n</sub>) times their power of 2 (2<sup>n</sup>):

- decimal =  $d_0 \times 2^0 + d_1 \times 2^1 + d_2 \times 2^2 + \dots$

#### Example

Find the decimal value of  $111001_2$ :

| binary number: | 1              | 1              | 1              | 0              | 0              | 1              |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| power of 2:    | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |

•  $|||00|_2 = |\cdot 2^5 + |\cdot 2^4 + |\cdot 2^3 + 0 \cdot 2^2 + 0 \cdot 2^1 + |\cdot 2^0 = 57_{10}$

# **DECIMAL TO BINARY CONVERSION**

There are 2 methods:

- Reverse of Binary-To-Decimal Method

- Repeat Division

Reverse of Binary-To-Decimal Method

| Decimal | Binary                         |

|---------|--------------------------------|

| 4510    | =32 + 0 + 8 + 4 + 0 + 1        |

|         | $=2^{5}+0+2^{3}+2^{2}+0+2^{0}$ |

| Result  | =1011012                       |

Repeat Division-Convert decimal to binary: This method uses repeated division by 2.

| Division | Remainder            | Binary                    |  |

|----------|----------------------|---------------------------|--|

| 25/2     | = 12+ remainder of 1 | 1 (Least Significant Bit) |  |

| 12/2     | = 6 + remainder of 0 | 0                         |  |

| 6/2      | = 3 + remainder of 0 | 0                         |  |

| 3/2      | = 1 + remainder of 1 | 1                         |  |

| 1/2      | = 0 + remainder of 1 | 1 (Most Significant Bit)  |  |

| Result   | 2510                 | = 110012                  |  |

#### Contd,.

#### **Conversion steps:**

- Divide the number by 2.

- Get the integer quotient for the next iteration.

- Get the remainder for the binary digit.

- Repeat the steps until the quotient is equal to 0.

#### Example #1

Convert 13<sub>10</sub> to binary:

| Division<br>by 2 | Quotient | Remainder | Bit # |

|------------------|----------|-----------|-------|

| 13/2             | 6        | 1         | 0     |

| 6/2              | 3        | 0         | 1     |

| 3/2              | 1        | 1         | 2     |

| 1/2              | 0        | 1         | 3     |

So 13<sub>10</sub> = 1101<sub>2</sub>

#### **EXAMPLE**

1. How to convert 145 into the binary number system? Solution:

| Division of<br>Decimal<br>Number by 2 | Quotient | Remainder | Binary                |

|---------------------------------------|----------|-----------|-----------------------|

| 145/2                                 | 72       | 1         | 1 <mark>(</mark> LSB) |

| 72/2                                  | 36       | 0         | 0                     |

| 36/2                                  | 18       | 0         | 0                     |

| 18/2                                  | 9        | 0         | 0                     |

| 9/8                                   | 4        | 1         | 1                     |

| 4/2                                   | 2        | 0         | 0                     |

| 2/2                                   | 1        | 0         | 0                     |

| 1/2                                   | 0        | 1         | 1 (MSB)               |

Hence, 14510 = 100100012

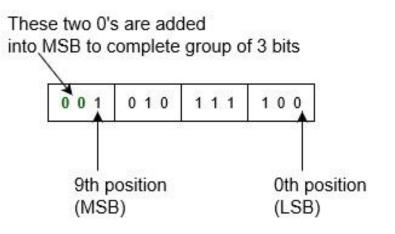

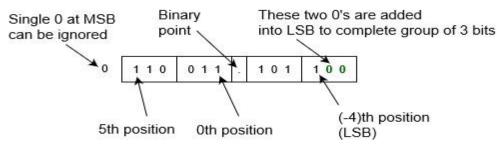

# **BINARY TO OCTAL**

The following are the steps to convert a binary number into octal number.

- Take binary number

- Divide the binary digits into groups of three (starting from right) for integer part and start from left for fraction part.

- Convert each group of three binary digits to one octal digit.

**Example-1** – Convert binary number 1010111100 into octal number. Since there is no binary point here and no fractional part. So,

#### Contd,.

• Therefore, Binary to octal is.

$=(001 \ 010 \ 111 \ 100)_2$

$=(1 2 7 4)_8$

Example-2 Convert binary number 0110 011.1011 into octal number. Since there is binary point here and fractional part. So,

- Therefore, Binary to octal is.

- $= (0|000|.000)_{2}$

- $= (0 | | 0 0 | | . | 0 | |)_2$

- $= (110011.101100)_{2}$

- = (6 3 . 5 4)<sub>8</sub>

# **OCTAL TO BINARY**

This method is simple and also works as reverse of Binary to Octal Conversion. The algorithm is explained as following below.

- Take Octal number as input

- Convert each digit of octal into binary.

- That will be output as binary number.

**Example:** Convert octal number 540 into binary number. According to above algorithm, equivalent binary number will be,

- $=(540)_{8}$

- $= (101\ 100\ 000)_2$

- $=(101100000)_2$

# **DECIMAL TO OCTAL**

Follow the steps given below to learn the decimal to octal conversion:

- Write the given decimal number

- If the given decimal number is less than 8 the octal number is the same.

- If the decimal number is greater than 7 then divide the number by 8.

- Note the remainder we get after division

- Repeat step 3 and 4 with the quotient till it is less than 8

- Now, write the remainders in reverse order(bottom to top)

- The resultant is the equivalent octal number to the given decimal number.

| Decimal Number | Operation | Quotient | Remainder | Octal Number |

|----------------|-----------|----------|-----------|--------------|

| 1792           | ÷ 8       | 224      | 0         | 0            |

| 224            | ÷ 8       | 28       | 0         | 00           |

| 28             | ÷ 8       | 3        | 4         | 400          |

| 3              | ÷ 8       | 0        | 3         | 3400         |

For example: Convert 1792 into octal number.

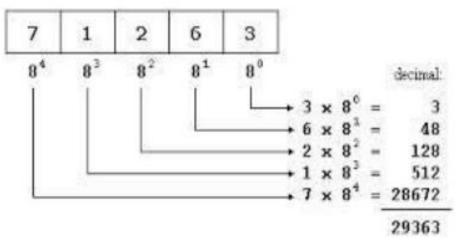

# **OCTAL TO DECIMAL**

- To convert an octal number (base-8) to the decimal (base-10) number system, we need to use octal place value to add the base-10 value of each digit.

- In the octal place value system, each time you move a place to the left, the value increases eight-fold.

Octal to Decimal

#### HEXADECIMAL TO DECIMAL

Here are the steps to convert hex to decimal:

- Get the decimal equivalent of hex from table.

- Multiply every digit with 16 power of digit location.

- Sum all the multipliers.

Example:

•  $7DE = (7 * 16^2) + (13 * 16^1) + (14 * 16^0)$

=(7 \* 256) + (13 \* 16) + (14 \* 1)

= 1792 + 208 + 14

7DE = 2014

# **DECIMAL TO HEXADECIMAL**

- Take decimal number as dividend.

- Divide this number by 16 (16 is base of hexadecimal so divisor here).

- Store the remainder in an array (it will be: 0 to 15 because of divisor 16, replace 10, 11, 12, 13, 14, 15 by A, B, C, D, E, F respectively).

- Repeat the above two steps until the number is greater than zero.

- Example Convert decimal number 540 into hexadecimal number.

- Since given number is decimal integer number, so by using above algorithm performing short division by 16 with remainder.

#### Contd,.

| Division      | Remainder (R) |

|---------------|---------------|

| 540 / 16 = 33 | 12 = C        |

| 33 / 16 = 2   | 1             |

| 2 / 16 = 0    | 2             |

| 0 / 16 = 0    | 0             |

• Now, write remainder from bottom to up (in reverse order), this will be 021C (or only 21C) which is equivalent hexadecimal number of decimal integer 540.

#### **BINARY TO HEXADECIMAL**

- Hexadecimal number system provides convenient way of converting large binary numbers into more compact and smaller groups.

- First, we need to convert a binary into other base system (e.g., into decimal, or into octal). Then we need to convert it hexadecimal number.

- **Example** Convert binary number 1101010 into hexadecimal number.

- First convert this into decimal number:

- $(1101010)_2 = 1x2^6 + 1x2^5 + 0x2^4 + 1x2^3 + 0x2^2 + 1x2^1 + 0x2^0$ =  $64 + 32 + 0 + 8 + 0 + 2 + 0 = (106)_{10}$

- Then, convert it into hexadecimal number (106)<sub>10</sub> =106/16=6.625=0.625\*16=10(A) =6/16=0.35=0.35\*16= 6

- $= (6A)_{16}$  which is answer.

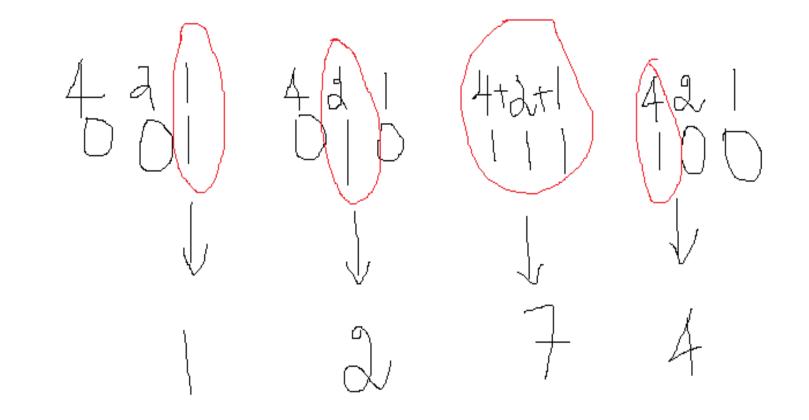

### **HEXADECIMAL TO BINARY**

- Step 1: Write down the hex number. If there are any, change the hex values represented by letters to their decimal equivalents.

- Step 2: Each hex digit represents four binary digits and therefore is equal to a power of 2.

- Step 3: Determine which powers of two (8, 4, 2 or 1) sum up to your hex digits.

- Step 4: Write down 1 below those 8, 4, 2 and 1's that are used. Write down 0 below those that are not used.

- Step 5: Read the 1's and 0's from left to right to get the binary equivalent of the given hex number.

#### Contd,.

• Example 1:

$(2C1)_{16} = ?$

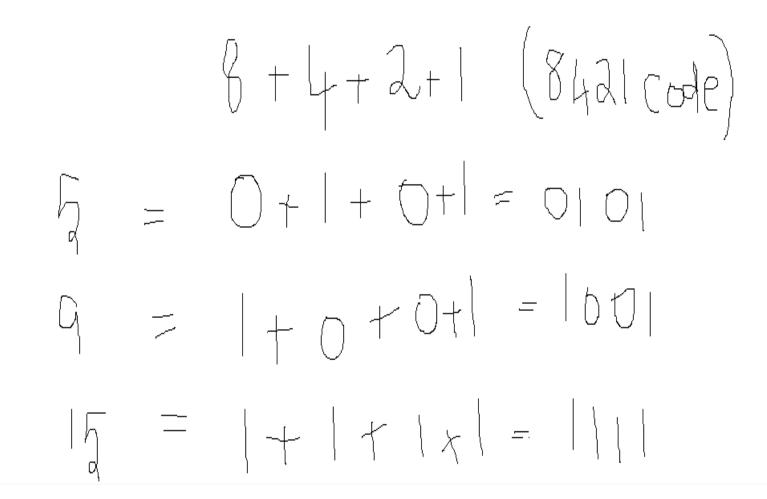

2 C 1

2 12 1 (using 8421 code) 0010 1100 0001 -----→ binary number Example 2:  $(9DB2)_{16} = ?$ 9 D B 2 9 13 11 2 (using 8421 code) 1001 1101 1011 0010 -----→ binary number

# **COMPLEMENT OF NUMBERS**

- Complements are used in digital computers to simplify the subtraction operation and for logical manipulation.

- There are TWO types of complements for each base-r system: the radix complement and the diminished radix complement.

- The first is referred to as the r's complement and the second as the (r 1)'s complement.

- The two types are referred to as

- 2's complement and

- 1's complement for binary numbers

and the 10's complement a complement for decimal numbers.

# 1's and 2's COMPLEMENT

- The 1's complement of a binary number is the number that results when we change all1's to zeros and the zeros to ones.

- The 2's complement is the binary number that results when we add 1 to the 1's complement. It is used to represent negative numbers.

Binary representation of 5 is: 0101

1's Complement of 5 is: 1010

2's Complement of 5 is: (1's Complement + 1) i.e.

1010 (1's Compliment)

+1

1011 (2's Complement i.e. -5)

# **ARITHMETIC OPERATIONS**

- The basic arithmetic operations for real numbers are addition, subtraction, multiplication, and division.

- The basic arithmetic properties are the commutative, associative, and distributive properties.

#### **Commutative Property**

• The commutative property describes equations in which the order of the numbers involved does not affect the result. Addition and multiplication are commutative operations:

2+3=3+2=5

$5 \cdot 2 = 2 \cdot 5 = 10$

Subtraction and division, however, are not commutative.

#### **Associative Property**

• The associative property describes equations in which the grouping of the numbers involved does not affect the result.

#### **ARITHMETIC OPERATIONS**

• As with the commutative property, addition and multiplication are associative operations:

(2+3)+6 = 2+(3+6)=11

$(4 \cdot 1) \cdot 2 = 4 \cdot (1 \cdot 2) = 8$

Subtraction and division are not associative.

#### **Distributive Property**

• The distributive property can be used when the sum of two quantities is then multiplied by a third quantity.

$(2+4)\cdot 3 = 2\cdot 3 + 4\cdot 3 = 18$

# **Arithmetic Operators**

| Operators | Meaning                                                     | Example | Result |

|-----------|-------------------------------------------------------------|---------|--------|

| +         | Addition                                                    | 4+2     | 6      |

| -         | Subtraction                                                 | 4-2     | 2      |

| *         | Multiplication                                              | 4*2     | 8      |

| /         | Division                                                    | 4/2     | ß      |

| %         | Modulus operator to<br>get remainder in<br>integer division | 5%2     | 1      |

### **RULES FOR ARTHIMETIC OPERATIONS**

#### 1. Rules of Binary Addition

0 + 0 = 0

- 0 + 1 = 1

- 1 + 0 = 1

- 1 + 1 = 0, and carry 1 to the next more significant bit

- $\checkmark$  Example 1 1

00011010 + 00001100 = 00100110

0 0 0 1 1 0 1 0

+0 0 0 0 1 1 0 0

0 0 1 0 0 1 1 0

## **RULES FOR ARTHIMETIC OPERATIONS**

#### 2. Rules of Binary Subtraction

0 - 0 = 0

0 - 1 = 1, and borrow 1 from the next more significant bit

1 - 0 = 1

1 - 1 = 0

✓ Example

00100101 - 00010001 = 00010100

0 0 1 0 0 1 0 1 + 0 0 0 1 0 0 1

0 0 0 1 0 1 0 0

#### EXAMPLE

## **Binary Subtraction**

# *Example:* Subtract binary number 101 from 1011

(borrow) 0 1 1 0 1 1 - 1 0 1 0 1 1 0

## **RULES FOR ARTHIMETIC OPERATIONS**

#### 3) Rules of Binary Multiplication

$0 \ge 0 \ge 0$

$0 \ge 1 = 0$

$1 \ge 0 = 0$

$1 \ge 1$ , and no carry or borrow bits

✓ Example

00101001 × 1 0 1 0 0 × 0 0 0 0 0 1 1 0 0 0 1 0 0 1

## **RULES FOR ARTHIMETIC OPERATIONS**

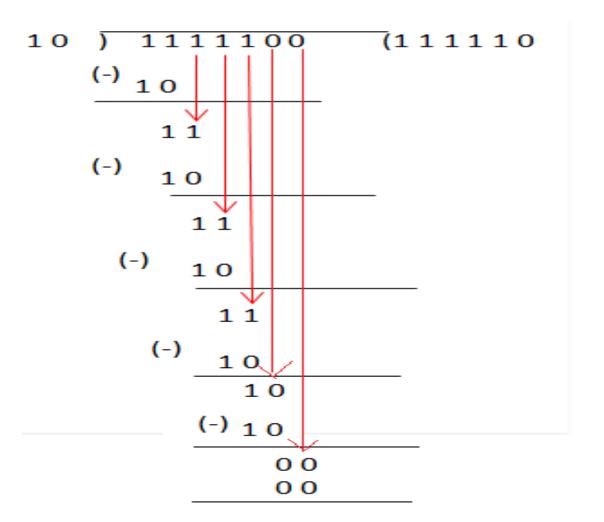

#### 4) Rules of Binary Division

• The process of binary **division** does not have any **specific** rules to follow. Though this process is quite similar to the decimal division.

Example:

$101)11010(101 \rightarrow \text{quotient})$

| 00110 |

|-------|

| 101   |

0 0 1  $\rightarrow$  remainder

## **BINARY CODES**

- The digital data is represented, stored and transmitted as group of binary bits. This group is also called as **binary code**.

- Binary codes are codes which are represented in binary system with modification from the original ones.

- The types of binary codes are:

- 1) Weighted codes.

- 2) Non-Weighted codes.

- 3) Binary Coded Decimal Code

- 4) Alphanumeric Codes

- 5) Error Detecting Codes

- 6) Error Correcting Codes

## **ADVANTAGES OF BINARY CODES**

Following is the list of advantages that binary code offers.

- Binary codes are suitable for the computer applications.

- Binary codes are suitable for the digital communications.

- Binary codes make the analysis and designing of digital circuits if we use the binary codes.

- Since only 0 & 1 are being used, implementation becomes easy.

## WEIGHTED BINARY CODES

- Weighted binary codes are those binary codes which obey the positional weight principle.

- Each position of the number represents a specific weight.

- Several systems of the codes are used to express the decimal digits 0 through 9.

- In these codes each decimal digit is represented by a group of four bits.

## **NON-WEIGHTED CODES**

- In this type of binary codes, the positional weights are not assigned.

- The examples of non-weighted codes are Excess-3 code and Gray code.

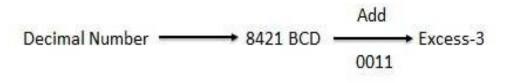

#### Excess-3 code

- The Excess-3 code is also called as XS-3 code. It is nonweighted code used to express decimal numbers.

- The Excess-3 code words are derived from the 8421 BCD code words adding (0011)<sub>2</sub> or (3)10 to each code word in 8421.

## **EXCESS-3 CODE**

• The excess-3 codes are obtained as follows –

#### Example

| Decimal | BCD     | Excess-3   |  |

|---------|---------|------------|--|

|         | 8421    | BCD + 0011 |  |

| 0       | 0 0 0 0 | 0011       |  |

| 1       | 0 0 0 1 | 0 1 0 0    |  |

| 2<br>3  | 0 0 1 0 | 0 1 0 1    |  |

| 3       | 0 0 1 1 | 0 1 1 0    |  |

| 4       | 0 1 0 0 | 0 1 1 1    |  |

| 5       | 0 1 0 1 | 1000       |  |

| 6       | 0 1 1 0 | 1001       |  |

| 7       | 0 1 1 1 | 1010       |  |

| 8       | 1000    | 1011       |  |

| 9       | 1001    | 1 1 0 0    |  |

#### **GRAY CODE**

- It is the non-weighted code and it is not arithmetic codes. That means there are no specific weights assigned to the bit position.

- As only one bit changes at a time so the gray code is called as a unit distance code. The gray code is also called as a cyclic code.

- Gray code cannot be used for arithmetic operation.

| Decimal | BCD     | Gray    |  |  |

|---------|---------|---------|--|--|

| 0       | 0 0 0 0 | 0 0 0 0 |  |  |

| 1       | 0001    | 0 0 0 1 |  |  |

| 2       | 0 0 1 0 | 0 0 1 1 |  |  |

| 3       | 0 0 1 1 | 0 0 1 0 |  |  |

| 4       | 0 1 0 0 | 0 1 1 0 |  |  |

| 5       | 0 1 0 1 | 0 1 1 1 |  |  |

| 6       | 0 1 1 0 | 0 1 0 1 |  |  |

| 7       | 0 1 1 1 | 0 1 0 0 |  |  |

| 8       | 1000    | 1 1 0 0 |  |  |

| 9       | 1001    | 1 1 0 1 |  |  |

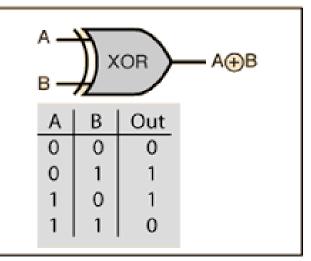

## EXOR OPERATION

s.

5/

Ð

16.4

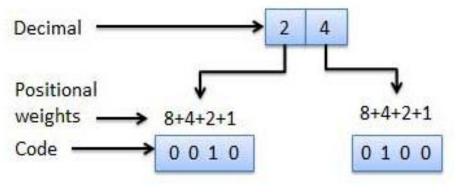

## **BINARY CODED DECIMAL (BCD) CODE**

- In this code each decimal digit is represented by a 4-bit binary number.

- BCD is a way to express each of the decimal digits with a binary code.

- In the BCD, with four bits we can represent sixteen numbers (0000 to 1111).

| Decimal | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---------|------|------|------|------|------|------|------|------|------|------|

| BCD     | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 |

## **BCD CODES**

#### Advantages of BCD Codes

- It is very similar to decimal system.

- We need to remember binary equivalent of decimal numbers 0 to 9 only.

#### **Disadvantages of BCD Codes**

- The addition and subtraction of BCD have different rules.

- The BCD arithmetic is little more complicated.

- BCD needs more number of bits than binary to represent the decimal number. So BCD is less efficient than binary.

## **ALPHANUMERIC CODES**

- The alphanumeric codes are the codes that represent numbers and alphabetic characters.

- Mostly such codes also represent other characters such as symbol and various instructions necessary for conveying information.

- An alphanumeric code should at least represent 10 digits.

- The following three alphanumeric codes are very commonly used for the data representation.

American Standard Code for Information Interchange (ASCII).

Extended Binary Coded Decimal Interchange Code

(EBCDIC).

### **ERROR CODES**

• There are binary code techniques available to detect and correct data during data transmission.

#### **Error detecting codes**

• When data is transmitted from one point to another, there are chances that data may get corrupted. To detect these data errors, we use special codes, which are error detection codes.

#### **Error-correcting codes**

- It not only detect errors, but also correct them. This is used normally in Satellite

- communication, where turn-around delay is very high as is the probability of data getting corrupt.

## **ERROR CODES**

#### Hamming Codes

- Hamming code adds a minimum number of bits to the data transmitted in a noisy channel, to be able to correct every possible one-bit error.

- Two types of parity are:

**Even parity:** Checks if there is an even number of ones; if so, parity bit is zero. When the number of one's is odd then parity bit is set to 1.

**Odd Parity:** Checks if there is an odd number of ones; if so, parity bit is zero. When the number of one's is even then parity bit is set to 1.

## **CODE CONVERSION**

- There are many methods or techniques which can be used to convert code from one format to another.

- > Binary to BCD Conversion

- BCD to Binary Conversion

- BCD to Excess-3

- Excess-3 to BCD

## **BINARY TO BCD CONVERSION**

- **Step 1** -- Convert the binary number to decimal.

- Step 2 -- Convert decimal number to BCD.

Example – convert  $(11101)_2$  to BCD.

Step 1 – Convert the given number to Decimal

| Step   | Binary Number      | Decimal Number                                                                         |

|--------|--------------------|----------------------------------------------------------------------------------------|

| Step 1 | 11101 <sub>2</sub> | $((1\times 2^4) + (1\times 2^3) + (1\times 2^2) + (0\times 2^1) + (1\times 2^0))_{10}$ |

| Step 2 | 11101 <sub>2</sub> | $(16 + 8 + 4 + 0 + 1)_{10}$                                                            |

| Step 3 | 11101 <sub>2</sub> | 29 <sub>10</sub>                                                                       |

Binary Number - 11101<sub>2</sub> = Decimal Number - 29<sub>10</sub>

## **BINARY TO BCD CONVERSION**

• Step 2 – Convert to BCD

| Step   | Decimal Number   | Conversion                          |

|--------|------------------|-------------------------------------|

| Step 1 | 29 <sub>10</sub> | 0010 <sub>2</sub> 1001 <sub>2</sub> |

| Step 2 | 29 <sub>10</sub> | 00101001 <sub>BCD</sub>             |

Result

$(11101)_2 = (00101001)_{BCD}$

## **BCD TO BINARY CONVERSION**

- **Step 1** -- Convert the BCD number to decimal.

- **Step 2** -- Convert decimal to binary.

Example – convert  $(00101001)_{BCD}$  to Binary.

Step 1 - Convert to BCD

| Step   | BCD Number                | Conversion                          |

|--------|---------------------------|-------------------------------------|

| Step 1 | (00101001) <sub>BCD</sub> | 0010 <sub>2</sub> 1001 <sub>2</sub> |

| Step 2 | (00101001) <sub>BCD</sub> | 2 <sub>10</sub> 9 <sub>10</sub>     |

| Step 3 | (00101001) <sub>BCD</sub> | 29 <sub>10</sub>                    |

## **BCD TO BINARY CONVERSION**

• Step 2 - Convert to Binary

Use long division method for decimal to binary conversion. Decimal Number  $-29_{10}$

| Step   | Operation | Result | Remainder |

|--------|-----------|--------|-----------|

| Step 1 | 29 / 2    | 14     | 1         |

| Step 2 | 14 / 2    | 7      | 0         |

| Step 3 | 7/2       | 3      | 1         |

| Step 4 | 3 / 2     | 1      | 1         |

| Step 5 | 1/2       | 0      | 1         |

#### Result

•  $(00101001)_{BCD} = (11101)_2$

### **BCD TO EXCESS-3**

Steps

- Step 1 -- Convert BCD to decimal.

- Step 2 -- Add (3)<sub>10</sub> to this decimal number.

- Step 3 -- Convert into binary to get excess-3 code.

Example - convert (0110)<sub>BCD</sub> to Excess-3.

Step 1 - Convert to decimal

$(0110)_{BCD} = 6_{10}$

Step 2 - Add 3 to decimal

$(6)_{10} + (3)_{10} = (9)_{10}$

Step 3 - Convert to Excess-3

$(9)_{10} = (1001)_2$

Result

$(0110)_{BCD} = (1001)_{XS-3}$

## **EXCESS-3 TO BCD**

Steps

Step 1 -- Subtract (0011)<sub>2</sub> from each 4 bit of excess-3 digit to obtain the corresponding BCD code.

Example - convert (10011010)<sub>XS-3</sub> to BCD.

Given XS-3 number = 1 0 0 1 1 0 1 0 Subtract (0011)<sub>2</sub> = 1 0 0 1 0 1 1 1 BCD = 0 1 1 0 0 1 1 1

Result

$(10011010)_{XS-3} = (01100111)_{BCD}$

## **BINARY CODE CONVERSION**

Example 1: Give the binary, BCD, Excess-3, gray code representations of numbers: 5,8,14.

| Decimal Number | Binary code BCD code Excess-3 |           | Excess-3 code | Gray code |

|----------------|-------------------------------|-----------|---------------|-----------|

| 5              | 0101                          | 0101      | 1000          | 0111      |

| 8              | 1000                          | 1000      | 1011          | 1100      |

| 14             | 1110                          | 0001 0100 | 0100 0111     | 1001      |

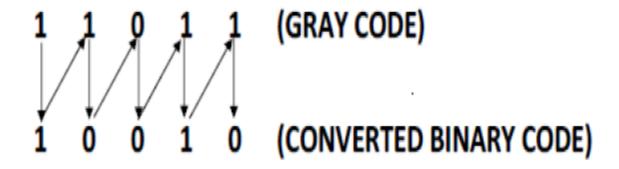

#### **BINARY CODE CONVERSION**

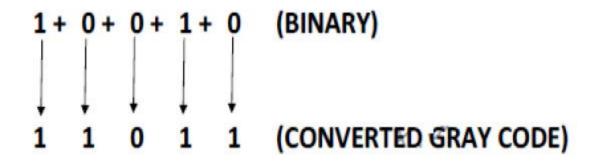

**Example 2: Binary To Gray Code Conversion**

Example 3: Gray code to Binary code

## **BOOLEAN ALGEBRA**

• Boolean algebra is an algebraic structure defined by a set of elements, B, together with two binary operators, + and., provider that the following postulates are satisfied.

#### **Principle of Duality**

- It states that every algebraic expression is deducible from the postulates of Boolean algebra, and it remains valid if the operators & identity elements are interchanged.

- 1. Interchanging the OR and AND operations of the expression.

- 2. Interchanging the 0 and 1 elements of the expression.

- 3. Not changing the form of the variables.

## **BOOLEAN THEOREM**

- The theorems of Boolean algebra can be used to simplify many a complex Boolean expression and also to transform the given expression into a more useful and meaningful equivalent expression.

- The theorems are presented as pairs, with the two theorems in a given pair being the dual of each other.

- These theorems can be very easily verified by the method of perfect induction.

- **T1: Commutative Law**

(a) A + B = B + A(b) A B = B A

#### **T2:** Associative Law

(a) (A + B) + C = A + (B + C)

(b) (A B) C = A (B C)

#### **BOOLEAN THEOREM**

#### T3: Distributive Law

(a) A(B + C) = AB + AC(b) A + (BC) = (A + B)(A + C)

T4: Identity Law (a) A + A = A(b) A A = A

**T5: Negation Law**  $(\overline{A}) = \overline{A}$  and  $(\overline{\overline{A}}) = A$

**T6: Redundancy**

(a) A + A B = A(b) A (A + B) = A

#### Contd,.

T7: Operations with '0' & '1'

(a) 0 + A = A

(b) 1 A = A

(c) 1 + A = 1

(d) 0 A = 0

#### **T8 : Complement laws**

(a)  $\bar{A} + A = 1$ (b)  $\bar{A} \cdot A = 0$

**T9:** (a)

$$A + \overline{AB} = A + B$$

(b) A.  $(\overline{A} + B) = A.B$

### Contd,.

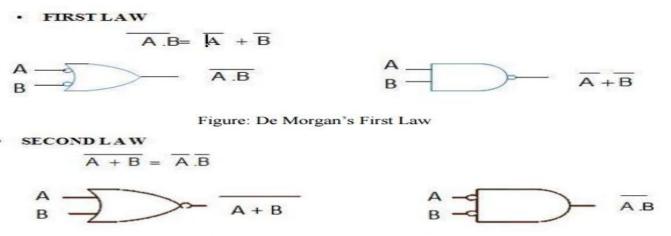

#### **T10: De Morgan's Theorem**

It States that —The complement of the sum of the variables is equal to the product of the complement of each variable This theorem may be expressed by the following Boolean expression.

$$(\overline{A+B}) = \overline{A}.\,\overline{B}$$

It states that the —Complement of the product of variables is equal to the sum of complements of each individual variable.

Boolean expression for this theorem is

$$(\overline{AB}) = \overline{A} + \overline{B}$$

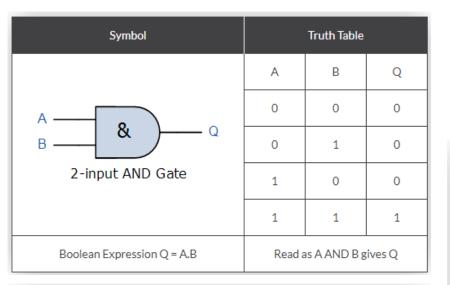

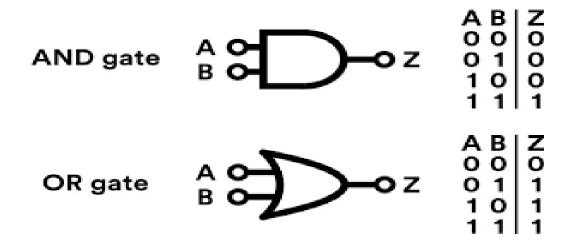

#### GATES

| Symbol Truth Table                                |   |   |       |

|---------------------------------------------------|---|---|-------|

|                                                   | А | В | Q     |

| A                                                 | 0 | 0 | 0     |

| BQ                                                | 0 | 1 | 1     |

| 2-input OR Gate                                   | 1 | 0 | 1     |

|                                                   | 1 | 1 | 1     |

| Boolean Expression Q = A+B Read as A OR B gives Q |   |   | ves Q |

| Symbol                                         | Truth           | Table           |

|------------------------------------------------|-----------------|-----------------|

|                                                | A               | Q               |

|                                                | 0               | 1               |

| Inverter or NOT Gate                           | 1               | 0               |

| Boolean Expression Q = NOT A or $\overline{A}$ | Read as inversi | on of A gives Q |

| Inp | uts | Truth Table Outputs For Each Gate |      |    |     |       |        |  |

|-----|-----|-----------------------------------|------|----|-----|-------|--------|--|

| A   | В   | AND                               | NAND | OR | NOR | EX-OR | EX-NOR |  |

| 0   | 0   | 0                                 | 1    | 0  | 1   | 0     | 1      |  |

| 0   | 1   | 0                                 | 1    | 1  | 0   | 1     | 0      |  |

| 1   | 0   | 0                                 | 1    | 1  | о   | 1     | 0      |  |

| 1   | 1   | 1                                 | 0    | 1  | 0   | 0     | 1      |  |

| Logic Function | Boolean Notation                                                           |  |

|----------------|----------------------------------------------------------------------------|--|

| AND            | A.B                                                                        |  |

| OR             | A+B                                                                        |  |

| NOT            | Ā                                                                          |  |

| NAND           | A.B                                                                        |  |

| NOR            | A+B                                                                        |  |

| EX-OR          | $(A.\overline{B}) + (\overline{A}.B) \text{ or } A \bigoplus B$            |  |

| EX-NOR         | $(A.B) + (\overline{A}.\overline{B}) \text{ or } \overline{A \bigoplus B}$ |  |

## **VERIFICATION OF DEMORGAN'S LAW**

#### **De Morgan's First Theorem states:**

• The complement of a product of variables is equal to the sum of the complements of the individual variables .

#### **De Morgan's Second Theorem states:**

• The complement of sum of variables is equal to the product of the complements of the dividable variables

Figure: De Morgan's Second Law

#### **PROBLEMS**

Example 1: Using theorems, find A+A'B. A + A' B = A 1 + A' B = A (1 + B) + A'B = A + AB + A'B = A + B (A + A')= A + B

#### **Using Truth Table**

| A | B | A+B | A'B | A+A'B |

|---|---|-----|-----|-------|

| 0 | 0 | 0   | 0   | 0     |

| 0 | 1 | 1   | 1   | 1     |

| 1 | 0 | 1   | 0   | 1     |

| 1 | 1 | 1   | 0   | 1     |

### **ORDER OF PRECEDENCE**

- NOT operations have the highest precedence, followed by AND operations, followed by OR operations.

- Brackets can be used as with other forms of algebra.

- e.g. X.Y + Z and X.(Y + Z) are not the same function.

- Truth tables are a means of representing the results of a logic function using a table.

Contd,.

NOT

AND

$\begin{array}{c|cc}

X & F(X) \\

0 & 1 \\

1 & 0

\end{array}$

| X | Y | $\mathbf{F}(\mathbf{X},\mathbf{Y})$ |

|---|---|-------------------------------------|

| 0 | 0 | 0                                   |

| 0 | 1 | 1                                   |

| 1 | 0 | 1                                   |

| 1 | 1 | 1                                   |

OR

### MINTERM AND MAXTERM

- A minterm is the product of N distinct literals where each literal occurs exactly once.

- A maxterm is the sum of N distinct literals where each literal occurs exactly once.

For a two-variable expression, the minterms and maxterms are as follows

| X | Y | Minterm | Maxterm |

|---|---|---------|---------|

| 0 | 0 | X'.Y'   | X+Y     |

| 0 | 1 | X'.Y    | X+Y'    |

| 1 | 0 | X.Y'    | X'+Y    |

| 1 | 1 | X.Y     | X'+Y'   |

#### Contd,.

For a three-variable expression, the minterms and maxterms are as follows

| X | Y | Z | Minterm  | Maxterm  |

|---|---|---|----------|----------|

| 0 | 0 | 0 | X'.Y'.Z' | X+Y+Z    |

| 0 | 0 | 1 | X'.Y'.Z  | X+Y+Z'   |

| 0 | 1 | 0 | X'.Y.Z'  | X+Y'+Z   |

| 0 | 1 | 1 | X'.Y.Z   | X+Y'+Z'  |

| 1 | 0 | 0 | X.Y'.Z'  | X'+Y+Z   |

| 1 | 0 | 1 | X.Y'.Z   | X'+Y+Z'  |

| 1 | 1 | 0 | X.Y.Z'   | X'+Y'+Z  |

| 1 | 1 | 1 | X.Y.Z    | X'+Y'+Z' |

#### **BOOLEAN FUNCTION**

- A Boolean expression is an expression which consists of variables, constants and logical operators which results in true or false.

- A Boolean function is an algebraic form of Boolean expression.

- The different ways of representing a Boolean function is shown below.

- 1. Sum-of-Products (SOP) Form

- 2. Product-of-sums (POS) form

- 3. Canonical forms

#### SOP

- The Sum of Product (SOP) expression comes from the fact that two or more products (AND) are summed (OR) together.

- The outputs from two or more AND gates are connected to the input of an OR gate so that they are effectively OR'ed together to create the final AND-OR logical output.

#### SOP

- The short form of the sum of the product is SOP, and it is one kind of Boolean algebra expression.

- The min term can be defined as, when the minimum combinations of inputs are high then the output will be high.

| X | Y | Z | Min Term (m) |  |

|---|---|---|--------------|--|

| 0 | 0 | 0 | X'Y'Z' = m0  |  |

| 0 | 0 | 1 | X'Y'Z = m1   |  |

| 0 | 1 | 0 | X'Y Z' = m2  |  |

| 0 | 1 | 1 | X'YZ = m3    |  |

| 1 | 0 | 0 | XY'Z'= m4    |  |

| 1 | 0 | 1 | XY'Z = m5    |  |

| 1 | 1 | 0 | XYZ' = m6    |  |

| 1 | 1 | 1 | XYZ = m7     |  |

### SOP

The sum of products is available in three different forms which include the following.

1). Canonical Sum of Products

- 2). Non-Canonical Sum of Products

- 3). Minimal Sum of Products

## **CANONICAL SUM OF PRODUCTS**

- This is a normal form of SOP.

- The expression of the canonical SOP is denoted with sign summation (∑), and the minterms in the bracket are taken when the output is true.

- The truth table of the canonical sum of the product is shown below.

| x | Y | Z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

#### Contd,.

• For the above table, the **canonical SOP form** can be written as

$F = \sum (m1, m2, m3, m5)$

By expanding the above summation we can get the following function.

```

F = m1 + m2 + m3 + m5

```

By substituting the minterms in the above equation we can get the below expression

#### $\mathbf{F} = \mathbf{X'Y'Z} + \mathbf{X'YZ'} + \mathbf{X'YZ} + \mathbf{XY'Z}$

• The product term of the canonical form includes both complemented and non-complimented inputs

## **NON-CANONICAL SUM OF PRODUCTS**

- In the non-canonical sum of product form, the product terms are simplified. For example, let's take the above canonical expression

- F = X'Y'Z + X'YZ' + X'YZ + XY'Z F = X'Y'Z + X'Y (Z'+Z) + XY'ZHere Z'+Z = 1 (Standard function) F = X'Y'Z + X'Y (1) + XY'ZF = X'Y'Z + X'Y + XY'Z

This is still in the form of SOP, but it is the non-canonical form

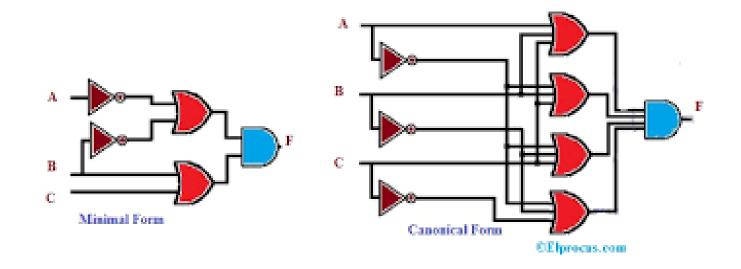

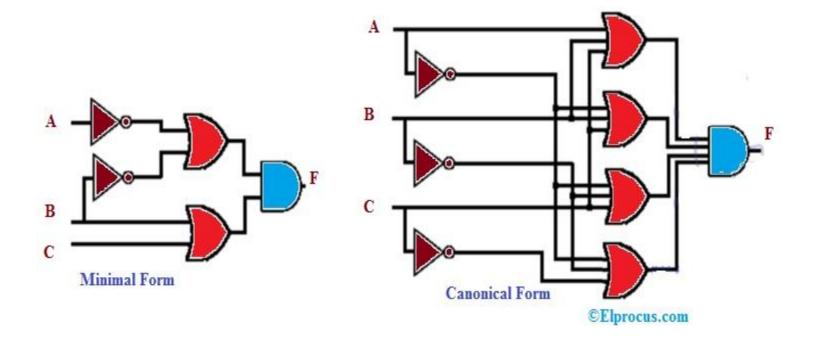

#### MINIMAL SUM OF PRODUCTS

- This is the most simplified expression of the sum of the product, and It is also a type of non-canonical.

- This type of can is made simplified with the Boolean algebraic theorem although it is simply done by using **K-map** (Karnaughmap).

- This form is chosen due to the number of input lines & gates are used in this is minimum.

#### K-MAP

• Let's take an example of canonical form function, and the minimal **Sum of Products K map** is

The expression of this based on the K-map will be

$\mathbf{F} = \mathbf{Y'Z} + \mathbf{X'Y}$

### **SCHEMATIC DESIGN**

• The expression of the sum of product executes two-level AND-OR design, and this design requires a collection of AND gates and one OR gate.

## MINIMAL TO CANONICAL SOP FORM

- Conversion from minimal or any sort of non-canonical form to canonical form is very simple.

- Example of conversion for minimal SOP form is given below.  $\mathbf{F} = \overline{\mathbf{A}}\mathbf{B} + \overline{\mathbf{B}}\mathbf{C}$  (Minimal SOP form)

- The term  $\overline{A}B$  is missing input C. So we will multiply  $\overline{A}B$  with  $(C+\overline{C})$  because  $(C+\overline{C}=1)$ . The term  $\overline{B}C$  is missing input A. so it will be multiplied with  $(A+\overline{A})$

$\mathbf{F} = \overline{\mathbf{A}}\mathbf{B}(\mathbf{C} + \overline{\mathbf{C}}) + \overline{\mathbf{B}}\mathbf{C}(\mathbf{A} + \overline{\mathbf{A}})$

$\mathbf{F} = \overline{\mathbf{A}}\mathbf{B}\mathbf{C} + \overline{\mathbf{A}}\mathbf{B}\overline{\mathbf{C}} + \mathbf{A}\overline{\mathbf{B}}\mathbf{C} + \overline{\mathbf{A}}\overline{\mathbf{B}}\mathbf{C}$  (Canonical SOP)

## **PRODUCT OF SUM(POS)**

- The product of Sum form is a form in which products of different sum terms of inputs are taken.

- These are not arithmetic product and sum but they are logical Boolean AND and OR respectively.

#### Max Term

• Maxterm means the term or expression that is true for a maximum number of input combinations or that is false for only one combination of inputs.

| Α | В | С  | Max term                                           |

|---|---|----|----------------------------------------------------|

| 0 | 0 | 0  | $M_0 = A + B + C$                                  |

| 0 | 0 | 1  | $M_1 = A + B + \overline{C}$                       |

| 0 | 1 | -0 | $M_2 = A + \overline{B} + C$                       |

| 0 | 1 | 1  | M₃=A+B+C                                           |

| 1 | 0 | -0 | M₄ <del>=</del> Ā + B + C                          |

| 1 | 0 | 1  | $M_5 = \overline{A} + B + \overline{C}$            |

| 1 | 1 | 0  | $M_6 = \overline{A} + \overline{B} + C$            |

| 1 | 1 | 1  | $M_7 = \overline{A} + \overline{B} + \overline{C}$ |

### **TYPES OF POS**

The product of the sum is classified into three types which include the following.

- Canonical Product of Sums

- Non Canonical Product of Sums

- Minimal Product of Sums

#### **CANONICAL PRODUCT OF SUM**

- The canonical POS is also named as a product of max term.

- The expression this is denoted by ∏ and the max terms in the bracket are taken when the output is false.

| x | Y | z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

## Contd,.

• For the above table, the canonical POS can be written as

#### $\mathbf{F} = \prod (\mathbf{M0}, \mathbf{M4}, \mathbf{M6}, \mathbf{M7})$

By expanding the above equation we can get the following function.

#### F = M0, M4, M6, M7

By substituting the max terms in the above equation we can get the below expression

F = (X+Y+Z) (X'+Y+Z)(X'+Y'+Z)(X'+Y'+Z')

The product term of the canonical form includes both complemented and non-complimented inputs

## **NON – CANONICAL PRODUCT OF SUM**

The expression of the product of sum (POS) is not in normal form is named as non-canonical form. For example, let's take the above expression F = (X+Y+Z) (X'+Y+Z)(X'+Y'+Z)(X'+Y'+Z') F = (Y+Z) (X'+Y+Z) (X'+Y'+Z')

Similar although reversed terms remove from two Max terms & forms only term to show it here is an instance.

= (X+Y+Z) (X'+Y+Z)= XX'+XY+XZ+X'Y+YY+YZ+X'Z+YZ+ZZ = 0+XY+XZ+X'Y+YY+YZ+X'Z+YZ+Z = X (Y+Z) + X' (Y+Z) + Y(1+Z) +Z = (Y+Z) (X+X') + Y (1) +Z = (Y+Z) (0) +Y+Z = Y+Z

The above expression is in the form of non-canonical.

## MINIMAL PRODUCT OF SUM

- This type of can is made simplified with the Boolean algebraic theorems although it is simply done by using K-map (Karnaugh map).

- Let's take an example of canonical form function, and the **Product** of sums K map is

• POS K-mapThe expression of this based on the K-map will be  $\mathbf{F} = (\mathbf{Y} + \mathbf{Z}) (\mathbf{X'} + \mathbf{Y'})$

### **SCHEMATIC DESIGN**

• The expression of the product of the sum executes two levels OR- AND design and this design requires a collection of OR gates and one AND gate.

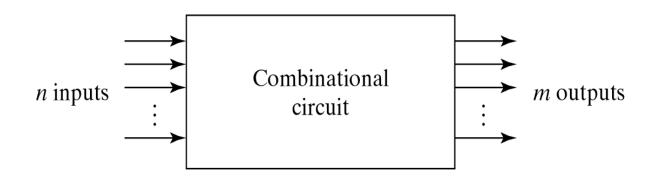

#### **UNIT-2 COMBINATIONAL CIRCUITS**

## **Combinational Logic**

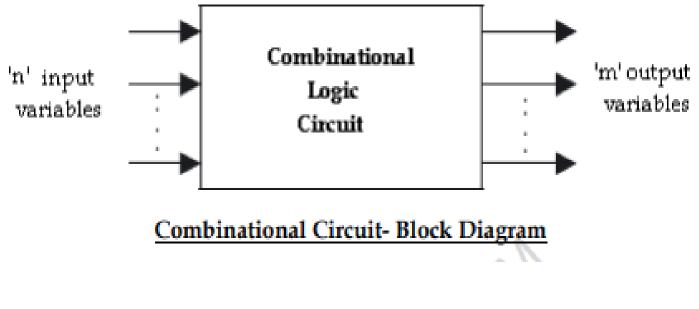

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

Fig. 4-1 Block Diagram of Combinational Circuit

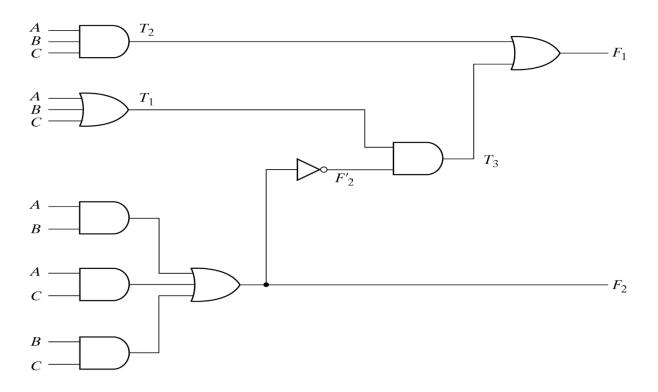

# 4-2. Analysis procedure

Ι.

To obtain the output Boolean functions from a logic diagram, proceed as follows:

- Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions for each gate output.

- Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

# 4-2. Analysis procedure

Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

Example

$F_2 = AB + AC + BC; T_1 = A + B + C;$   $F_1 = T_3 + T_2$  $F_1 = T_3 + T_2 = F_2'T_1 + ABC = A'BC' + A'B'C + AB'C' + ABC$

Fig. 4-2 Logic Diagram for Analysis Example

## Derive truth table from logic diagram

• We can derive the truth table in Table 4-1 by using the circuit of Fig.4-2.

Table 4-1

Truth Table for the Logic Diagram of Fig. 4-2

| A | В | с | F <sub>2</sub> | F <sub>2</sub> | T <sub>1</sub> | T <sub>2</sub> | T <sub>3</sub> | F <sub>1</sub> |

|---|---|---|----------------|----------------|----------------|----------------|----------------|----------------|

| 0 | 0 | 0 | 0              | 1              | 0              | 0              | 0              | 0              |

| 0 | 0 | 1 | 0              | 1              | 1              | 0              | 1              | 1              |

| 0 | 1 | 0 | 0              | 1              | 1              | 0              | 1              | 1              |

| 0 | 1 | 1 | 1              | 0              | 1              | 0              | 0              | 0              |

| 1 | 0 | 0 | 0              | 1              | 1              | 0              | 1              | 1              |

| 1 | 0 | 1 | 1              | 0              | 1              | 0              | 0              | 0              |

| 1 | 1 | 0 | 1              | 0              | 1              | 0              | 0              | 0              |

| 1 | 1 | 1 | 1              | 0              | 1              | 1              | 0              | 1              |

101

# 4-3. Design procedure

Table4-2 is a Code-Conversion example, first, we can list the relation of the BCD and Excess-3 codes in the truth table.

| Input BCD |   |   | Out | Output Excess- |   |   |   |

|-----------|---|---|-----|----------------|---|---|---|

| A         | B | с | D   | w              | x | y | z |

| 0         | 0 | 0 | 0   | 0              | 0 | 1 | 1 |

| 0         | 0 | 0 | 1   | 0              | 1 | 0 | 0 |

| 0         | 0 | 1 | 0   | 0              | 1 | 0 | 1 |

| 0         | 0 | 1 | 1   | 0              | 1 | 1 | 0 |

| 0         | 1 | 0 | 0   | 0              | 1 | 1 | 1 |

| 0         | 1 | 0 | 1   | 1              | 0 | 0 | 0 |

| 0         | 1 | 1 | 0   | 1              | 0 | 0 | 1 |

| 0         | 1 | 1 | 1   | 1              | 0 | 1 | 0 |

| 1         | 0 | 0 | 0   | 1              | 0 | 1 | 1 |

| 1         | 0 | 0 | 1   | 1              | 1 | 0 | 0 |

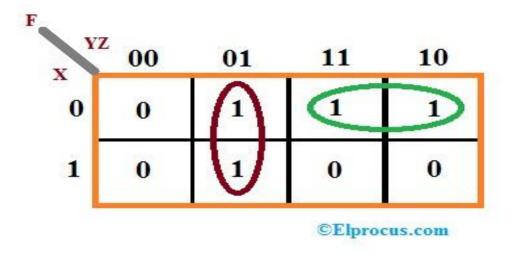

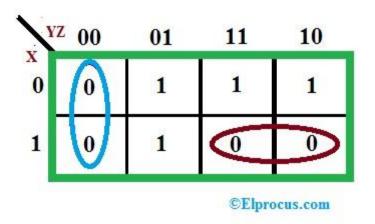

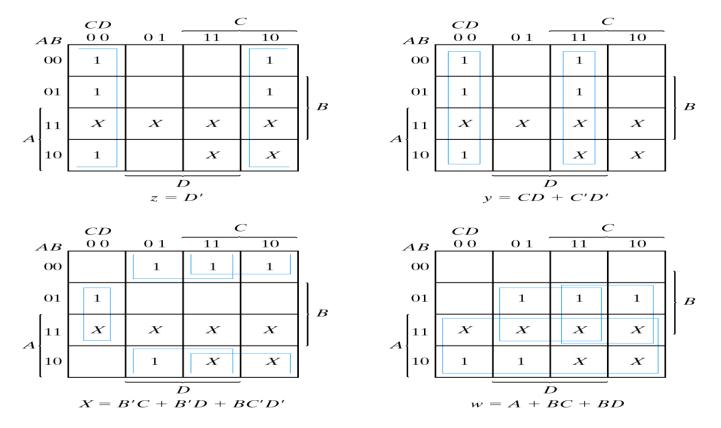

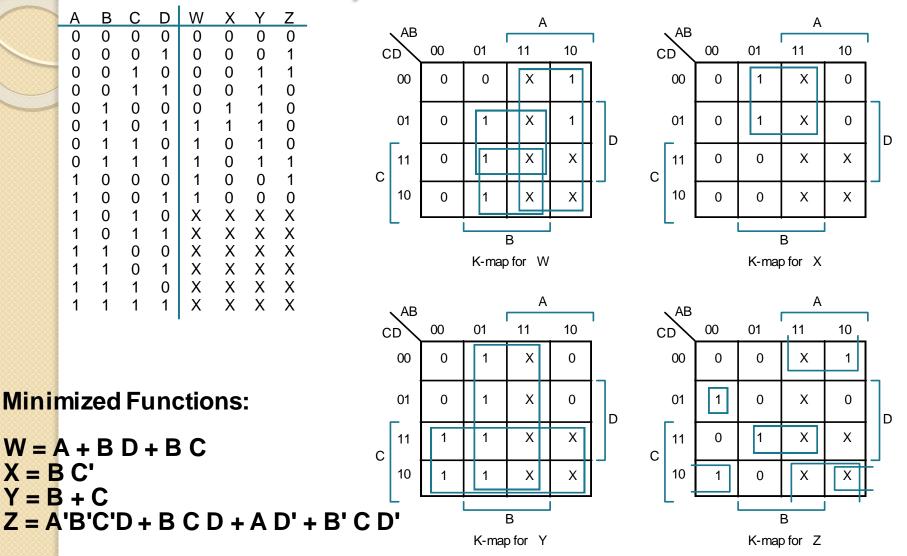

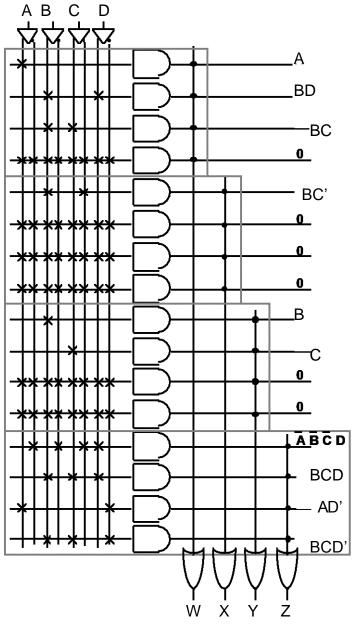

## Karnaugh map

For each symbol of the Excess-3 code, we use I's to draw the map for simplifying Boolean function.

Fig. 4-3 Maps for BCD to Excess-3 Code Converter

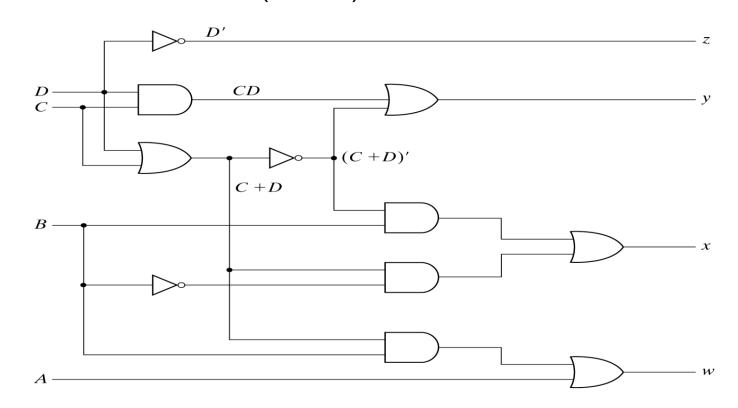

## Circuit implementation

```

z = D'; y = CD + C'D' = CD + (C + D)'

x = B'C + B'D + BC'D' = B'(C + D) + B(C + D)'

w = A + BC + BD = A + B(C + D)

```

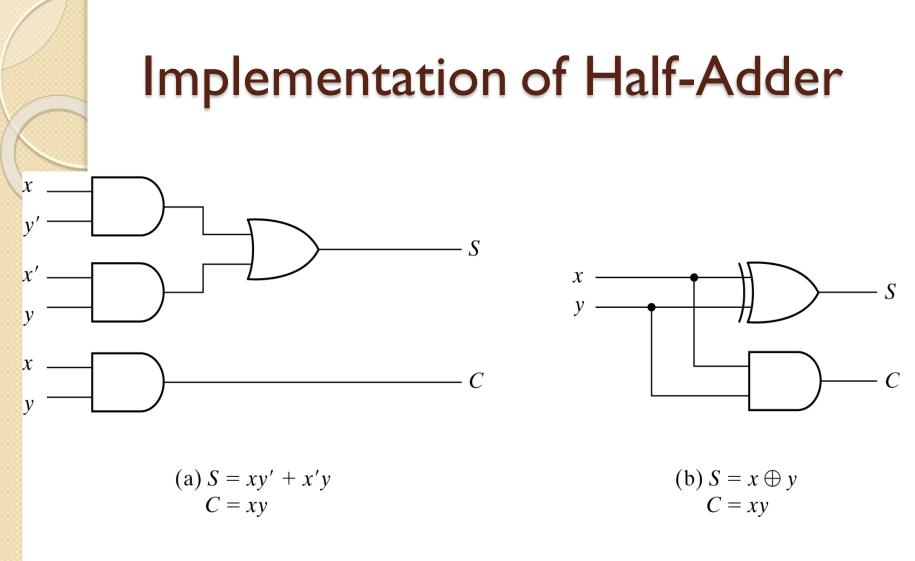

# 4-4. Binary Adder-Subtractor

A combinational circuit that performs the addition of two bits is called a half adder.

• The truth table for the half adder is listed below:

| у | с | S                 |

|---|---|-------------------|

| 0 | 0 | 0                 |

| 1 | 0 | 1                 |

| 0 | 0 | 1                 |

| 1 | 1 | 0                 |

|   | 1 | 0 0<br>1 0<br>0 0 |

| Та | ble  | 4-3  |   |

|----|------|------|---|

| На | lf A | dder | , |

S: Sum C: Carry

S = x'y + xy'C = xy

Fig. 4-5 Implementation of Half-Adder

## Full-Adder

• One that performs the addition of three bits(two significant bits and a previous carry) is a full adder.

#### Table 4-4 Full Adder

| x | У | z | С | 5 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

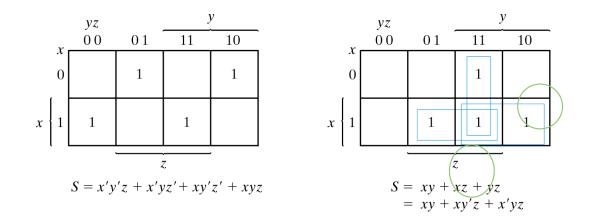

# Simplified Expressions

Fig. 4-6 Maps for Full Adder

С

S = x'y'z + x'yz' + xy'z' + xyzC = xy + xz + yz

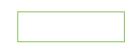

Fig. 4-7 Implementation of Full Adder in Sum of Products

# Another implementation

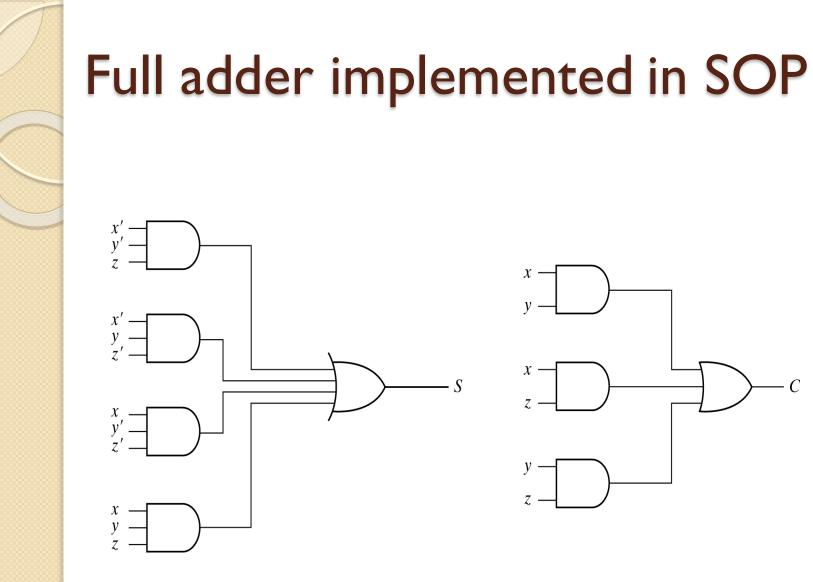

• Full-adder can also implemented with two half adders and one OR gate (Carry Look-Ahead adder).

$$S = z \bigoplus (x \bigoplus y)$$

= z'(xy' + x'y) + z(xy' + x'y)'

= xy'z' + x'yz' + xyz + x'y'z

$$C = z(xy' + x'y) + xy = xy'z + x'yz + xy$$

Fig. 4-8 Implementation of Full Adder with Two Half Adders and an OR Gate

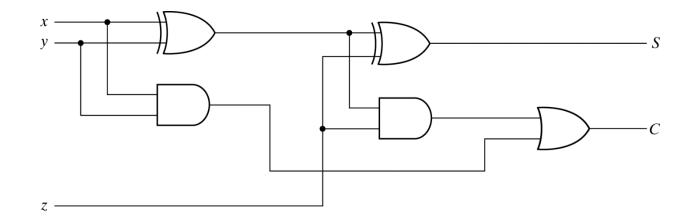

# Binary adder

#### This is also called

Ripple Carry Adder ,because of the construction with full adders are connected in cascade.

| Subscript i: | 3 | 2 | 1 | 0 |                   |

|--------------|---|---|---|---|-------------------|

| Input carry  | 0 | 1 | 1 | 0 | $C_i$             |

| Augend       | 1 | 0 | 1 | 1 | $A_i$             |

| Addend       | 0 | 0 | 1 | 1 | $B_i$             |

| Sum          | 1 | 1 | 1 | 0 | Si                |

| Output carry | 0 | 0 | 1 | 1 | $S_i$<br>$C_{i+}$ |

# **Carry Propagation**

Fig.4-9 causes a unstable factor on carry bit, and produces a longest propagation delay.

The signal from C<sub>i</sub> to the output carry C<sub>i+1</sub>, propagates through an AND and OR gates, so, for an n-bit RCA, there are 2n gate levels for the carry to propagate from input to output.

# Carry Propagation

- Because the propagation delay will affect the output signals on different time, so the signals are given enough time to get the precise and stable outputs.

- The most widely used technique employs the principle of carry look-ahead to improve the speed of the algorithm.

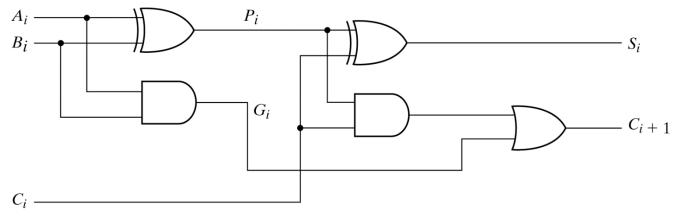

Fig. 4-10 Full Adder with P and G Shown

# **Boolean functions**

$P_i = A_i \oplus B_i$  steady state value  $G_i = A_i B_i$  steady state value

Output sum and carry

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_iC_i$$

G<sub>i</sub> : carry generate P<sub>i</sub> : carry propagate

$$C_{0} = input carry$$

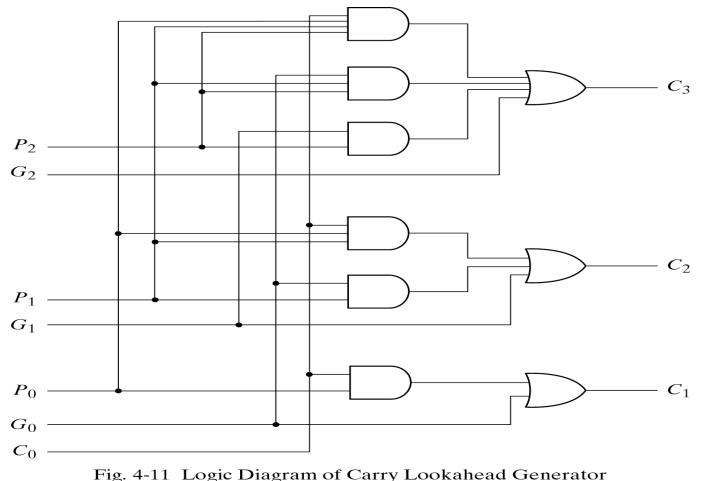

$$C_{1} = G_{0} + P_{0}C_{0}$$

$$C_{2} = G_{1} + P_{1}C_{1} = G_{1} + P_{1}G_{0} + P_{1}P_{0}C_{0}$$

$$C_{3} = G_{2} + P_{2}C_{2} = G_{2} + P_{2}G_{1} + P_{2}P_{1}G_{0} + P_{2}P_{1}P_{0}C_{0}$$

C<sub>3</sub> does not have to wait for C<sub>2</sub> and C<sub>1</sub> to propagate.

# Logic diagram of carry look-ahead generator

• C<sub>3</sub> is propagated at the same time as C<sub>2</sub> and C<sub>1</sub>.

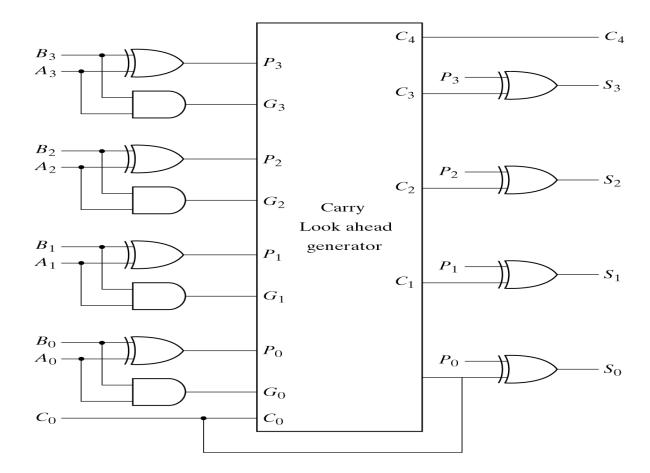

#### 4-bit adder with carry lookahead

Delay time of n-bit CLAA = XOR + (AND + OR) + XOR

Fig. 4-12 4-Bit Adder with Carry Lookahead

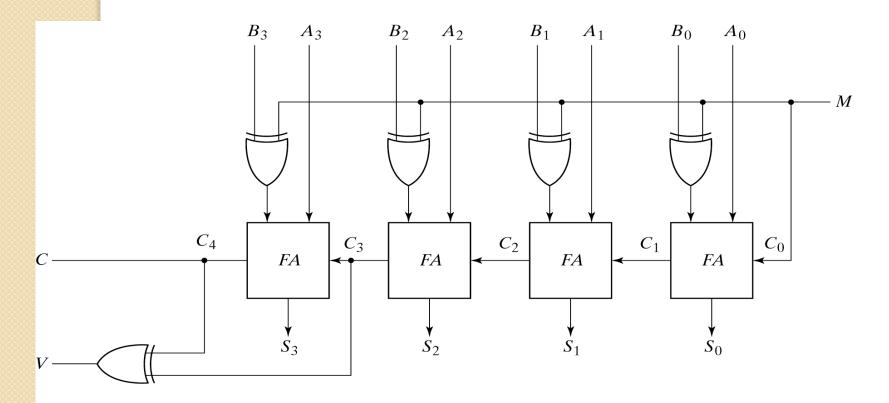

# Binary subtractor

$M = I \rightarrow subtractor \quad ; M = 0 \rightarrow adder$

Fig. 4-13 4-Bit Adder Subtractor

It is worth noting Fig.4-13 that binary numbers in the signed-

complement system are added and subtracted by the same basic addition and subtraction rules as unsigned numbers.

Overflow is a problem in digital computers because the number of bits that hold the number is finite and a result that contains

n+ I bits cannot be accommodated.

# Overflow on signed and unsigned

When two unsigned numbers are added, an overflow is detected from the end carry out of the MSB position.

- When two signed numbers are added, the sign bit is treated as part of the number and the end carry does not indicate an overflow.

- An overflow cann't occur after an addition if one number is positive and the other is negative.

- An overflow may occur if the two numbers added are both positive or both negative.

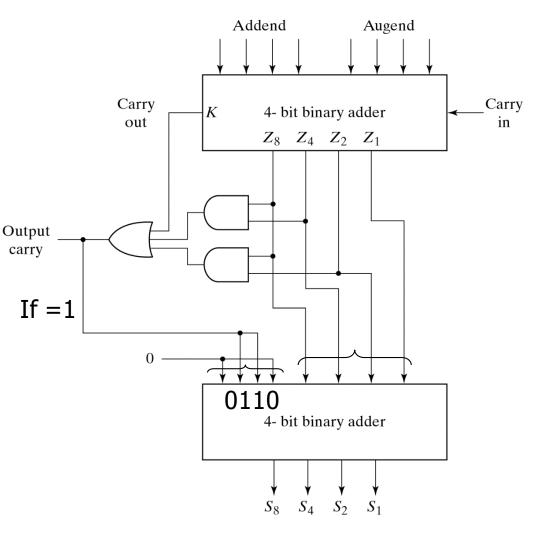

# 4-5 Decimal adder

#### BCD adder can't exceed 9 on each input digit. K is the carry.

#### Table 4-5 Derivation of BCD Adder

| Decima |                       | n  | CD Sur | В              |   |    | m              | nary Su | Bir            |   |

|--------|-----------------------|----|--------|----------------|---|----|----------------|---------|----------------|---|

|        | <i>S</i> <sub>1</sub> | Sz | 54     | S <sub>8</sub> | с | Z1 | Z <sub>2</sub> | Z4      | Z <sub>8</sub> | к |

| 0      | 0                     | 0  | 0      | 0              | 0 | 0  | 0              | 0       | 0              | 0 |

| 1      | 1                     | 0  | 0      | 0              | 0 | 1  | 0              | 0       | 0              | 0 |

| 2      | 0                     | 1  | 0      | 0              | 0 | 0  | 1              | 0       | 0              | 0 |

| 3      | 1                     | 1  | 0      | 0              | 0 | 1  | 1              | 0       | 0              | 0 |

| 4      | 0                     | 0  | 1      | 0              | 0 | 0  | 0              | 1       | 0              | 0 |

| 5      | 1                     | 0  | 1      | 0              | 0 | 1  | 0              | 1       | 0              | 0 |

| 6      | 0                     | 1  | 1      | 0              | 0 | 0  | 1              | 1       | 0              | 0 |

| 7      | 1                     | 1  | 1      | 0              | 0 | 1  | 1              | 1       | 0              | 0 |

| 8      | 0                     | 0  | 0      | 1              | 0 | 0  | 0              | 0       | 1              | 0 |

| 9      | 1                     | 0  | 0      | 1              | 0 | 1  | 0              | 0       | 1              | 0 |

| 10     | 0                     | 0  | 0      | 0              | 1 | 0  | 1              | 0       | 1              | 0 |

| 11     | 1                     | 0  | 0      | 0              | 1 | 1  | 1              | 0       | 1              | 0 |

| 12     | 0                     | 1  | 0      | 0              | 1 | 0  | 0              | 1       | 1              | 0 |

| 13     | 1                     | 1  | 0      | 0              | 1 | 1  | 0              | 1       | 1              | 0 |

| 14     | 0                     | 0  | 1      | 0              | 1 | 0  | 1              | 1       | 1              | 0 |

| 15     | 1                     | 0  | 1      | 0              | 1 | 1  | 1              | 1       | 1              | 0 |

| 16     | 0                     | 1  | 1      | 0              | 1 | 0  | 0              | 0       | 0              | 1 |

| 17     | 1                     | 1  | 1      | 0              | 1 | 1  | 0              | 0       | 0              | 1 |

| 18     | 0                     | 0  | 0      | 1              | 1 | 0  | 1              | 0       | 0              | 1 |

| 19     | 1                     | 0  | 0      | 1              | 1 | 1  | 1              | 0       | 0              | 1 |

| 120    |                       |    |        |                |   |    |                |         |                |   |

# Rules of BCD adder

- When the binary sum is greater than 1001, we obtain a non-valid

BCD representation.

- The addition of binary 6(0110) to the binary sum converts it to the correct BCD representation and also produces an output carry as required.

- To distinguish them from binary 1000 and 1001, which also have a I in position  $Z_8$ , we specify further that either  $Z_4$  or  $Z_2$  must have a I.

$$C = K + Z_8 Z_4 + Z_8 Z_2$$

# Implementation of BCD adder

- A decimal parallel adder that adds n decimal digits needs n BCD adder stages.

- The output carry from one stage must

be connected to the input carry of the next higher-order

stage.

Fig. 4-14 Block Diagram of a BCD Adder 122

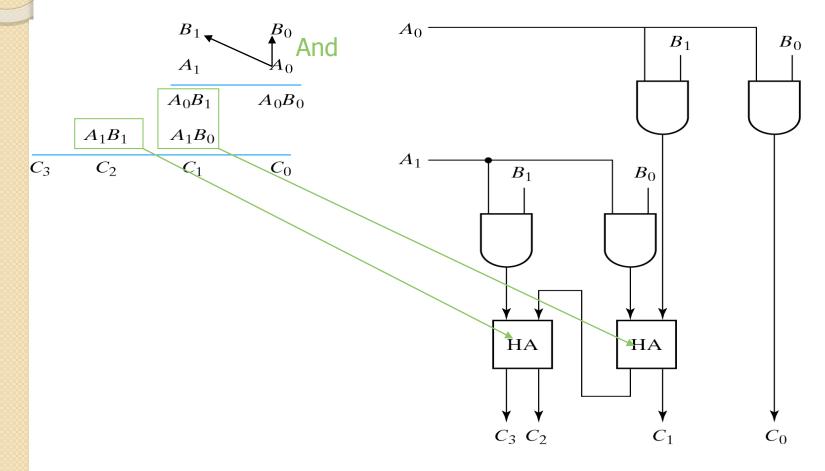

# 4-6. Binary multiplier

Usually there are more bits in the partial products and it is necessary to use adders to produce the sum of the partial products.

Fig. 4-15 2-Bit by 2-Bit Binary Multiplier

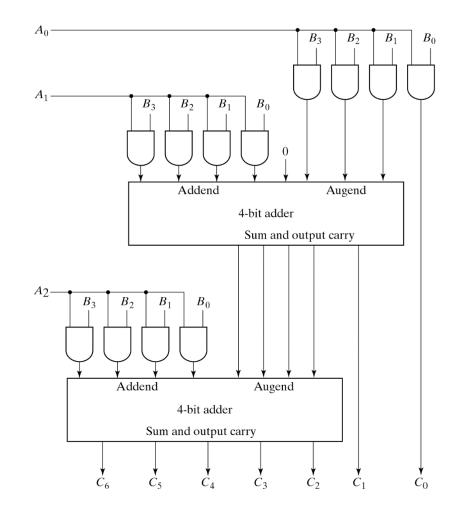

# 4-bit by 3-bit binary multiplier

For J multiplier bits and K

multiplicand bits we need (J X

K) AND gates and (J - I) Kbit adders to produce a

product of J+K bits.

K=4 and J=3, we need 12

AND gates and two 4-bit adders.

Fig. 4-16 4-Bit by 3-Bit Binary Multiplier

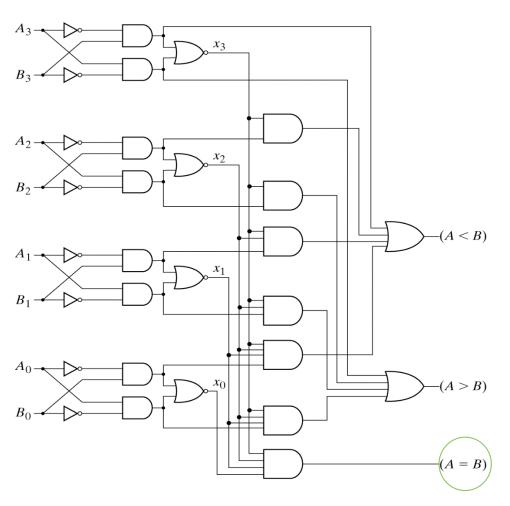

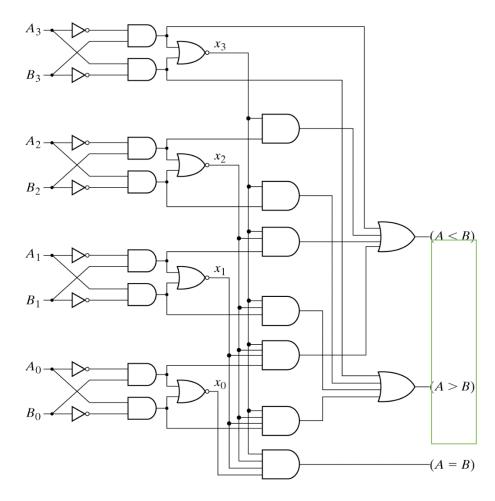

# 4-7. Magnitude comparator

The equality relation of each pair of bits can be expressed logically with an exclusive-NOR function as:

$$A = A_3 A_2 A_1 A_0; B = B_3 B_2 B_1 B_0$$

$$x_i = A_i B_i + A_i B_i$$

for i = 0, 1, 2, 3

$$(\mathsf{A} = \mathsf{B}) = \mathsf{x}_3 \mathsf{x}_2 \mathsf{x}_1 \mathsf{x}_0$$

Fig. 4-17 4-Bit Magnitude Comparator

# Magnitude comparator

We inspect the relative magnitudes of pairs of MSB. If equal, we compare the next lower significant pair of digits until a pair of unequal digits is reached.

If the corresponding digit of A is I and that of B is 0, we conclude that A>B.

(A > B) = $A_3B'_3 + x_3A_2B'_2 + x_3x_2A_1B'_1 + x_3x_2x_1A_0B'_0$ (A < B) = $A'_2B'_3 + x_3A_2B'_2 + x_3x_2A_1B'_1 + x_3x_2x_1A_0B'_0$  $(A < B) = A'_2B'_3 + x_3A_2B'_2 + x_3A_2B'_2 + x_3A_2B'_1 + x_3A_2B'_2 + x_3A_2B'_2 + x_3A_2B'_1 + x_3A_2B'_2 + x_3A_2B'_1 + x_3A_2B'_2 + x_3A_2B'_2 + x_3A_2B'_1 + x_3A_2B'_2 + x_3A_2B'_2 + x_3A_2B'_1 + x_3A_2B'_2 + x_3A_2B'_3 + x$

$A'_{3}B_{3} + x_{3}A'_{2}B_{2} + x_{3}x_{2}A'_{1}B_{1} + x_{3}x_{2}x_{1}A'_{0}B_{0}$

Fig. 4-17 4-Bit Magnitude Comparator

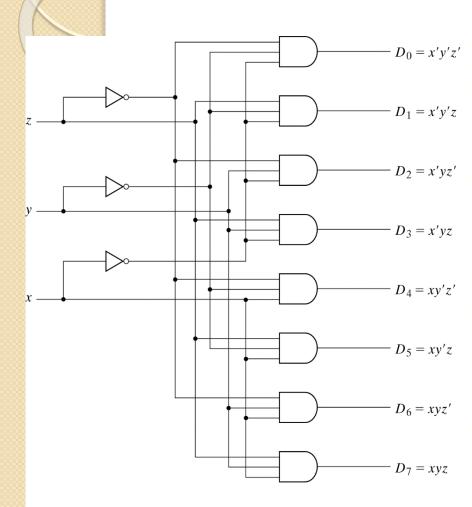

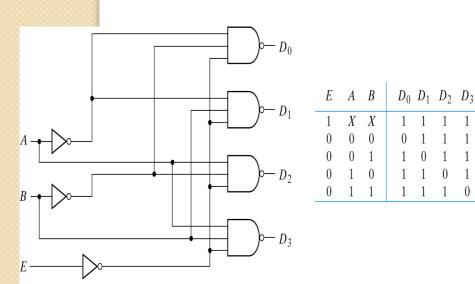

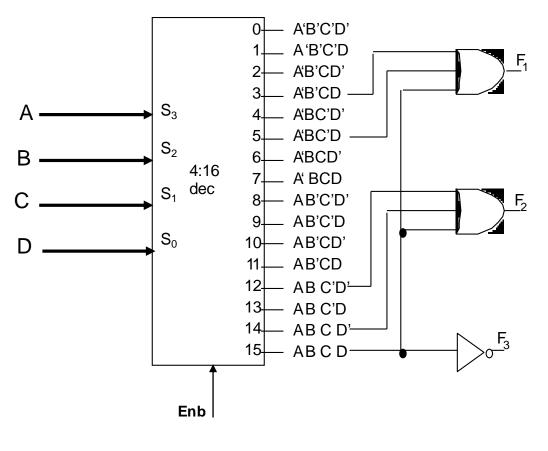

# 4-8. Decoders

- The decoder is called n-to-m-line decoder, where m≤2<sup>n</sup>.

- the decoder is also used in conjunction with other code converters such as a BCD-toseven\_segment decoder.

- 3-to-8 line decoder: For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1.

### Implementation and truth table

Table 4-6

| Inputs |   |   |    |    | Out | puts |    |    |    |    |

|--------|---|---|----|----|-----|------|----|----|----|----|

| X      | y | l | Do | Dı | D2  | D3   | D4 | Ds | D, | Dy |

| 0      | 0 | 0 | 1  | 0  | 0   | 0    | 0  | 0  | 0  | 0  |

| 0      | 0 | 1 | 0  | 1  | 0   | 0    | 0  | 0  | 0  | 0  |

| 0      | I | 0 | 0  | 0  | 1   | 0    | 0  | 0  | 0  | 0  |

| 0      | 1 | 1 | 0  | 0  | 0   | 1    | 0  | 0  | 0  | 0  |

| 1      | 0 | 0 | 0  | 0  | 0   | 0    | 1  | 0  | 0  | 0  |

| 1      | 0 | 1 | 0  | 0  | 0   | 0    | 0  | 1  | 0  | 0  |

| 1      | 1 | 0 | 0  | 0  | 0   | 0    | 0  | 0  | 1  | 0  |

| 1      | 1 | 1 | 0  | 0  | 0   | 0    | 0  | 0  | 0  | ١  |

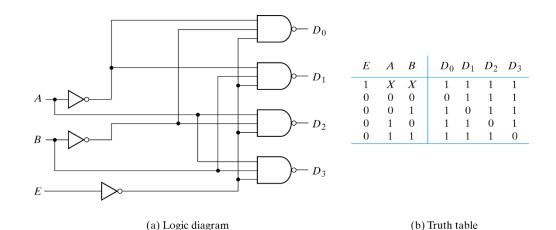

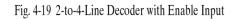

# Decoder with enable input

Some decoders are constructed with NAND gates, it becomes more economical to generate the decoder minterms in their complemented form.

As indicated by the truth table , only one output can be equal to 0 at any given time, all other outputs are equal to 1.

Fig. 4-19 2-to-4-Line Decoder with Enable Input

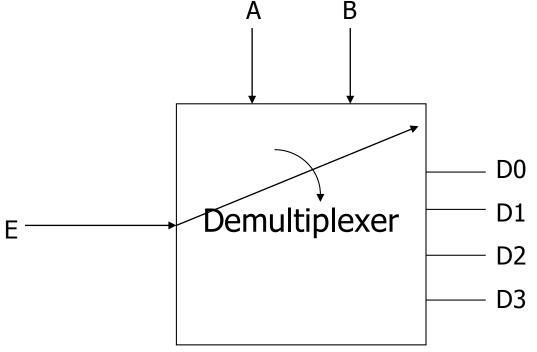

# Demultiplexer

• A decoder with an enable input is referred to as a decoder/demultiplexer.

The truth table of demultiplexer is the same with decoder.

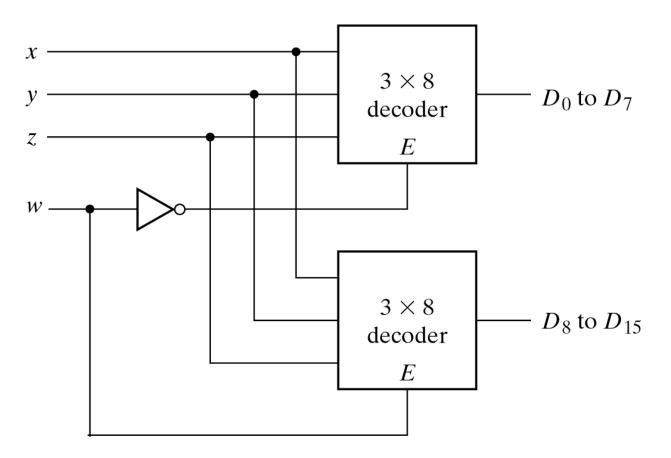

#### 3-to-8 decoder with enable implement the 4-to-16 decoder

Fig. 4-20  $4 \times 16$  Decoder Constructed with Two  $3 \times 8$  Decoders

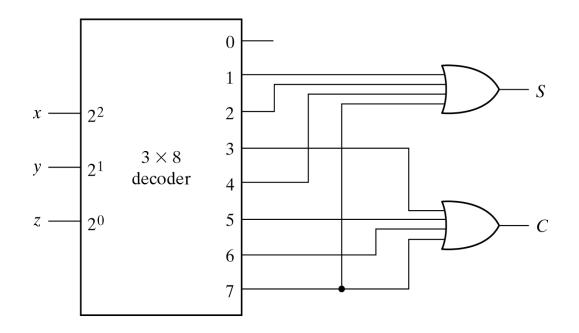

# Implementation of a Full Adder with a Decoder

From table 4-4, we obtain the functions for the combinational circuit in sum of minterms:

$S(x, y, z) = \sum (1, 2, 4, 7)$ C(x, y, z) = \sum (3, 5, 6, 7)

Fig. 4-21 Implementation of a Full Adder with a Decoder

#### 4-9. Encoders

An encoder is the inverse operation of a decoder. We can derive the Boolean functions by table 4-7

> $z = D_1 + D_3 + D_5 + D_7$   $y = D_2 + D_3 + D_6 + D_7$  $x = D_4 + D_5 + D_6 + D_7$

Table 4-7

Truth Table of Octal-to-Binary Encoder

| Inp   | puts  |       |       |       |       |       |       | Outputs |   |   |  |

|-------|-------|-------|-------|-------|-------|-------|-------|---------|---|---|--|

| $D_0$ | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ | x       | у | z |  |

| 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0       | 0 | 0 |  |

| 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0       | 0 | 1 |  |

| 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0       | 1 | 0 |  |

| 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0       | 1 | 1 |  |

| 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1       | 0 | 0 |  |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 1       | 0 | 1 |  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1       | 1 | 0 |  |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1       | 1 | 1 |  |

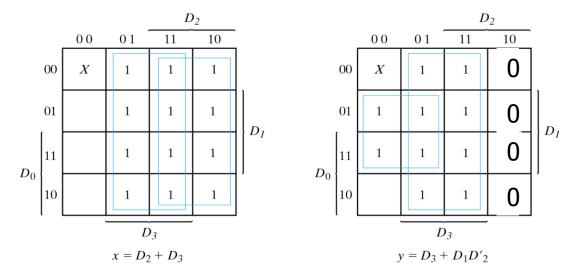

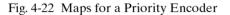

# Priority encoder

- If two inputs are active simultaneously, the output produces an undefined combination. We can establish an input priority to ensure that only one input is encoded.

- Another ambiguity in the octal-to-binary encoder is that an output with all 0's is generated when all the inputs are 0; the output is the same as when  $D_0$  is equal to 1.

- The discrepancy tables on Table 4-7 and Table 4-8 can resolve aforesaid condition by providing one more output to indicate that at least one input is equal to 1.

# **Priority encoder**

V=0→no valid inputs V=1→valid inputs

X's in output columns represent don t-care conditions X's in the input columns are useful for representing a truth table in condensed form. Instead of listing all 16 minterms of four variables.

### Table 4-8 Truth Table of a Priority Encoder

|    | Inp | uts |                | ( | Dutput | s |

|----|-----|-----|----------------|---|--------|---|

| Do | Dı  | D2  | D <sub>3</sub> | x | y      | V |

| 0  | 0   | 0   | 0              | X | X      | 0 |

| 1  | 0   | 0   | 0              | 0 | 0      | 1 |

| X  | 1   | 0   | 0              | 0 | 1      | 1 |

| X  | X   | 1   | 0              | 1 | 0      | 1 |

| X  | X   | X   | 1              | 1 | 1      | 1 |

# 4-input priority encoder

Implementation of table 4-8

$x = D_{2} + D_{3}$ y = D\_{3} + D\_{1}D'\_{2} V = D\_{0} + D\_{1} + D\_{2} + D\_{3}

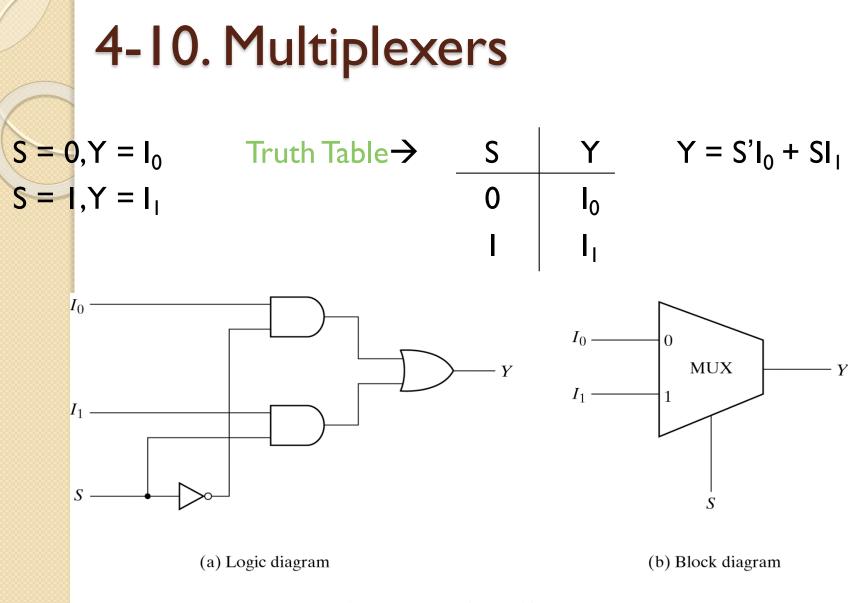

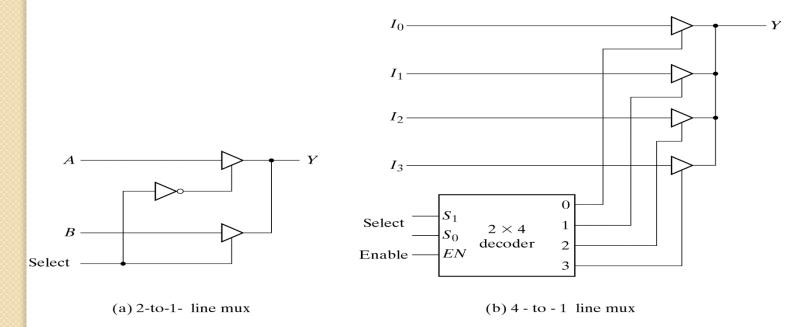

Fig. 4-24 2-to-1-Line Multiplexer

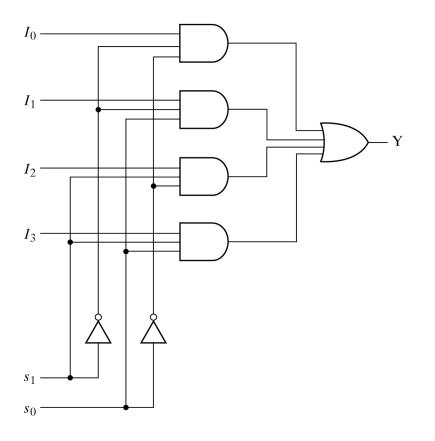

# 4-to-I Line Multiplexer

| $s_1$ | $s_0$ | Y              |

|-------|-------|----------------|

| 0     | 0     | $I_0$          |

| 0     | 1     | $I_0$<br>$I_1$ |

| 1     | 0     | $I_2$<br>$I_3$ |

| 1     | 1     | $I_3$          |

(b) Function table

(a) Logic diagram

Fig. 4-25 4-to-1-Line Multiplexer

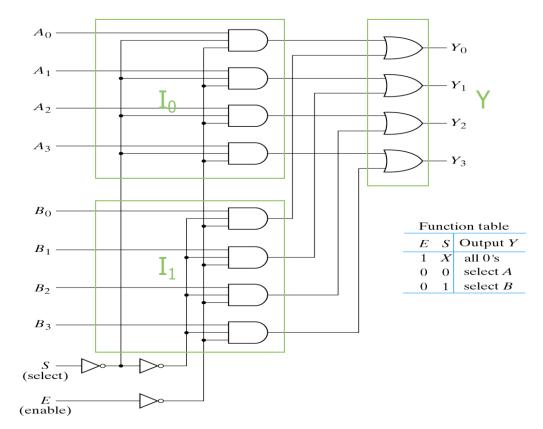

### Quadruple 2-to-1 Line Multiplexer

Multiplexer circuits can be combined with common selection inputs to provide multiple-bit selection logic. Compare with Fig4-24.

Fig. 4-26 Quadruple 2-to-1-Line Multiplexer

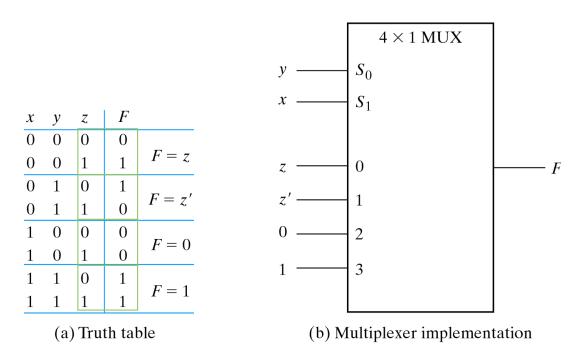

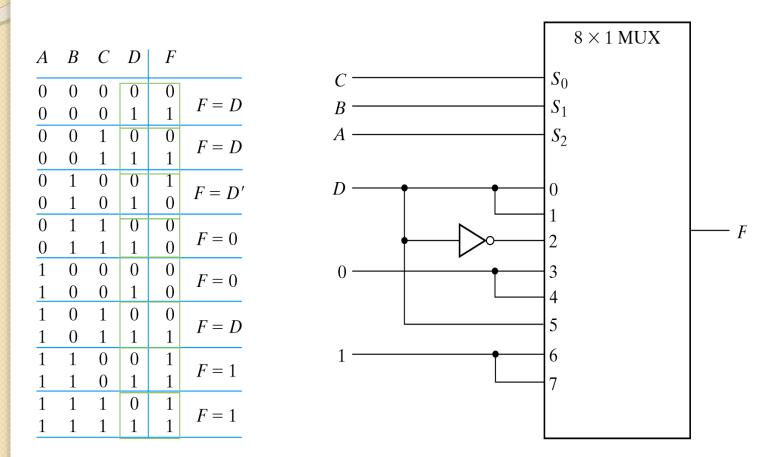

#### **Boolean function implementation**

A more efficient method for implementing a Boolean function of n variables with a multiplexer that has n-1 selection inputs.

$$F(x, y, z) = \Sigma(1, 2, 6, 7)$$

Fig. 4-27 Implementing a Boolean Function with a Multiplexer

#### 4-input function with a multiplexer

$F(A, B, C, D) = \Sigma(1, 3, 4, 11, 12, 13, 14, 15)$

Fig. 4-28 Implementing a 4-Input Function with a Multiplexer

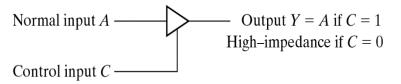

# **Three-State Gates**

A multiplexer can be constructed with three-state gates.

Fig. 4-29 Graphic Symbol for a Three-State Buffer

Fig. 4-30 Multiplexers with Three-State Gates

# 4-11. HDL for combinational circuits

- A module can be described in any one of the following modeling techniques:

- I. Gate-level modeling using instantiation of primitive gates and user-defined modules.

- 2. Dataflow modeling using continuous assignment statements with keyword assign.

- 3. Behavioral modeling using procedural assignment statements with keyword always.

# Gate-level Modeling

A circuit is specified by its logic gates and their interconnection.

Verilog recognizes 12 basic gates as predefined primitives.

• The logic values of each gate may be 1,0, x(unknown), z(high-impedance).

| and | 0 | 1 | х | z | or  | 0   | 1  | x   | Z   |

|-----|---|---|---|---|-----|-----|----|-----|-----|

| 0   | 0 | 0 | 0 | 0 | 0   | 0   | 1  | x   | x   |

| 1   | 0 | 1 | x | x | 1   | 1   | 1  | 1   | 1   |

| х   | 0 | х | х | х | x   | x   | 1  | х   | x   |

| z   | 0 | x | x | x | z   | x   | 1  | х   | x   |

| xor | 0 | 1 | x | z | not | inp | ut | out | put |

| 0   | 0 | 1 | х | x |     | 0   |    | 1   |     |

| 1   | 1 | 0 | x | x |     | 1   |    | 0   | )   |

| x   | x | х | x | x |     | x   |    | x   |     |

| Z   | x | x | x | x |     | z   |    | x   |     |

Table 4-9 Truth Table for Predefined Primitive Gates

### Gate-level description on Verilog code

#### The wire declaration is for internation of a 2-to-4-line decoder //Figure 4-19

(a) Logic diagram

(b) Truth table

HDL Example 4-1

module decoder\_g1 (A, B, E, D); input A, B, E; output [0:3]D; wire Anot, Bnot, Enot; not nl (Anot, A), n2 (Bnot, B), n3 (Enot, E); nand n4 (D[0], Anot, Bnot, Enot), n5 (D[1], Anot, B, Enot), n6 (D[2], A, Bnot, Enot), n7 (D[3], A, B, Enot);

#### endmodule

# Design methodologies

- There are two basic types of design methodologies: top-down and bottom-up.

- Top-down: the top-level block is defined and then the subblocks necessary to build the top-level block are identified.(Fig.4-9 binary adder)

- Bottom-up: the building blocks are first identified and then combined to build the top-level block.(Example 4-2 4-bit adder)

# A bottom-up hierarchical description

### HDL Example 4-2

```

//Gate-level hierarchical description of 4-bit adder

// Description of half adder (see Fig 4-5b)

module halfadder (S,C,x,y);

input x,y;

output S,C;

//Instantiate primitive gates

xor (S, x, y);

and (C, x, y);

endmodule

```

# Full-adder

```

//Description of full adder (see Fig 4-8)

module fulladder (S,C,x,y,z);

input x,y,z;

output S,C;

wire S1, D1, D2; //Outputs of first XOR and two AND gates

//Instantiate the halfadder

halfadder HA1 (S1, D1, x, y),

HA2 (S, D2, S1, z);

or g1(C, D2, D1);

endmodule

```

# 4-bit adder

```

//Description of 4-bit adder (see Fig 4-9)

module _4bit_adder (S,C4,A,B,C0);

input [3:0] A,B;

input CO;

output [3:0] S;

output C4;

wire C1, C2, C3; //Intermediate carries

//Instantiate the fulladder

fulladder FA0 (S[0],C1,A[0],B[0],C0),

FA1 (S[1],C2,A[1],B[1],C1),

FA2 (S[2],C3,A[2],B[2],C2),

FA3 (S[3],C4,A[3],B[3],C3);

endmodule

```

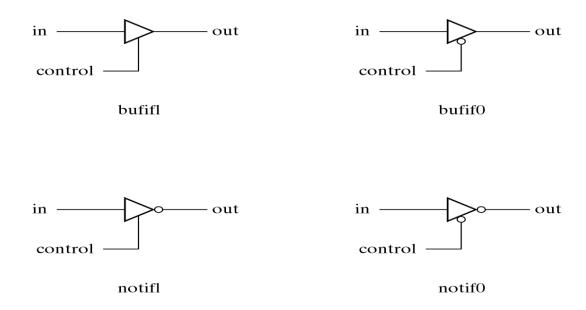

### Three state gates

Gates statement: gate name(output, input, control)

- >> bufif I (OUT, A, control);

- A = OUT when control = I, OUT = z when control = 0; >> notif0(Y, B, enable);

- Y = B' when enable = 0, Y = z when enable = 1;

Fig. 4-31 Three-State Gates

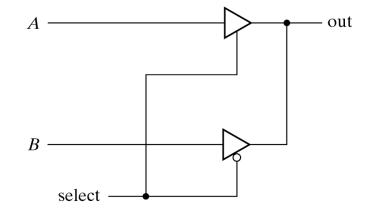

# 2-to-1 multiplexer

HDL uses the keyword tri to indicate that the output has multiple drivers.

```

module muxtri (A, B, select, OUT);

input A,B,select;

output OUT;

tri OUT;

bufif I (OUT,A,select);

bufif0 (OUT,B,select);

endmodule

```

Fig. 4-32 2-to-1-Line Multiplexer with Three-State Buffers

# Dataflow modeling

It uses a number of operators that act on operands to produce desired results. Verilog HDL provides about 30 operator types.

Table 4-10

| Tuble |                    |  |

|-------|--------------------|--|

| Symbo | Operation          |  |

| +     | binary addition    |  |

|       | binary subtraction |  |

| &     | bit-wise AND       |  |

|       | bit-wise OR        |  |

| ^     | bit-wise XOR       |  |

| ~     | bit-wise NOT       |  |

| ==    | equality           |  |

| >     | greater than       |  |

| <     | less than          |  |

| { }   | concatenation      |  |

| ?:    | conditional        |  |

|       |                    |  |

# Dataflow modeling

A continuous assignment is a statement that assigns a value to a net.

- The data type net is used in Verilog HDL to represent a physical connection between circuit elements.

- A net defines a gate output declared by an output or wire.

#### HDL Example 4-3

HDL Example 4

```

//Dataflow description of a 2-to-4-line decoder

//See Fig. 4-19

module decoder_df (A,B,E,D);

input A,B,E;

output [0:3] D;

assign D[0] = ~(~A & ~B & ~E),

D[1] = ~(~A & B & ~E),

D[2] = ~(~A & B & ~E),

D[3] = ~(A & B & ~E);

endmodule

```

### Dataflow description of 4-bit adder

### HDL Example 4-4

```

//Dataflow description of 4-bit adder

module binary_adder (A,B,Cin,SUM,Cout);

input [3:0] A,B;

input Cin;

output [3:0] SUM;

output Cout;

assign {Cout,SUM} = A + B + Cin;

endmodule

```

# Data flow description of a 4-bit comparator

### HDL Example 4-5

```

//Dataflow description of a 4-bit comparator.

module magcomp (A,B,ALSB,AGTB,AEQB);

input [3:0] A,B;

output ALTB,AGTB,AEQB;

assign ALTB=(A < B),

AGTB = (A > B),

AEQB = (A == B);

```

endmodule

### Dataflow description of 2-1 multiplexer

Conditional operator(?:)

Condition? true-expression : false-expression;

### HDL Example 4-6

```

//Dataflow description of 2-to-1-line multiplexer

module mux2x1_df (A,B,select,OUT);

input A,B,select;

output OUT;

assign OUT = select ? A : B;

endmodule

```

# **Behavioral modeling**

- It is used mostly to describe sequential circuits, but can be used also to describe combinational circuits.

- Behavioral descriptions use the keyword always followed by a list of procedural assignment statements.

- The target output of procedural assignment statements must be of the reg data type. Contrary to the wire data type, where the target output of an assignment may be continuously updated, a reg data type retains its value until a new value is assigned.

### Behavioral description of 2-1 multiplexer

### HDL Example 4-7

```

//Behavioral description of 2-to-1-line multiplexer

module mux2x1_bh(A, B, select, OUT);

input A, B, select;

output OUT;

reg OUT;

always @ (select or A or B)

if (select == 1) OUT = A;

else OUT = B;

endmodule

```

# 4-to-I-line Multiplexer

#### HDL Example 4-8

the Leegen

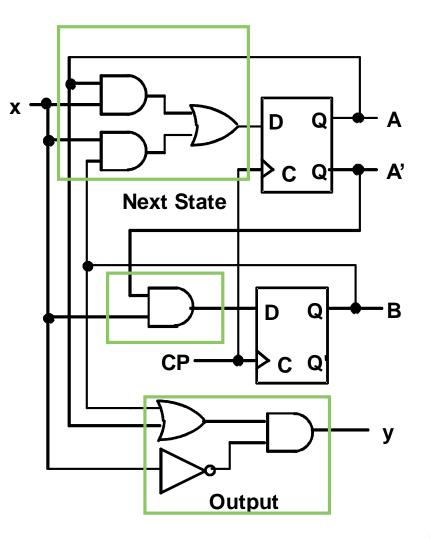

### Unit-III & IV Synchronous and Asynchronous Sequential Circuits

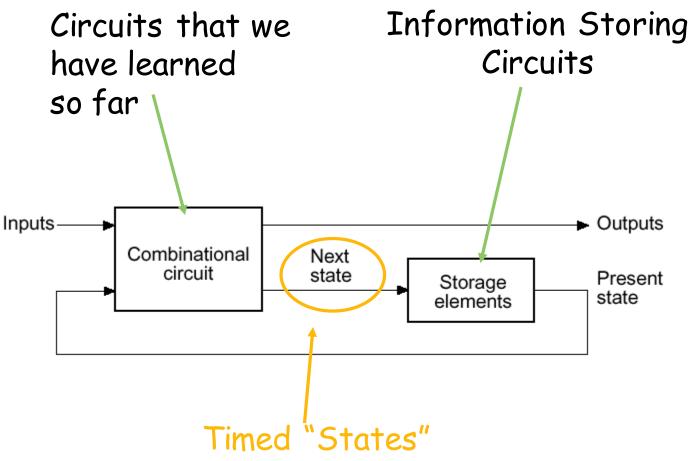

# **Combinational Logic**

- Combinational Logic:

- Output depends only on current input

- Has no memory

# Sequential Logic

- Sequential Logic:

- Output depends not only on current input but also on past input values, e.g., design a counter

- Need some type of memory to remember the past input values

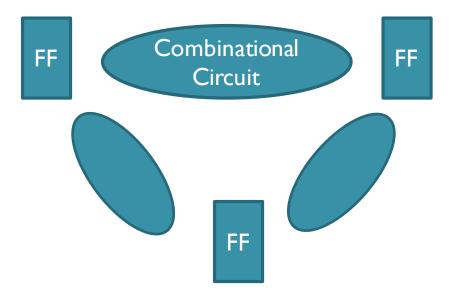

# Sequential Circuits

# Sequential Logic: Concept

- Sequential Logic circuits remember past inputs and past circuit state.

- Outputs from the system are "fed back" as new inputs

- With gate delay and wire delay

- The storage elements are circuits that are capable of storing binary information: memory.

| Combinational Circuits                    | Sequential Circuits                                      |

|-------------------------------------------|----------------------------------------------------------|

| Outputs depend only on present<br>inputs. | Outputs depend on both present inputs and present state. |

| Feedback path is not present.             | Feedback path is present.                                |

| Memory elements are not required.         | Memory elements are required.                            |

| Clock signal is not required.             | Clock signal is required.                                |

| Easy to design.                           | Difficult to design.                                     |

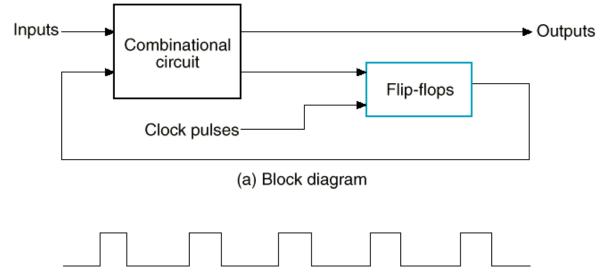

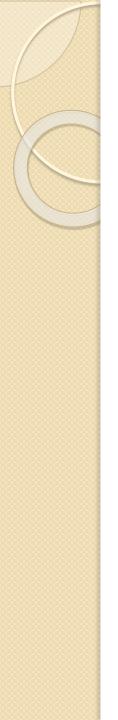

### Synchronous vs. Asynchronous

There are two types of sequential circuits:

- **Synchronous** sequential circuit: circuit output changes only at some discrete instants of time. This type of circuits achieves synchronization by using a timing signal called the *clock*.

- **Asynchronous** sequential circuit: circuit output can change at **any** time (clockless).

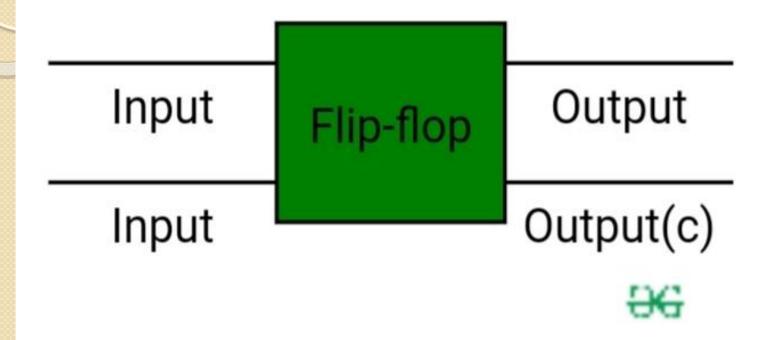

### Synchronous Sequential Circuits: Flip flops as state memory

(b) Timing diagram of clock pulses

The flip-flops receive their inputs from the combinational circuit and also from a clock signal with pulses that occur at fixed intervals of time, as shown in the timing diagram.

# **Clock Period**

Smallest clock period = largest combinational circuit delay between any two directly connected FF, subjected to impact of FF setup time.

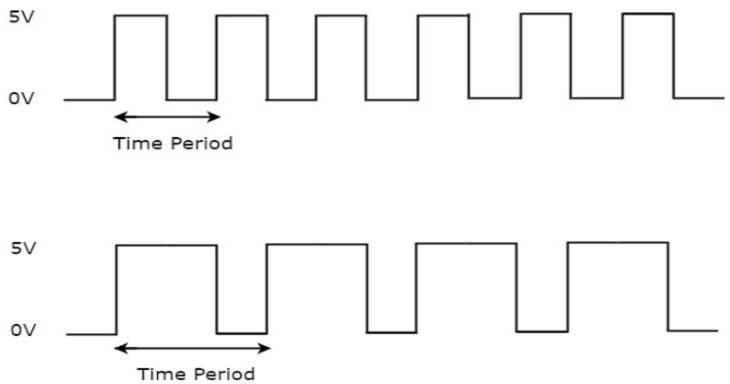

# **CLOCK SIGNAL**

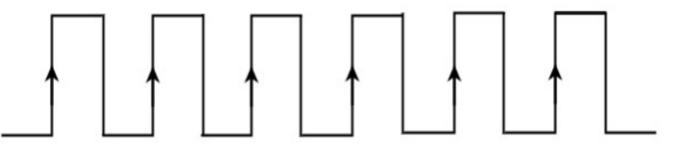

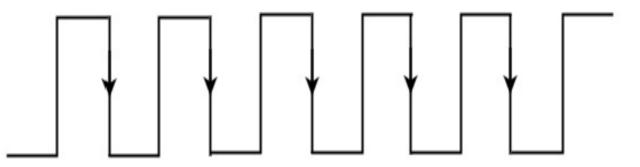

## TYPES OF TRIGGERING

There are two levels, namely logic High and logic Low in clock signal. Following are the two types of level triggering.

- Positive level triggering

- Negative level triggering

If the sequential circuit is operated with the clock signal when it is in **Logic High**, then that type of triggering is known as **Positive level triggering**. It is highlighted in below figure.

If the sequential circuit is operated with the clock signal when it is in **Logic Low**, then that type of triggering is known as **Negative level triggering**. It is highlighted in the following figure.

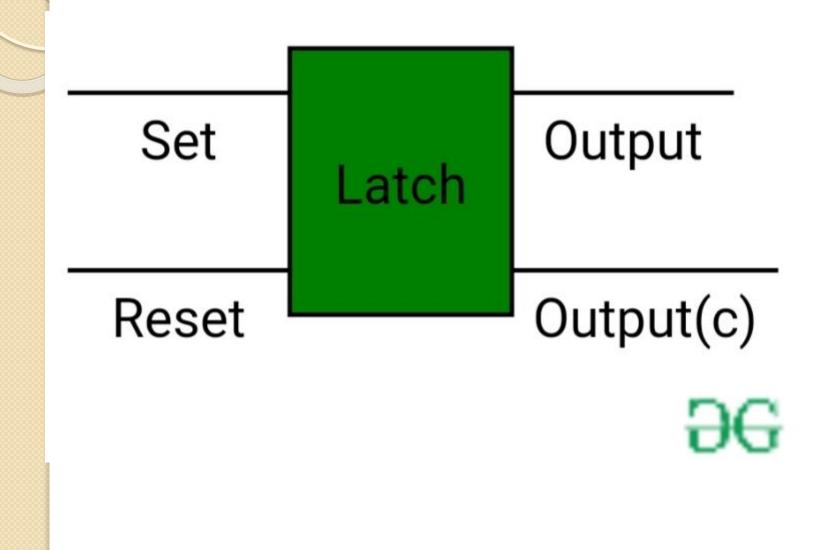

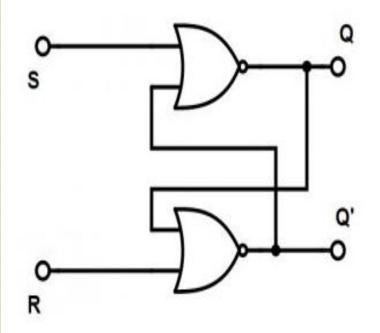

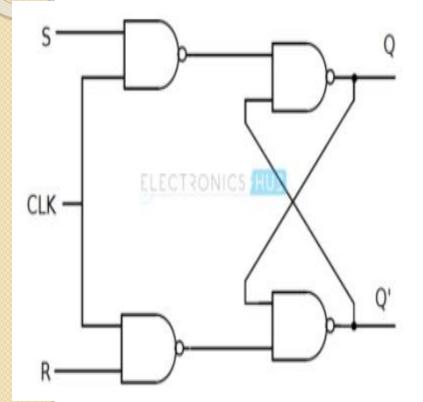

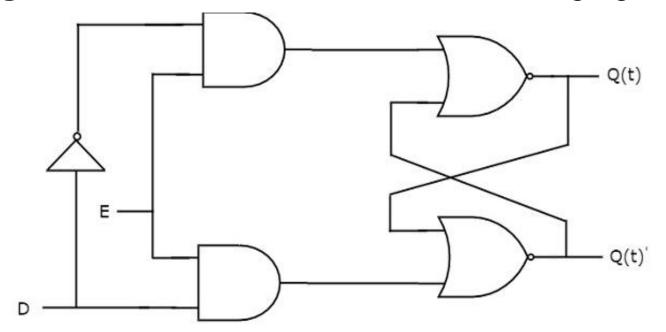

# EDGETRIGERRING