(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408,Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

# ECE

II/IV

Course Name with Code: 19ECC07/MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: I – 8051MICROCONTROLLER

Date of Lecture:

#### Topic of Lecture: Architecture of 8051

#### Introduction :

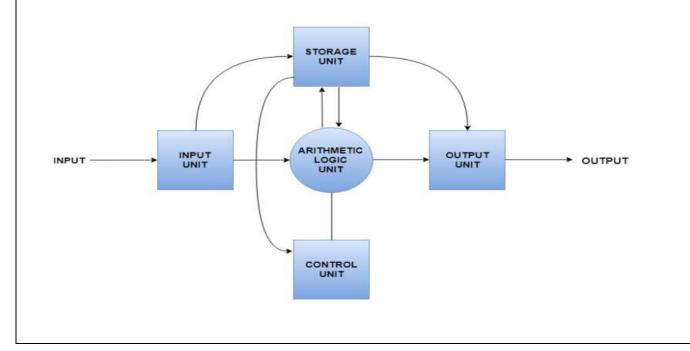

A microcontroller is essentially a small computer on a chip. Like any computer, it has memory, and can be programmed to do calculations, receive input, and generate output. Unlike a PC, it incorporates memory, a CPU, peripherals and I/O interfaces into a single chip.

#### Prerequisite knowledge for Complete understanding and learning of Topic:

Basics of Digital circuits

#### Detailed content of the Lecture:

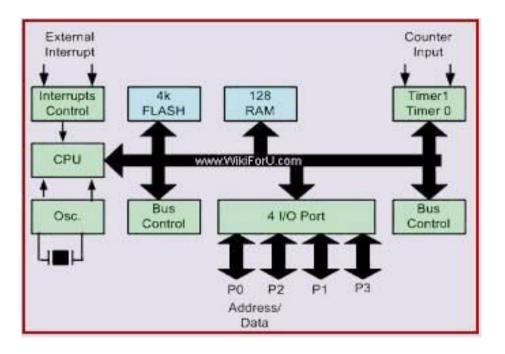

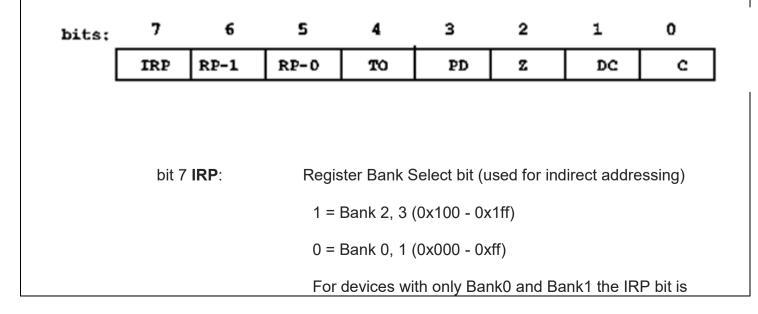

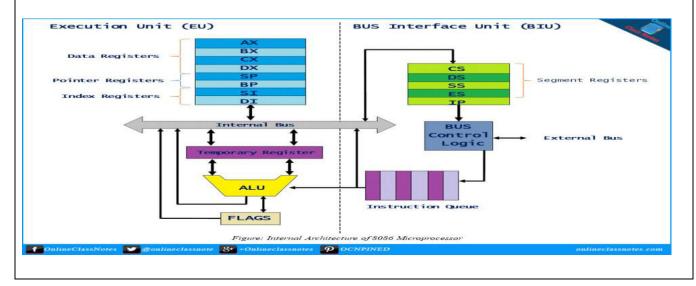

The 8051 Microcontroller is one of the basic type of microcontroller, designed by Intel in 1980's. This microcontroller was based on Harvard Architecture and developed primarily for use in <u>embedded systems</u> technology. Normally, this microcontroller was developed using NMOS technology, which requires more power to operate. Therefore, Intel redesigned Microcontroller 8051 using CMOS technology and their updated versions came with a letter C in their name, for instance an 80C51 it is an 8 bit microcontroller. These latest Microcontrollers requires less power to operate as compared to their previous versions. The 8051 Microcontroller has two buses and two memory spaces of 64K X 8 size for program and data units. It has an 8 bit processing unit and 8 bit accumulator units.

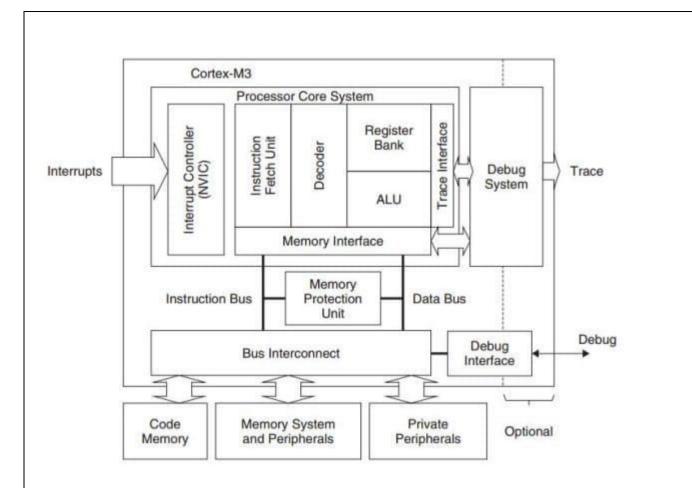

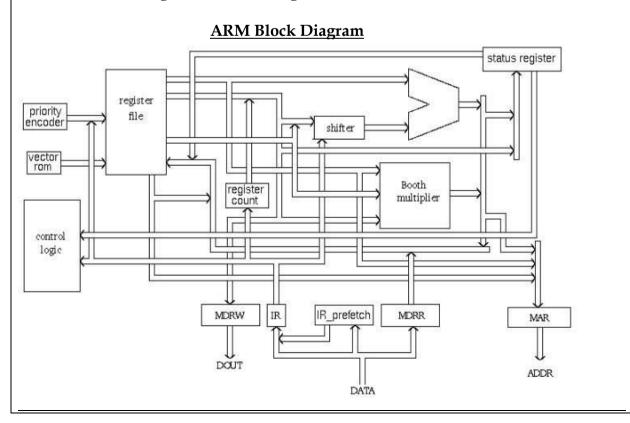

#### Central Processor Unit (CPU)

As we know that the CPU is the brain of any processing device of the microcontroller. It monitors and controls all operations that are performed on the Microcontroller units. The User has no control over the work of the CPU directly. It reads program written in ROM memory and executes them and do the expected task of that application.

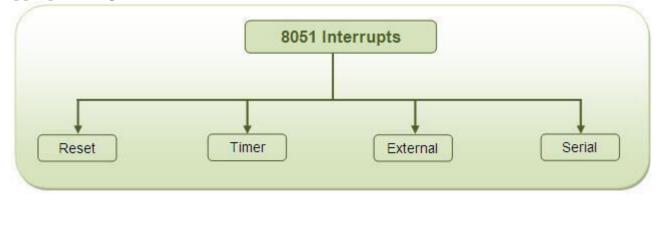

#### Interrupts

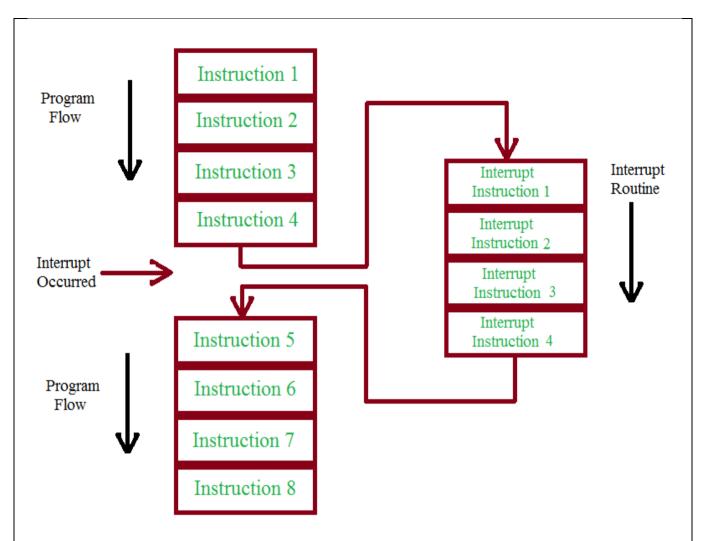

As its name suggests, Interrupt is a subroutine call that interrupts of the microcontrollers main operations or work and causes it to execute any other program, which is more important at the time of operation. The feature of Interrupt is very useful as it helps in case of emergency operations. An Interrupts gives us a mechanism to put on hold the

ongoing operations, execute a subroutine and then again resumes to another type of operations. The Microcontroller 8051 can be configured in such a way that it temporarily terminates or pause the main program at the occurrence of interrupts. When a subroutine is completed, Then the execution of main program starts. Generally five interrupt sources are there in 8051 Microcontroller.

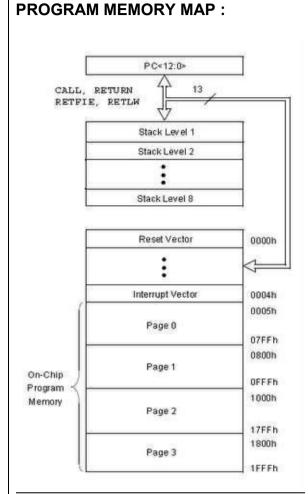

#### Memory

Microcontroller requires a program which is a collection of instructions. This program tells microcontroller to do specific tasks. These programs require a memory on which these can be saved and read by Microcontroller to perform specific operations of a particular task. The memory which is used to store the program\_of\_the microcontroller is known as code memory or Program memory of applications. It is known as ROM memory of microcontroller also requires a memory to store data or operands temporarily of the micro controller. The data memory of the 8051 is used to store data temporarily for operation is known RAM memory. 8051 microcontroller has 4K of code memory or program memory,That has 4KB ROM and also 128 bytes of data memory of RAM.

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=O-UALuVyyLY

#### Important Books/Journals for further learning including the page nos.:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (4-10)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

II/IV

ECE

#### Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: I - 8051 MICROCONTROLLER

Date of Lecture:

Topic of Lecture: Architecture of 8051 Microprocessor

#### Introduction :

A microcontroller is essentially a small computer on a chip. Like any computer, it has memory, and can be programmed to do calculations, receive input, and generate output. Unlike a PC, it incorporates memory, a CPU, peripherals and I/O interfaces into a single chip.

#### Prerequisite knowledge for Complete understanding and learning of Topic:

- Processors and controllers

- Central processing unit

- > BUS

#### **Detailed content of the Lecture:**

Basically Bus is a collection of wires which work as a communication channel or medium for transfer of Data. These buses consists of 8, 16 or more wires of the microcontroller. Thus, these can carry 8 bits,16 bits simultaneously. Hire two types of buses that are shown in below

- Address Bus

- Data Bus

#### Address Bus

Microcontroller 8051 has a 16 bit address bus for transferring the data. It is used to address memory locations and to transfer the address from CPU to Memory of the microcontroller.

#### Data Bus

Microcontroller 8051 has 8 bits of the data bus, which is used to carry data of particular applications.

#### Oscillator

Generally, we know that the microcontroller is a device, therefore it requires clock pulses for its operation of microcontroller applications. For this purpose, microcontroller 8051 has an on-chip oscillator which works as a clock source for Central Processing Unit of the microcontroller. The output pulses of oscillator are stable. Therefore, it enables synchronized work of all parts of the 8051 Microcontroller.

# Input/Output Port

Normally microcontroller is used in embedded systems to control the operation of machines in the microcontroller. Therefore, to connect it to other machines, devices or peripherals we require I/O interfacing ports in the microcontroller interface. For this purpose microcontroller 8051 has 4 input, output ports to connect it to the other peripherals.

## Timers/Counters

8051 microcontroller has two 16 bit timers and counters. These counters are again divided into a 8 bit register. The timers are used for measurement of intervals to determine the pulse width of pulses.

# Applications of 8051 Microcontroller

Some of the applications of 8051 is mainly used in daily life & industrial applications also some of that applications are shown below

- Light sensing and controlling devices

- Temperature sensing and controlling devices

- Fire detections and safety devices

- Automobile applications

- Defense applications

Some industrial applications of micro controller and its applications

- Industrial instrumentation devices

- Process control devices

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=O-UALuVyyLY

# Important Books/Journals for further learning including the page nos.:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085,wiley eastern ltd, New Delhi 2013-Page no (24-30)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

ECE

II/IV

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: I - 8051MICROCONTROLLER

Date of Lecture:

Topic of Lecture: Special Function Registers(SFRs)

#### Introduction :

Each bit is wired across to one or other of the microcontroller peripherals. Each is then used either to set up the operating mode of the peripheral or to transfer data between the peripheral and the microcontroller core.

Prerequisite knowledge for Complete understanding and learning of Topic:

➢ Basics of digital electronics

**Detailed content of the Lecture:**

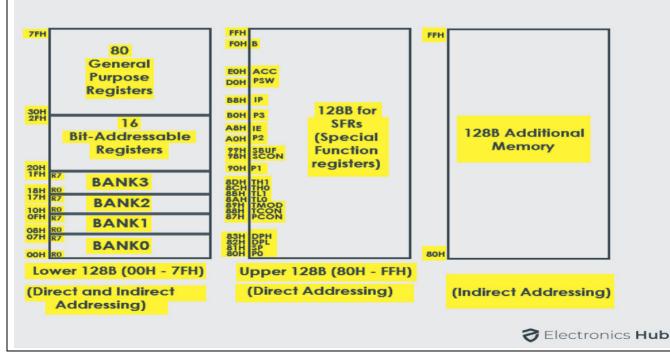

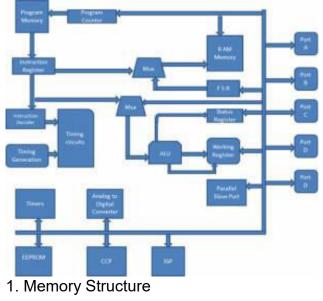

The 8051 Microcontroller Special Function Registers are used to program and control different hardware peripherals like Timers, Serial Port, I/O Ports etc. In fact, by manipulating the 8051 Microcontroller Special Function Registers (SFRs), you can assess or change the operating mode of the 8051 Microcontroller.

The following image shows you the basic structure of 8051 Microcontroller's Internal RAM.

## Data Memory (RAM) Of 8051 Microcontroller

#### 8051 Microcontroller Special Function Registers (SFRs):

The 8051 Microcontroller Special Function Registers act as a control table that monitor and control the operation of the 8051 Microcontroller. If you observe in Internal RAM Structure, the Address Space from 80H to FFH is allocated to SFRs. Out of these 128 Memory Locations (80H to FFH), there are only 21 locations that are actually assigned to SFRs. Each SFR has one Byte Address and also a unique name which specifies its purpose. Since the SFRs are a part of the Internal RAM Structure, you can access SFRs as if you access the Internal RAM. The main difference is the address space: first 128 Bytes (00H to 7FH) is for regular Internal RAM and next 128 Bytes (80H to FFH) is for SFRS.

List of 8051 Microcontroller Special Function Registers

- A or ACC

- B

- DPL

- DPH

- IE

- IP

- P0

- P1

- P2

- P3

- PCON

- PSW

- SCON

- SBUF

- SP

- TMOD

- TCON

- TL0

- TH0

- TL1

- TH1

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=i8IT4Mu8afI

Important Books/Journals for further learning including the page nos.:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (24-30)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

## Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

#### : I - 8015 MICROCONTROLLER

Date of Lecture:

Topic of Lecture: Special Function Registers(SFRs)

#### Introduction :

Each bit is wired across to one or other of the microcontroller peripherals. Each is then used either to set up the operating mode of the peripheral or to transfer data between the peripheral and the microcontroller core

Prerequisite knowledge for Complete understanding and learning of Topic:➢ Basics of digital electronics

**Detailed content of the Lecture:**

#### **Categories of 8051 Microcontroller Special Function Registers:**

All the 21 8051 Microcontroller Special Function Registers (SFRs) along with their functions and

Internal RAM Address is given in the following table.

| Name of the Register Function     |                             | Internal RAM Address (HEX) |  |

|-----------------------------------|-----------------------------|----------------------------|--|

| ACC                               | Accumulator                 | E0H                        |  |

| В                                 | B Register (for Arithmetic) | F0H                        |  |

| DPH                               | Addressing External Memory  | 83H                        |  |

| DPL                               | Addressing External Memory  | 82H                        |  |

| IE                                | Interrupt Enable Control    | A8H                        |  |

| IP                                | Interrupt Priority          | B8H                        |  |

| PO                                | PORT 0 Latch                | 80H                        |  |

| P1                                | PORT 1 Latch                | 90H                        |  |

| P2                                | PORT 2 Latch                | A0H                        |  |

| P3                                | PORT 3 Latch                | B0H                        |  |

| PCON                              | Power Control               | 87H                        |  |

| PSW                               | Program Status Word         | D0H                        |  |

| SCON                              | Serial Port Control         | 98H                        |  |

| SBUF Serial Port Data Buffer      |                             | 99H                        |  |

|                                   |                             | ONICS HUB 81H              |  |

| TMOD Timer / Counter Mode Control |                             | 89H                        |  |

| TCON                              |                             |                            |  |

| TL0                               | Timer 0 LOW Byte 8AH        |                            |  |

| TH0                               | Timer 0 HIGH Byte 8CH       |                            |  |

| TL1                               | Timer 1 LOW Byte 8BH        |                            |  |

| TH1 Timer 1 HIGH Byte             |                             | 8DH                        |  |

There are many ways to categorize these 21 Special Function Registers but I find the following way as an appropriate one. The 21 Special Function Registers of 8051 Microcontroller are categorized in to seven groups. They are:

Math or CPU Registers: A and B

Status Register: PSW (Program Status Word)

**Pointer Registers:** DPTR (Data Pointer – DPL, DPH) and SP (Stack Pointer)

I/O Port Latches: P0 (Port 0), P1 (Port 1), P2 (Port 2) and P3 (Port 3)

Peripheral Control Registers: PCON, SCON, TCON, TMOD, IE and IP

Peripheral Data Registers: TL0, TH0, TL1, TH1 and SBUF

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=i8IT4Mu8afI

Important Books/Journals For Further Learning Including The Page Nos.:

Gaonkar.R.S, Microprocessor Architecture Programming And Applications With 8085, Wiley Eastern Ltd, New Delhi 2013-Page No(12-16)

**Course Faculty**

**ECE**

# MUTHAYAMMAL ENGINEERING COLLEGE

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408,Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

II/IV

L5

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

#### : I - 8051 MICROCONTROLLER

Date of Lecture:

**Topic of Lecture:** I/O Pins Ports and Circuits

Introduction :

8051 microcontrollers have **4 I/O ports each of 8-bit**, which can be configured as input or output. Hence, total 32 input/output pins allow the microcontroller to be connected with the peripheral devices.

Prerequisite knowledge for Complete understanding and learning of Topic:

Instruction Sets

#### **Detailed content of the Lecture:**

8051 microcontrollers have 4 I/O ports each of 8-bit, which can be configured as input or output. Hence, total 32 input/output pins allow the microcontroller to be connected with the peripheral devices.

- Pin configuration, i.e. the pin can be configured as 1 for input and 0 for output as per the logic state.

- **Input/Output (I/O) pin** All the circuits within the microcontroller must be connected to one of its pins except P0 port because it does not have pull-up resistors built-in.

- **Input pin** Logic 1 is applied to a bit of the P register. The output FE transistor is turned off and the other pin remains connected to the power supply voltage over a pull-up resistor of high resistance.

Port 0 - The P0 (zero) port is characterized by two functions -

- When the external memory is used then the lower address byte (addresses A0A7) is applied on it, else all bits of this port are configured as input/output.

- When P0 port is configured as an output then other ports consisting of pins with builtin pull-up resistor connected by its end to 5V power supply, the pins of this port have this resistor left out.

#### **Input Configuration**

If any pin of this port is configured as an input, then it acts as if it "floats", i.e. the input has unlimited input resistance and in-determined potential.

#### **Output Configuration**

When the pin is configured as an output, then it acts as an "open drain". By applying logic 0 to a port bit, the appropriate pin will be connected to ground (0V), and applying logic 1, the external output will keep on "floating".

In order to apply logic 1 (5V) on this output pin, it is necessary to build an external pullup resistor.

#### Port 1

P1 is a true I/O port as it doesn't have any alternative functions as in P0, but this port can be configured as general I/O only. It has a built-in pull-up resistor and is completely compatible with TTL circuits.

#### Port 2

P2 is similar to P0 when the external memory is used. Pins of this port occupy addresses intended for the external memory chip. This port can be used for higher address byte with addresses A8-A15. When no memory is added then this port can be used as a general input/output port similar to Port 1.

#### Port 3

In this port, functions are similar to other ports except that the logic 1 must be applied to appropriate bit of the P3 register.

Pins Current Limitations

- When pins are configured as an output (i.e. logic 0), then the single port pins can receive a current of 10mA.

- When these pins are configured as inputs (i.e. logic 1), then built-in pull-up resistors provide very weak current, but can activate up to 4 TTL inputs of LS series.

- If all 8 bits of a port are active, then the total current must be limited to 15mA (port P0: 26mA).

- If all ports (32 bits) are active, then the total maximum current must be limited to 71mA.

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=WU8uvapSIic

**Important Books/Journals for further learning including the page nos.**:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (156-188)

**Course Faculty**

ECE

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

LECTURE HANDOUTS

Π/Ιν

L6

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: I - 8051 MICROCONTROLLER

Date of Lecture:

**Topic of Lecture**: Instruction set

#### Introduction :

An instruction set is **a group of commands for a CPU in machine language**. The term can refer to all possible instructions for a CPU or a subset of instructions to enhance its performance in certain situations. ... Some instructions are simple read, write and move commands that direct data to different hardware.

Prerequisite knowledge for Complete understanding and learning of Topic: ➤ Instruction set

#### Detailed content of the Lecture:

An Instruction Set is unique to a family of computers. This tutorial introduces the 8051 Microcontroller Instruction Set also called as the MCS-51 Instruction Set. As the 8051 family of Microcontrollers are 8-bit processors, the 8051 Microcontroller Instruction Set is optimized for 8-bit control applications. As a typical 8-bit processor, the 8051 Microcontroller instructions have 8-bit Opcodes. As a result, the 8051 Microcontroller instruction set can have up to  $2^8 = 256$  Instructions.

A Brief Look at 8051 Microcontroller Instructions and Groups:

Before going into the details of the 8051 Microcontroller Instruction Set, Types of Instructions and the Addressing Mode, let us take a brief look at the instructions and the instruction groups of the 8051 Microcontroller Instruction Set (the MCS-51 Instruction Set).

The following table shows the 8051 Instruction Groups and Instructions in each group. There are 49 Instruction Mnemonics in the 8051 Microcontroller Instruction Set and these 49 Mnemonics are divided into five groups.

| DATA TRANSFER | ARITHMETIC | LOGICAL | BOOLEAN | PROGRAM BRANCHING |

|---------------|------------|---------|---------|-------------------|

| MOV           | ADD        | ANL     | CLR     | LJMP              |

| MOVC          | ADDC       | ORL     | SETB    | AJMP              |

| MOVX          | SUBB       | XRL     | MOV     | SJMP              |

| PUSH          | INC        | CLR     | JC      | JZ                |

| POP           | DEC        | CPL     | JNC     | JNZ               |

| ХСН           | MUL        | RL      | JB      | CJNE              |

| XCHD          | DIV        | RLC     | JNB     | DJNZ              |

|               | DA A       | RR      | JBC     | NOP               |

|               |            | RRC     | ANL     | LCALL             |

|               |            | SWAP    | ORL     | ACALL             |

|               |            |         | CPL     | RET               |

|               |            |         |         | RETI              |

|               |            |         |         | JMP               |

## Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=9VY6d6oJr7s

#### Important Books/Journals for further learning including the page nos.:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (352-370)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408,Namakkal Dist., Tamil Nadu

LECTURE HANDOUTS

# ECE

II/IV

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

#### : I – 8051 MICROCONTROLLER

Date of Lecture:

Topic of Lecture: : Instruction set

#### Introduction :

An instruction set is **a group of commands for a CPU in machine language**. The term can refer to all possible instructions for a CPU or a subset of instructions to enhance its performance in certain situations. ... Some instructions are simple read, write and move commands that direct data to different hardware

## Prerequisite knowledge for Complete understanding and learning of Topic:

Instruction set

## Detailed content of the Lecture:

#### What is an Addressing Mode?

An Addressing Mode is a way to locate a target Data, which is also called as Operand. The 8051 Family of Microcontrollers allows five types of Addressing Modes for addressing the Operands. They are:

- Immediate Addressing

- Register Addressing

- Direct Addressing

- Register Indirect Addressing

- Indexed Addressing

## Immediate Addressing

In Immediate Addressing mode, the operand, which follows the Opcode, is a constant data of either 8 or 16 bits. The name Immediate Addressing came from the fact that the constant data to be stored in the memory immediately follows the Opcode. The constant value to be stored is specified in the instruction itself rather than taking from a register. The destination register to which the constant data must be copied should be the same size as the operand mentioned in the instruction.

# Example: MOV A, #030H

Here, the Accumulator is loaded with 30 (hexadecimal). The # in the operand indicates that it is a data and not the address of a Register. Immediate Addressing is very fast as the data to be loaded is given in the instruction itself.

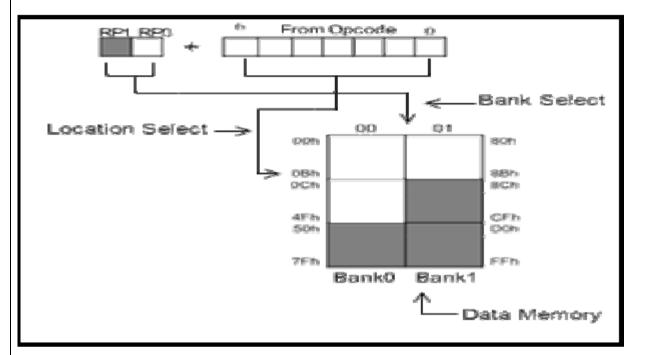

#### **Register Addressing**

In the 8051 Microcontroller Memory Organization Tutorial, we have seen the organization of RAM and four banks of Working Registers with eight Registers in each bank. In Register Addressing mode, one of the eight registers (R0 – R7) is specified as Operand in the Instruction. It is important to select the appropriate Bank with the help of PSW Register. Let us see a example of Register Addressing assuming that Bank0 is selected.

#### Example: MOV A, R5

Here, the 8-bit content of the Register R5 of Bank0 is moved to the Accumulator.

#### **Direct Addressing**

In Direct Addressing Mode, the address of the data is specified as the Operand in the instruction. Using Direct Addressing Mode, we can access any register or onchip variable. This includes general purpose RAM, SFRs, I/O Ports, Control registers.

#### Example: MOV A, 47H

Here, the data in the RAM location 47H is moved to the Accumulator.

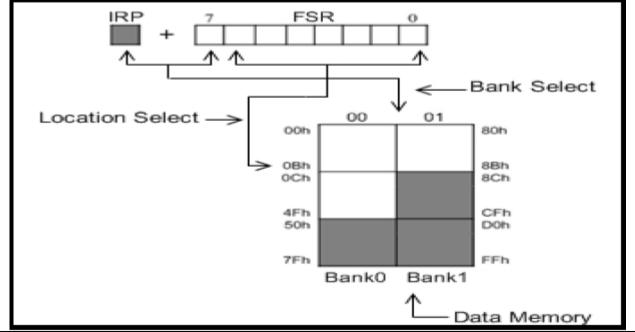

#### **Register Indirect Addressing**

In the Indirect Addressing Mode or Register Indirect Addressing Mode, the address of the Operand is specified as the content of a Register. This will be clearer with an example.

#### Example: MOV A, @R1

The @ symbol indicates that the addressing mode is indirect. If the contents of R1 is 56H, for example, then the operand is in the internal RAM location 56H. If the contents of the RAM location 56H is 24H, then 24H is moved into accumulator. Only R0 and R1 are allowed in Indirect Addressing Mode. These register in the indirect addressing mode are called as Pointer registers.

#### Indexed Addressing Mode

With Indexed Addressing Mode, the effective address of the Operand is the sum of a base register and an offset register. The Base Register can be either Data Pointer (DPTR) or Program Counter (PC) while the Offset register is the Accumulator (A). In Indexed Addressing Mode, only MOVC and JMP instructions can be used. Indexed Addressing Mode is useful when retrieving data from look-up tables.

#### Example: MOVC A, @A+DPTR

Here, the address for the operand is the sum of contents of DPTR and Accumulator

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=9VY6d6oJr7s

#### Important Books/Journals for further learning including the page nos.:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (78-83)

**Course Faculty**

(An Autonomous Institution)

**LECTURE HANDOUTS**

II/IV

IQAO

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: I -8051 MICROCONTROLLER

Date of Lecture:

Topic of Lecture: Addressing modes

#### Introduction :

An Addressing Mode is a way to locate a target Data, which is also called as Operand. The 8051 Family of Microcontrollers allows five types of Addressing Modes for addressing the Operands. They are: Immediate Addressing. Register Addressing.

Prerequisite knowledge for Complete understanding and learning of Topic:

Addressing modes

**Detailed content of the Lecture:**

In 8051 there are 1-byte, 2-byte instructions and very few 3-byte instructions are present. The opcodes are 8-bit long. As the opcodes are 8-bit data, there are 256 possibilities. Among 256, 255 opcodes are implemented.

The clock frequency is12MHz, so 64 instruction types are executed in just 1  $\mu$ s, and rest are just 2  $\mu$ s. The Multiplication and Division operations take 4  $\mu$ sto to execute.

In 8051 There are six types of addressing modes.

- Immediate Addressing Mode

- Register Addressing Mode

- Direct Addressing Mode

- Register Indirect Addressing Mode

- Indexed Addressing Mode

- Implied Addressing Mode

## Immediate addressing mode

In this Immediate Addressing Mode, the data is provided in the instruction itself. The data is provided immediately after the opcode. These are some

examples of Immediate Addressing Mode.

MOVA, #0AFH; MOVR3, #45H;

MOVDPTR, **#FE00H;**

In these instructions, the # symbol is used for immediate data. In the last instruction, there is DPTR. The DPTR stands for Data Pointer. Using this, it points the external data memory location. In the first instruction, the immediate data is AFH, but one 0 is added at the beginning. So when the data is starting with A to F, the data should be preceded by 0.

#### **Register addressing mode**

In the register addressing mode the source or destination data should be present in a register (R0 to R7). These are some examples of Register Addressing Mode.

MOVA, R5;

MOVR2, **#45H**;

MOVR0, A;

In 8051, there is no instruction like **MOVR5**, **R7**. But we can get the same result by using this instruction **MOV R5**, **07H**, or by using **MOV 05H**, **R7**. But this two instruction will work when the selected register bank is **RB0**. To use another register bank and to get the same effect, we have to add the starting address of that register bank with the register number. For an example, if the RB2 is selected, and we want to access R5, then the address will be (10H + 05H = 15H), so the instruction will look like this **MOV 15H**, **R7**. Here 10H is the starting address of Register Bank 2.

#### **Direct Addressing Mode**

In the Direct Addressing Mode, the source or destination address is specified by using 8-bit data in the instruction. Only the internal data memory can be used in this mode. Here some of the examples of direct Addressing Mode.

MOV80H, R6;

MOVR2, 45H;

MOVR0, 05H;

The first instruction will send the content of registerR6 to port P0 (Address of Port 0 is 80H). The second one is forgetting content from 45H to R2. The third one is used to get data from Register R5 (When register bank RB0 is selected) to register R5.

#### **Register indirect addressing Mode**

In this mode, the source or destination address is given in the register. By using register indirect addressing mode, the internal or external addresses can be accessed. The R0 and R1 are used for 8-bit addresses, and DPTR is used for 16-bit addresses, no other registers can be used for addressing purposes. Let us see some examples of this mode.

```

MOV0E5H, @R0;

```

MOV@R1, 80H

In the instructions, the @ symbol is used for register indirect addressing. In the first instruction, it is showing that theR0 register is used. If the content of R0 is 40H, then that

instruction will take the data which is located at location 40H of the internal RAM. In the second one, if the content of R1 is 30H, then it indicates that the content of port P0 will be stored at location 30H in the internal RAM.

MOVXA, @R1;

MOV@DPTR, A;

In these two instructions, the X in MOVX indicates the external data memory. The external data memory can only be accessed in register indirect mode. In the first instruction if the R0 is holding 40H, then A will get the content of external RAM location40H. And in the second one, the content of A is overwritten in the location pointed by DPTR.

#### Indexed addressing mode

In the indexed addressing mode, the source memory can only be accessed from program memory only. The destination operand is always the register A. These are some examples of Indexed addressing mode.

MOVCA, @A+PC;

MOVCA, @A+DPTR;

The C in MOVC instruction refers to code byte. For the first instruction, let us consider A holds 30H. And the PC value is1125H. The contents of program memory location 1155H (30H + 1125H) are moved to register A.

#### Implied Addressing Mode

In the implied addressing mode, there will be a single operand. These types of instruction can work on specific registers only. These types of instructions are also known as register specific instruction. Here are some examples of Implied Addressing Mode.

RLA;

SWAPA;

These are 1- byte instruction. The first one is used to rotate the A register content to the Left. The second one is used to swap the nibbles in A.

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=LUlq\_KBhhXE

#### Important Books/Journals for further learning including the page nos.:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (41-45)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408,Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

# ECE

# Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

# : I - 8051 MICROCONTROLLER

Date of Lecture:

II/IV

Topic of Lecture- Assembly language programming

#### Introduction :

An assembly language is a low-level programming language for microprocessors and other programmable devices. It is not just a single language, but rather a group of languages. An assembly language implements a symbolic representation of the machine code needed to program a given CPU architecture

## Prerequisite knowledge for Complete understanding and learning of Topic:

Assembly language programming

#### Detailed content of the Lecture:

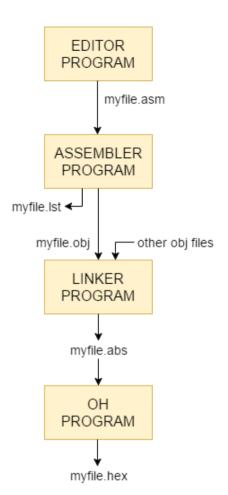

Programming in the sense of Microcontrollers (or any computer) means writing a sequence of instructions that are executed by the processor in a particular order to perform a predefined task. Programming also involves debugging and troubleshooting of instructions and instruction sequence to make sure that the desired task is performed.

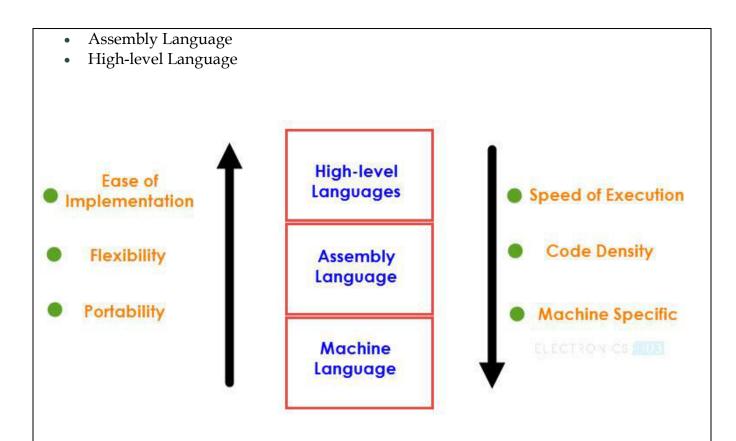

Like any language, Programming Languages have certain words, grammar and rules. There are three types or levels of Programming Languages for 8051 Microcontroller. These levels are based on how closely the statements in the language resemble the operations or tasks performed by the Microcontroller.

The three levels of Programming Languages are:

Machine Language

#### Machine language

In Machine language or Machine Code, the instructions are written in binary bit patterns i.e. combination of binary digits 1 and 0, which are stored as HIGH and LOW Voltage Levels. This is the lowest level of programming languages and is the language that a Microcontroller or Microprocessor actually understands.

#### Assembly Language

The next level of Programming Language is the Assembly Language. Since Machine Language or Code involves all the instructions in 1's and 0's, it is very difficult for humans to program using it. Assembly Language is a pseudo-English representation of the Machine Language. The 8051 Microcontroller Assembly Language is a combination of English like words called Mnemonics and Hexadecimal codes.

It is also a low level language and requires extensive understanding of the architecture of the Microcontroller.

#### High-level Language

The name High-level language means that you need not worry about the architecture or other internal details of a microcontroller and they use words and statements that are easily understood by humans.

Few examples of High-level Languages are BASIC, C Pascal, C++ and Java. A program called Compiler will convert the Programs written in High-level languages to Machine Code.

## Why Assembly Language?

Although High-level languages are easy to work with, the following reasons point out the advantage of Assembly Language

- The Programs written in Assembly gets executed faster and they occupy less memory.

- With the help of Assembly Language, you can directly exploit all the features of a Microcontroller.

- Using Assembly Language, you can have direct and accurate control of all the Microcontroller's resources like I/O Ports, RAM, SFRs, etc.

- Compared to High-level Languages, Assembly Language has less rules and restrictions.

#### Structure of the 8051 Microcontroller Assembly Language:

The Structure or Syntax of the 8051 Microcontroller Assembly Language is discussed here. Each line or statement of the assembly language program of 8051 Microcontroller consists of three fields: Label, Instruction and Comments.

The arrangement of these fields or the order in which they appear is shown below.

[Label:] Instructions [//Comments]

**NOTE:** The brackets for Label and Comments mean that these fields are optional and may not be used in all statements in a program.

Before seeing about these three fields, let us first see an example of how a typical statement or line in an 8051 Microcontroller Assembly Language looks like.

## TESTLABEL: MOV A, 24H ; THIS IS A SAMPLE COMMENT

In the above statement, the "TESTLABEL" is the name of the Label, "MOV A, 24H" is the Instruction and the "THIS IS A SAMPLE COMMENT" is a Comment.

# ; THIS IS A SAMPLE COMMENT

Instruction

#### Label

The Label is programmer chosen name for a Memory Location or a statement in a program. The Label part of the statement is optional and if present, the Label must be terminated with a Colon (:).An important point to remember while selecting a name for the Label is that they should reduce the need for documentation.

#### Instruction

The Instruction is the main part of the 8051 Microcontroller Assembly Language Programming as it is responsible for the task performed by the Microcontroller. Any Instruction in the Assembly Language consists of two parts: Op-code and Operand(s).

The first part of the Instruction is the Op-code, which is short for Operation Code, specifies the operation to be performed by the Microcontroller. Op-codes in Assembly Language are called as Mnemonics. Op-codes are in binary format (used in Machine Language) while the Mnemonic (which are equivalent to Op-codes) are English like statements.

The second part of the instruction is called the Operand(s) and it represents the Data on which the operation is performed. There are two types of Operands: the Source Operand and the Destination Operand. The Source Operand is the Input of the operation and the Destination Operand is where the result is stored.

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=g7Gypl9zNz8

**Important Books/Journals for further learning including the page nos.:**

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (30-41)

**Course Faculty**

# MUTHAYAMMAL ENGINEERING

# COLLEGE

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

L10

ECE

II/IV

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: II – 8051 MICROCONTROLLER INTERFACING

Date of Lecture:

Topic of Lecture: Programming 8051 Timers

#### Introduction :

➢ 8051 Microcontrollers have two timers/counters which work on the clock frequency. Timer/counter can be used for time delay generation, counting external events, etc..

#### Detailed content of the Lecture:

The programming of 8051 Timers can be done by using either polling method or by using interrupt. In polling, the microcontroller keeps monitoring the status of Timer flag. While doing so, it does no other operation and consumes all its processing time in checking the Timer flag until it is **raised on a rollover**. In interrupt method controller responds to only when the Timer flag is raised. The interrupt method prevents the wastage of controller's processing time unlike polling method.

Polling is mostly used for time delay generation and interrupt method is more useful when waveforms are to be generated or some action has to be repeated in fixed delays.

## (i) Polling Method

The polling method involves the following algorithm:

1. Configure the Timer mode by passing a hex value into the TMOD register. This will tell the controller about which Timer is be used; the mode of Timer; operation (to be used as timer or counter); and whether external interrupt is required to start Timer.

2. Load the initial values in the Timer low TLx and high THx byte. (x = 0/1)

- 3. Start the Timer by setting TRx bit.

- 4. Wait while the Timer flag TFx is raised.

- 5. Clear the Timer flag. The Timer flag is raised when Timer **rolls over** from FFFFH to 0000H. If

the Timer is not stopped, it will start updating from 0000H in case of modes 0 & 1 while with initial value in case of mode 2. If TFx is not cleared, controller will not be able to detect next rollover.

6. Stop the Timer by clearing TRx bit. If TRx bit is not cleared the Timer will restart updating from 0000H after the rollover in case of modes 0 and 1 while with initial value in case of mode 2.

## (ii) Interrupt Method

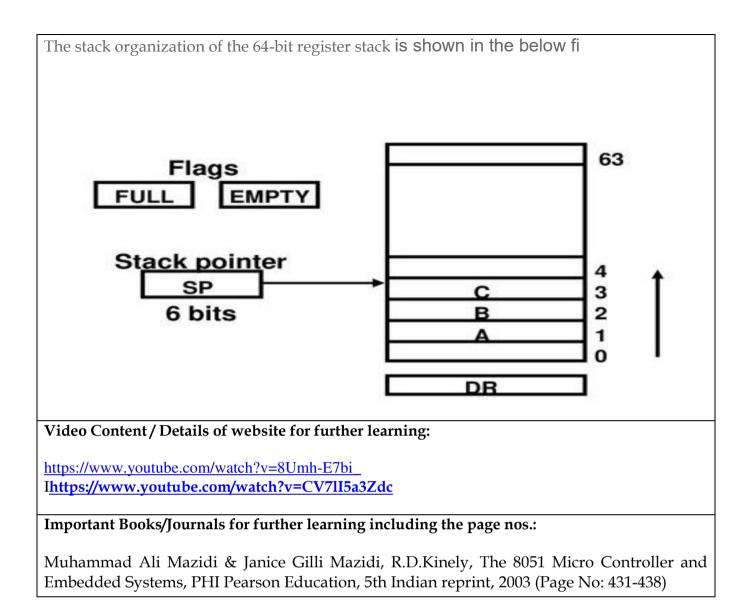

The **interrupt** method makes use of a register called **Interrupt Enable** (IE) register. An 8051 microcontroller has 6 hardware interrupts. The interrupts refer to a notification, communicated to the controller, by a hardware device or software, on receipt of which controller skips temporarily whatsoever it was doing and responds to the interrupt.

The controller starts the execution of an **Interrupt Service Routine** (ISR) or Interrupt Handler which is a piece of code that tells the processor or controller **what to do on receipt of an interrupt**. After the execution of ISR, controller returns to whatever it was doing earlier (before the interrupt was received).

The Interrupt Enable register has the following bits which enable or disable the hardware interrupts of 8051 microcontroller.

| IE: EA - | ET2 ES | ET1 EX1 | El |

|----------|--------|---------|----|

|----------|--------|---------|----|

When EA (IE.7) is set (=1), interrupts are enabled. When clear (EA=0), interrupts are disabled and controller does not respond to any interrupts.

ET0, ET1 & ET2 (IE.3, IE.4 & IE.5) are Timer interrupt bits. When set (high) the timer are enabled and when cleared (low) they are disabled. (8052 controllers have three Timers, so ET2 is its Timer 2 interrupt bit.) The ISR corresponding to these interrupts are executed when the TFx flags of respective Timers are raised. For more details on other IE register bits, refer <u>Interrupts with 8051</u>.

Note that IE register is bit addressable.

Timer programming using Timer interrupts involves following algorithm.

Configure the Timer mode by passing a hex value to TMOD register.

Load the initial values in the Timer low TLx and high THx byte.

Enable the Timer interrupt by passing hex value to IE register or setting required bits of IE register. For example,

| 0                 | -                              |

|-------------------|--------------------------------|

| IE = 0x82;        | enables Timer 0 interrupt      |

| $I\Gamma = 0.000$ | an alalaa Tina ay 1 in tayuu u |

IE = 0x88; enables Timer 1 interrupt

or

EA = 1;

ETO = 1; enables Timer 0 interrupt  $IE^7 = 1;$  enables Timer 1 interrupt  $IE^3 = 1;$  enables Timer 1 interrupt

Start the Timer by setting TRx bit.

Write Interrupt Service Routine (ISR) for the Timer interrupt. For example,

ISR definition for Timer 0 :

void ISR\_Timer0(void) interrupt 1

<Body of ISR>

}

{

```

ISR definition for Timer 1 :

```

```

void ISR_Timer1(void) interrupt 3

```

<Body of ISR>

}

{

6. If the Timer has to be stopped after once the interrupt has occurred, the ISR must contain the statement to stop the Timer.

```

For example,

void ISR_Timer1(void) interrupt 3

```

```

{

```

<Body of ISR>

TR1 =0;

}

If a routine written for Timer interrupt has to be repeated again and again, the Timer run bit need not be cleared. But it should be kept in mind that **Timer will start updating from 0000H** and **not the initial values in case of mode 0 and 1**. So the initial values must be reloaded in the interrupt service routine.

For example, void ISR\_Timer1(void) interrupt 3

```

{

```

<Body of ISR>

TH1 =0XFF;

//load with initial values if in mode 0 or 1  $\,$

TL1 = 0xFC;

}

Video Content / Details of website for further learning (if any):

https://www.engineersgarage.com/timers-8051-timer-programming/

# Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 Page No: 24-28

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

ECE

L11

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

#### Unit

: II - 8051 MICROCONTROLLER INTERFACING

Date of Lecture:

Topic of Lecture: Serial Port Programming

#### Introduction :

One of the 8051's many powerful features -integrated UART, known as a serial port easily read and write values to the serial port instead of turning on and off one of the I/ lines in rapid succession to properly "clock out" each individual bit, including start bi stop bits and parity bits.

#### Prerequisite knowledge for Complete understanding and learning of Topic:

- Processors and controllers

- Central processing unit

- Memory Devices

#### Detailed content of the Lecture:

#### Serial Port Programming: 8051 Serial Communication

One of the 8051's many powerful features -integrated *UART*, known as a serial port to easily read write values to the serial port instead of turning on and off one of the I/O lines in ransuccession to properly "clock out" each individual bit, including start bits, stop bits and parity bits

✓ Setting the Serial Port Mode configures it by specifying 8051 how many data bits

we want, the baud rate we will be using and how the baud rate will be determined. First, le present the "Serial Control" (SCON) SFR and define what each bit of the SFR represents:

## Table : Definition of SCON SFR

| Bit | Name | Bit<br>Address    | Explanation of Function                                               |

|-----|------|-------------------|-----------------------------------------------------------------------|

| 7   | SM0  | 9Fh               | Serial port mode bit 0                                                |

| 6   | SM1  | 9Eh               | Serial port mode bit 1.                                               |

| 5   | SM2  | 9Dh               | Mutli processor Communications Enable                                 |

| 4   | REN  | 9Ch               | Receiver Enable. This bit must be set in order to receive Characters. |

| 3   | TB8  | 9Bh               | Transmit bit 8. The 9th bit to transmit in mode 2 and 3.              |

| 2   | RB8  | 9AH               | Receive bit 8. The 9th bit received in mode 2 and 3.                  |

| 1   | T1   | 99h               | Transmit Flag. Set when a byte has been completely<br>Transmitted.    |

| 0   | RI   | <mark>98</mark> h | Receive Flag. Set when a byte has been completely Received.           |

**Table 5.3 Definition of SCON SFR**

Additionally, it is necessary to define the function of SM0 and SM1 by an additional table: Ta 5.4 SCON as serial Port

# **Table 5.4 Modes of SCON**

# Table 5.4 Modes of SCON

| SM0 | SM1 | Serial Mode | Explanation Baud Rate                  |

|-----|-----|-------------|----------------------------------------|

| 0   | 0   | 0           | 0 8-bit Shift Register Oscillator / 12 |

| 0   | 1   | 1           | 8-bit UART Set by Timer 1 (*)          |

| 1   | 0   | 2           | 9-bit UART Oscillator / 32 (*)         |

| 1   | 1   | 3           | 9-bit UART Set by Timer 1 (*)          |

The SCON SFR allows us to configure the Serial Port. The first four bits (bits 4 through are configuration bits:

Bits **SM0** and **SM1** is to set the *serial mode* to a value between 0 and 3, inclusive as in ta above selecting the Serial Mode selects the mode of operation (8-bit/9-bit, UART

or Shift Register) and also determines how the baud rate will be calculated. In modes 0 and 2 baud rate is fixed based on the oscillator's frequency. In modes 1 and 3 the baud rate is

variable based on how often Timer 1 overflows.

The next bit, SM2, is a flag for " Multiprocessor communication whenever a byte has be

received the 8051 will set the "RI" (Receive Interrupt) flag to let the program know that a byte I been received and that it needs to be processed.

However, when SM2 is set the "RI" flag will only be triggered if the 9th bit received wa "1". if SM2 is set and a byte is received whose 9th bit is clear, the RI flag will never be set .Y will almost always want to clear this bit so that the flag is set upon reception of *any* character.

The next bit, REN, is "Receiver Enable." is set indicate to data received via the serial port

The last four bits (bits 0 through 3) are operational bits. They are used when actually send and receiving data--they are not used to configure the serial port.

The TB8 bit is used in modes 2 and 3. In modes 2 and 3, a total of nine data bits are

transmitted. The first 8 data bits are the 8 bits of the main value, and the ninth bit is taken from TB8. If TB8 is set and a value is written to the serial port, the data's bits will be

written to the serial line followed by a "set" ninth bit. If TB8 is clear the ninth bit will be "clear."

The **RB8** also operates in modes 2 and 3and functions essentially the same way as TB8, I on the reception side. When a byte is received in modes 2 or 3, a total of nine bits are received. this case, the first eight bits received are the data of the serial byte received and the value of nineth bit received will be placed in RB8.**TI** means "Transmit Interrupt."

When a program writes a value to the serial port, a certain amount of time will pass before the individual bits of the byte are "clocked out" the serial port. If the program were to write anothe byte to the serial port before the first byte was completely output, the data being sent would garbled. Thus, the 8051 lets the program know that it has "clocked out" the last byte by setting TI bit.

When the TI bit is set, the program may assume that the serial port is "free" and ready send the next byte. Finally, the **RI** bit means "Receive Interrupt." It functions similarly to the "bit, but it indicates that a byte has been received. Whenever the 8051 has received a complete bit will trigger the RI bit to let the program know that it needs to read the value quickly, befa another byte is read.

Video Content / Details of website for further learning (if any):

https://www.brainkart.com/article/Serial-Port-Programming--8051-Serial-Communication\_7888/

Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedo Systems, PHI Pearson Education, 5th Indian reprint, 2003 (Page No: 28-32)

**Course Faculty**

# MUTHAYAMMAL ENGINEERING

# COLLEGE

L12C

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

LECTURE HANDOUTS

| ECE |

|-----|

|-----|

II/IV

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: II - 8051 MICROCONTROLLER INTERFACING Date of Lecture:

Topic of Lecture: Interrupts Programming

Rasipuram

#### Introduction :

**Interrupt** is one of the most important and powerful concepts and features in **microcontroller**/processor applications. Almost all the real world and real time systems built around microcontrollers and microprocessors make use of interrupts.

Prerequisite knowledge for Complete understanding and learning of Topic:

Programming of 8051

**Detailed content of the Lecture:**

#### What is Interrupt

The interrupts refer to a notification, communicated to the controller, by a hardware device or software, on receipt of which controller momentarily stops and responds to the interrupt. Whenever an interrupt occurs the controller completes the execution of the current instruction and starts the execution of an **Interrupt Service Routine** (ISR) or Interrupt Handler. **ISR** is a piece of code that tells the processor or controller what to do when the interrupt occurs. After the execution of ISR, controller returns back to the instruction it has jumped from (before the interrupt was received). The interrupts can be either **hardware interrupts** or **software interrupts**.

#### Why need interrupts

An application built around microcontrollers generally has the following structure. It takes input from devices like keypad, ADC etc; processes the input using certain algorithm; and generates an output which is either displayed using devices like seven segment, LCD or used further to operate other devices like motors etc. In such designs, controllers interact with the inbuilt devices like <u>timers</u> and other interfaced peripherals like sensors, serial port etc. The programmer needs to monitor their status regularly like whether the sensor is giving output, whether a signal has been received or transmitted, whether timer has finished counting, or if an interfaced device

needs service from the controller, and so on. This state of continuous monitoring is known as polling.

In polling, the microcontroller keeps checking the status of other devices; and while doing so it does no other operation and consumes all its processing time for monitoring. This problem can be addressed by using interrupts. In interrupt method, the controller responds to only when an interruption occurs. Thus in interrupt method, controller is not required to regularly monitor the status (flags, signals etc.) of interfaced and inbuilt devices.

To understand the difference better, consider the following. The polling method is very much similar to a salesperson. The salesman goes door-to-door requesting to buy its product or service. Like controller keeps monitoring the flags or signals one by one for all devices and caters to whichever needs its service. Interrupt, on the other hand, is very similar to a shopkeeper. Whosoever needs a service or product goes to him and apprises him of his/her needs. In our case, when the flags or signals are received, they notify the controller that they need its service.

#### Hardware & Software Interrupt

#### Hardware and Software interrupt

The interrupts in a controller can be either hardware or software. If the interrupts are generated by the controller's inbuilt devices, like timer interrupts; or by the interfaced devices, they are called the hardware interrupts. If the interrupts are generated by a piece of code, they are termed as software interrupts.

#### Multiple interrupts

What would happen if multiple interrupts are received by a microcontroller at the same instant? In such a case, the controller assigns priorities to the interrupts. Thus the interrupt with the highest priority is served first. However the priority of interrupts can be changed configuring the appropriate registers in the code.

**1. RESET interrupt** – This is also known as Power on Reset (POR). When the RESET interrupt is received, the controller restarts executing code from 0000H location. This is an interrupt which is not available to or, better to say, need not be available to the programmer.

**2. Timer interrupts** – Each Timer is associated with a Timer interrupt. A timer interrupt notifies the microcontroller that the corresponding Timer has finished counting.

**3. External interrupts** – There are two external interrupts EX0 and EX1 to serve external devices. Both these interrupts are active low. In <u>AT89C51</u>, P3.2 (INT0) and P3.3 (INT1) pins are available for external interrupts 0 and 1 respectively. An external interrupt notifies the microcontroller that an external device needs its service.

**4. Serial interrupt** – This interrupt is used for <u>serial communication</u>. When enabled, it notifies the controller whether a byte has been received or transmitted.

Video Content / Details of website for further learning (if any):

https://www.engineersgarage.com/interrupts-programming-8051-hardware-interrupts/

Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 Page No: 93-106

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

# ECE

II/IV

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

**Course Faculty** : Mrs.S.Punitha

Unit

: II -8051 MICROCONTROLLER INTERFACING Date of Lecture:

#### **Topic of Lecture:**

#### **Introduction :**

- LCDs can display numbers, characters, and graphics. To produce a proper  $\geq$ display, the information has to be periodically refreshed. This can be done by the CPU or internally by the LCD device itself.

- Keys in a keyboard are arranged in a matrix of rows and columns. The controller  $\geq$ access both rows and columns through ports. Using two ports, we can connect to an 8x8 or a 4x4 matrix keyboard.

#### Prerequisite knowledge for Complete understanding and learning of Topic: $\geq$

LCD & Keyboard Interfacing 8051

Detailed content of the Lecture:

#### LCD (LIQUID CRYSTAL DISPLAY) INTERFACE

LCDs can display numbers, characters, and graphics. To produce a proper display, the information has to be periodically refreshed. This can be done by the CPU or internally by the LCD device itself. Incorporating a refreshing controller into the LCD, relieves the CPU of this task and hence many LCDs have built-in controllers. These controllers also facilitate flexible programming for characters and graphics. Table shows the pin description of an LCD. from Optrex.

| Pin no. | Symbol  | External<br>connection | Function                                                                                                                                                            |

|---------|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Vss     |                        | Signal ground for LCM                                                                                                                                               |

| 2       | VDD     | Power supply           | Power supply for logic for LCM                                                                                                                                      |

| 3       | Vo      |                        | Contrast adjust                                                                                                                                                     |

| 4       | RS      | MPU                    | Register select signal                                                                                                                                              |

| 5       | R/W     | MPU                    | Read/write select signal                                                                                                                                            |

| 6       | E       | MPU                    | Operation (data read/write) enable signal                                                                                                                           |

| 7~10    | DB0~DB3 | MPU                    | Four low order bi-directional three-state data bus lines.<br>Used for data transfer between the MPU and the LCM.<br>These four are not used during 4-bit operation. |

| 11~14   | DB4~DB7 | MPU                    | Four high order bi-directional three-state data bus lines<br>Used for data transfer between the MPU                                                                 |

- ➤ Vss and VDD provide +5v and ground, V0 is used for controlling LCD contrast.

- ➢ If RS=0, the instruction command register is selected, allowing the user to send a command such as clear display, cursor at home, etc.

- ▶ If RS=1 the data register is selected, allowing the user to send data to be displayed on the LCD.

- > R/W input allows the user to Read/ Write the information to the LCD.

- > The enable pin is used by the LCD to latch information presented to its data pins.

- > The 8-bit data pins are used to send information to LCD.

- Section 5.1 discusses about command codes for writing the instructions on the LCD register. Section 5.2 gives an example program for displaying a character on the LCD.

#### LCD COMMAND CODES

The LCD's internal controller can accept several commands and modify the display accordingly. These commands would be things like:

- Clear screen

- ➢ Return home

- Decrement/Increment cursor

After writing to the LCD, it takes some time for it to complete its internal operations. During this time, it will not accept any new commands or data. Figure 5.4.1 shows the command codes of LCD and Figure 5.4.2 shows the LCD interfacing. We need to insert a time delay between any two commands or data sent to LCD.

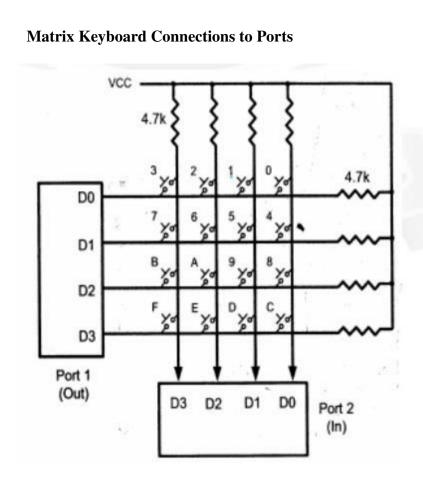

#### **KEYBOARD INTERFACING WITH 8051**

Keys in a keyboard are arranged in a matrix of rows and columns. The controller access both rows and columns through ports. Using two ports, we can connect to an 8x8 or a 4x4 matrix keyboard. When a key is pressed, a row and column make a contact, otherwise there is no contact. We will look at the details using a 4x4 keyboard.

#### 4X 4 KEYBOARD

Figure 5.4.31 shows a 4 x4 matrix connected to two ports

- The rows are connected to an output port(Port 1) and the columns are connected to an input port. (Port 2)

- If no key has been pressed, reading the input port will yield 1s for all columns since they are all connected to high (Vcc).

- If all the rows are grounded and a key is pressed, one of the columns will have 0 since the key pressed provides the path to ground.

- ➢ It is the function of the microcontroller to scan the keyboard continuously to detect and identify the key pressed.

#### **KEY SCAN**

To find out the key pressed , the controller grounds a row by sending a '0' on the corresponding line of the output port. It then reads the data at the columns using the input port. If data from columns is D3-D0=1111, then no key is pressed. If any bit of the column is '0', it indicates that a key is pressed in that column. In this example, the column is identified by the following values: 1110 – key pressed in column 0 1101 – key pressed in column 3

Video Content / Details of website for further learning (if any):

https://www.rcet.org.in/uploads/academics/rohini\_10051412485.pdf

**Important Books/Journals for further learning including the page nos.**:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 (Page No: 218-223)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408,Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

II/IV

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: II -8051 MICROCONTROLLER INTERFACING Date of Lecture:

**Topic of Lecture:**

ADC, DAC & Sensor

Interfacing

- Introduction :

- ADCs (analog-to-digital converters) are among the most widely used devices for data acquisition

- The digital-to-analog converter (DAC) is a device widely used to convert digital pulses to analog signals

Prerequisite knowledge for Complete understanding and learning of Topic:

- Architecture

- Pin diagram

**Detailed content of the Lecture:**

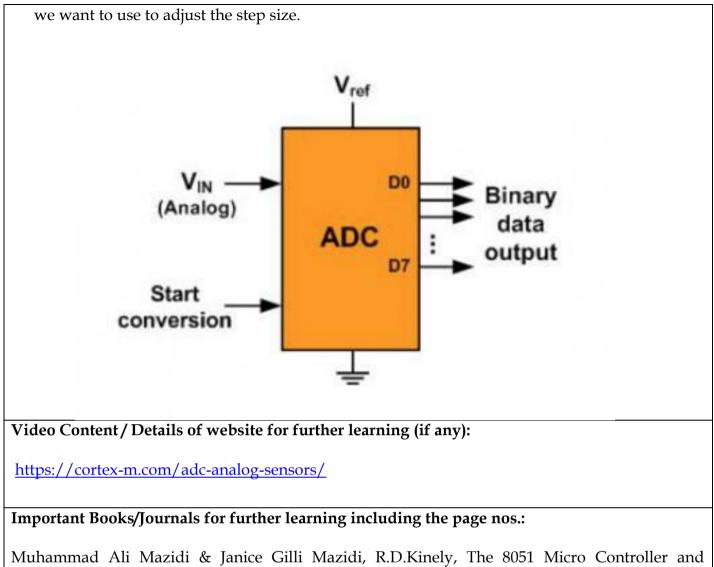

## **ADC Devices**

- ADCs (analog-to-digital converters) are among the most widely used devices for data acquisition

- A physical quantity, like temperature, pressure, humidity, and velocity, etc., is converted to electrical (voltage, current) signals using a device called a transducer, or sensor

- We need an analog-to-digital converter to translate the analog signals to digital numbers, so microcontroller can read them

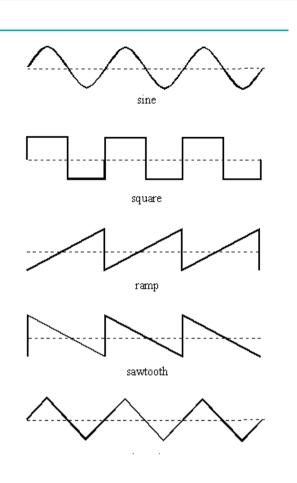

## **Digital to Analog Conversion**

- The conversion process: Digital code is converted to a proportional voltage or current Reference voltage determines the max output DAC can output

- > Analog (pseudo analog) output Finite number of output levels

- > Input weights Each bit of the input has a different weight

- Resolution (step size) Difference between two consecutive output levels smallest amount of change realizable at the output Weight of the LSB of input

## **Digital to Analog Conversion**

- Bipolar DACs Many DACs produce both positive and negative values 2's complement can be used to represent negative voltages

- We are going to focus on unipolar DACs

- ADCs (Analog-to-Digital Converters) are among the most widely used devices for data acquisition.

- A physical quantity, like temperature, pressure, humidity, and velocity, etc., is converted to electrical (voltage, current) signals using a device called a transducer or sensor

- We need an Analog-to-Digital Converter to translate the analog signals to digital numbers, so microcontroller can read and process them.

- An ADC has n-bit resolution where n can be 8, 10, 12, 16 or even 24 bits.

- The higher-resolution ADC provides a smaller step size, where step size is the smallest change that can be discerned by an ADC.

- In addition to resolution, conversion time is another major factor in judging an ADC.

- Conversion time is defined as the time it takes the ADC to convert the analog input to a digital (binary) number.

- In parallel ADC, we have 8 of more pins dedicated to bringing out the binary data, but in serial ADC we have only one pin for data out.

# ADC804 CHIP:

ADC804 IC is an 8-bit parallel analog-to-digital converter.

- > It works with +5 volts and has a resolution of 8bits.

- In ADC804 conversion time varies depending on the clocking signals applied to the CLK R and CLK IN pins, but it cannot be faster than 110µs.

- > It is the Pin out of ADC0804 in free running mode.

# STEPS TO BE FOLLOWED FOR DATA CONVERSION:

The following steps must be followed for data conversion by the ADC804 chip:

- > Make CS= 0 and send a L-to-H pulse to pin WR to start conversion.

- Monitor the INTR pin, if high keep polling but if low, conversion is complete, go to next step.

- > Make CS=0 and send a H-to-L pulse to pin RD to get the data out.

# Video Content / Details of website for further learning (if any):

https://www.rcet.org.in/uploads/academics/rohini\_40959333711.pdf

# Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 Page No: (70-75)

# MUTHAYAMMAL ENGINEERING

# COLLEGE

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna

University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

LECTURE HANDOUTS

ECE

II/IV

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: II -8051 MICROCONTROLLER INTERFACING Date of Lecture:

Topic of Lecture: External Memory Interface

#### Introduction :

An **external memory interface** is a bus protocol for communication from an integrated circuit, such as a microprocessor, to an external memory device located on a circuit board..

#### Prerequisite knowledge for Complete understanding and learning of Topic:

- Architecture

- External Memory

### **Detailed content of the Lecture:**

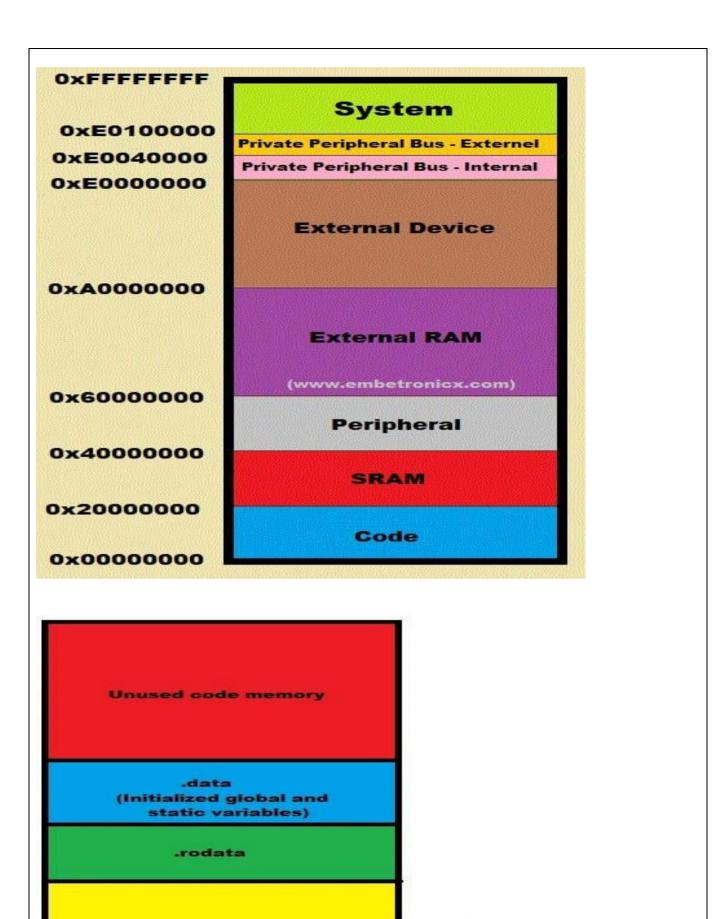

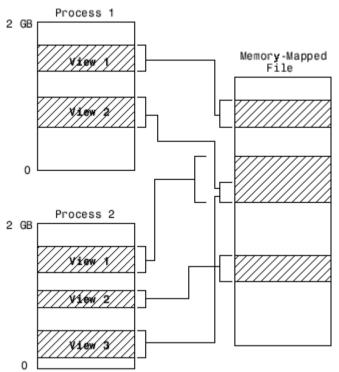

An **external memory interface** is a bus protocol for communication from an integrated circuit, such as a microprocessor, to an external memory device located on a circuit board. The memory is referred to as external because it is not contained within the internal circuitry of the integrated circuit and thus is externally located on the circuit board.

The external memory interface enables the processor to interface with third level caches, peripherals, and external memory.<sup>[1]</sup>

Some common external memory interfaces include:

- > DDR

- > DDR2

- > GDDR

# **DDR SDRAM**

### Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM)

It is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) class of memory integrated circuits used in computers. DDR SDRAM, also retroactively called DDR1 SDRAM, has been superseded by DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM and DDR5 SDRAM. None of its successors are forward or backward compatible with DDR1 SDRAM, meaning DDR2, DDR3, DDR4 and DDR5 memory modules will not work in DDR1-equipped motherboards, and vice versa.

Compared to single data rate (SDR) SDRAM, the DDR SDRAM interface makes higher

transfer rates possible by more strict control of the timing of the electrical data and clock signals. Implementations often have to use schemes such as phase-locked loops and self-calibration to reach the required timing accuracy.<sup>[4][5]</sup> The interface uses double pumping (transferring data on both the rising and falling edges of the clock signal) to double data bus bandwidth without a corresponding increase in clock frequency. One advantage of keeping the clock frequency down is that it reduces the signal integrity requirements on the circuit board connecting the memory to the controller. The name "double data rate" refers to the fact that a DDR SDRAM with a certain clock frequency achieves nearly twice the bandwidth of a SDR SDRAM running at the same clock frequency, due to this double pumping.

With data being transferred 64 bits at a time, DDR SDRAM gives a transfer rate (in bytes/s) of (memory bus clock rate) × 2 (for dual rate) × 64 (number of bits transferred) / 8 (number of bits/byte). Thus, with a bus frequency of 100 MHz, DDR SDRAM gives a maximum transfer rate of 1600 MB/s.

# **DDR2 SDRAM**

**Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM)** is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It superseded the original DDR SDRAM specification, and was itself superseded by DDR3 SDRAM (launched in 2007). DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR.

In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle.

Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better latency. Alternatively, DDR2 memory operating at twice the external data bus clock rate as DDR may provide twice the bandwidth with the same latency. The best-rated DDR2 memory modules are at least twice as fast as the best-rated DDR memory modules. The maximum capacity on commercially available DDR2 DIMMs is 8GB, but chipset support and availability for those DIMMs is sparse and more common 2GB per DIMM are used

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=0uKdlNT0EMU

#### Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 Page No: 70-75

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

10/

Course Name with Code: 19ECC07/ MICROCONTROLLER BASED SYSTEM DESIGN

Course Faculty : Mrs.S.Punitha

Unit

: II -8051 MICROCONTROLLER INTERFACING Date of Lecture:

Topic of Lecture: Stepper Motor

### Introduction :

A **stepper motor**, also known as **step motor** or **stepping motor**, is a brushless DC electric motor that divides a full rotation into a number of equal steps.

Prerequisite knowledge for Complete understanding and learning of Topic: ➤ Stepper Motor

**Detailed content of the Lecture:**

# Stepper motor

A **stepper motor**, also known as **step motor** or **stepping motor**, is a brushless DC electric motor that divides a full rotation into a number of equal steps. The motor's position can be commanded to move and hold at one of these steps without any position sensor for feedback (an open-loop controller), as long as the motor is correctly sized to the application in respect to torque and speed.

Switched reluctance motors are very large stepping motors with a reduced pole count, and generally are closed-loop commutated.

#### Mechanism:

Brushed DC motors rotate continuously when DC voltage is applied to their terminals. The stepper motor is known for its property of converting a train of input pulses (typically square waves) into a precisely defined increment in the shaft's rotational position. Each pulse rotates the shaft through a fixed angle.

Stepper motors effectively have multiple "toothed" electromagnets arranged as a stator around a central rotor, a gear-shaped piece of iron. The electromagnets are energized by an external driver circuit or a micro controller. To make the motor shaft turn, first, one electromagnet is given power, which magnetically attracts the gear's teeth. When the gear's teeth are aligned to the first electromagnet, they are slightly offset from the next electromagnet. This means that when the next electromagnet is turned on and the first is turned off, the gear rotates slightly to align with the next one. From there the process is repeated. Each of those rotations is called a "step", with an integer number of steps making a full rotation. In that way, the motor can be turned by a precise angle.

The circular arrangement of electromagnets is divided into groups, each group called a phase, and there is an equal number of electromagnets per group. The number of groups is chosen by the designer of the stepper motor. The electromagnets of each group are interleaved with the electromagnets of other groups to form a uniform pattern of arrangement. For example, if the stepper motor has two groups identified as A or B, and ten electromagnets in total, then the grouping pattern would be ABABABABA.

Electromagnets within the same group are all energized together. Because of this, stepper motors with more phases typically have more wires (or leads) to control the motor.

# Types:

There are three main types of stepper motors:

- 1. Permanent magnet stepper

- 2. Variable reluctance stepper

- 3. Hybrid synchronous stepper

Permanent magnet motors use a permanent magnet (PM) in the rotor and operate on the attraction or repulsion between the rotor PM and the stator electromagnets.

Pulses move the rotor in discrete steps, CW or CCW. If left powered at a final step a strong detent remains at that shaft location. This detent has a predictable spring rate and specified torque limit; slippage occurs if the limit is exceeded. If current is removed a lesser detent still remains, therefore holding shaft position against spring or other torque influences. Stepping can then be resumed while reliably being synchronized with control electronics.

Variable reluctance (VR) motors have a plain iron rotor and operate based on the principle that minimum reluctance occurs with minimum gap, hence the rotor points are attracted toward the stator magnet poles. Whereas hybrid synchronous are a combination of the permanent magnet and variable reluctance types, to maximize power in a small size.<sup>[2]</sup>

VR motors have power on detents but do not have power off detents.

# Video Content / Details of website for further learning (if any):

https://en.wikipedia.org/wiki/Stepper\_motor

**Important Books/Journals for further learning including the page nos.:**

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 Page No: 109-131

**Course Faculty**

# MUTHAYAMMAL ENGINEERING

# COLLEGE

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna

University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS