(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L - 01

II/III/A

CSE

### :16CSD12& COMPUTER ARCHITECTURE

Course Faculty

**Course Name with Code**

• D VINITIDDIVA

ι

| Lourse Faculty                                                                | : K.VINUPK       | IYA                         |                                       |

|-------------------------------------------------------------------------------|------------------|-----------------------------|---------------------------------------|

| Jnit                                                                          | : I - BASIC      | STRUCTURE OF CO             | MPUTERS                               |

|                                                                               |                  |                             | Date of Lecture:                      |

| Topic of Lecture: Functional U                                                | Jnits            |                             |                                       |

| Introduction:                                                                 |                  |                             |                                       |

| Functional units are a part                                                   | of a CPU that    | performs the operation      | ns and calculations called for by the |

|                                                                               |                  |                             | of the CPU (Central Processing Unit)  |

| that performs the operations a                                                | nd calculations  | called for by the compu     | ater program.                         |

| Learning objective:                                                           |                  | 1                           |                                       |

| To understand the basis                                                       |                  |                             | - (T)-                                |

| Prerequisite knowledge for C                                                  | _                | istanding and learning      |                                       |

| <ul><li>Evolution of Computer</li><li>Basic Operation of a Computer</li></ul> |                  |                             |                                       |

| Detailed content of the Lecture                                               |                  |                             |                                       |

| FUNCTIONAL UNITS                                                              | ie.              |                             |                                       |

| A computer consists of 5 funct                                                | tionally indeper | ndent main parts:           |                                       |

| 1) Input                                                                      |                  |                             |                                       |

| 2) Memory                                                                     |                  |                             |                                       |

| 3) ALU                                                                        |                  |                             |                                       |

| 4) Output &                                                                   |                  |                             |                                       |

| 5) Control units.                                                             |                  |                             |                                       |

|                                                                               |                  |                             |                                       |

|                                                                               |                  |                             |                                       |

|                                                                               |                  | Memory                      |                                       |

|                                                                               |                  |                             |                                       |

|                                                                               |                  |                             |                                       |

|                                                                               |                  |                             | 1.64                                  |

|                                                                               | Icout            |                             | Arithmetic                            |

|                                                                               | Input            |                             | and<br>logic                          |

|                                                                               |                  |                             | - decision-                           |

|                                                                               |                  | Interconnection             |                                       |

|                                                                               |                  | network                     |                                       |

|                                                                               | Output           |                             | Control                               |

|                                                                               |                  |                             | EDUCTION OF BEEN                      |

|                                                                               |                  |                             |                                       |

|                                                                               | I/O              |                             | Processor                             |

|                                                                               | Figure 1.1       | Basic functional units of a | computer                              |

|                                                                               |                  |                             |                                       |

|                                                                               |                  |                             |                                       |

|                                                                               |                  |                             |                                       |

|                                                                               |                  |                             |                                       |

**Input Units** are used by the computer to read the data. The most commonly used input devices are keyboards, mouse, joysticks, trackballs, microphones, etc.

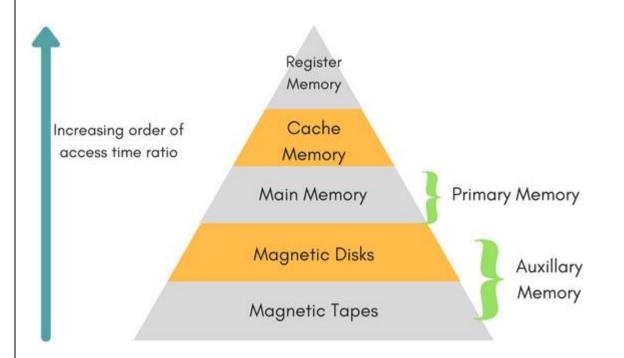

**Memory unit** can be referred to as the storage area in which programs are kept which are running, and that contains data needed by the running programs. The Memory unit can be categorized in two ways namely, primary memory and secondary memory.

**ALU**, most of all the arithmetic and logical operations of a computer are executed in the ALU (Arithmetic and Logical Unit) of the processor. It performs arithmetic operations like addition, subtraction, multiplication, division and also the logical operations like AND, OR, NOT operations.

**Outputs** are pieces of equipment that are used to generate information or any other response processed by the computer. These devices display information that has been held or generated within a computer. The most common example of an output device is a monitor.

**Control Unit** is a component of a computer's central processing unit that coordinates the operation of the processor. It tells the computer's memory, arithmetic/logic unit and input and output devices how to respond to a program's instructions. The control unit is also known as the nerve center of a computer system.

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=Ev1TQ6qEfzU https://www.youtube.com/watch?v=U7elB4HpY3M https://www.youtube.com/watch?v=UDvpNeTRBs0

#### Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture: By Bester field ,Page no: 3

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 1-6

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L - 02

| II/III/A |

|----------|

|----------|

| Course Name with Code | : 16CSD12& COMPUTER ARCHITECTURE   |

|-----------------------|------------------------------------|

| Course Faculty        | : R.VINUPRIYA                      |

| Unit                  | : I - BASIC STRUCTURE OF COMPUTERS |

|                       | Date of Lecture:                   |

Topic of Lecture: Basic Operational concepts

#### Introduction:

An Instruction consists of 2 parts, 1) Operation code (Opcode) and 2) Operands. The data/operands are stored in memory. The individual instruction is brought from the memory to the processor.

#### Learning objective:

• To understand the basic structure of a digital computer

Prerequisite knowledge for Complete understanding and learning of Topic:

- Evolution of Computer Systems

- Basic Operation of a Computer

### Detailed content of the Lecture:

## Let us see a typical instruction

ADD LOCA, RO

This instruction is an **addition operation**. The following are the steps to execute the instruction: **Step 1:** Fetch the instruction from main-memory into the processor.

Step 2: Fetch the operand at location LOCA from main-memory into the processor.

**Step 3:** Add the memory operand (i.e. fetched contents of LOCA) to the contents of register R0.

**Step 4:** Store the result (sum) in R0.

The same instruction can be realized using **2 instructions** as:

#### Load LOCA, R1 Add R1, R2

The following are **the steps to execute the instruction**:

**Step 1:** Fetch the instruction from main-memory into the processor.

Step 2: Fetch the operand at location LOCA from main-memory into the register R1.

Step 3: Add the content of Register R1 and the contents of register R0.

Step 4: Store the result (sum) in R0.

## MAIN PARTS OF PROCESSOR

- The **processor** contains ALU, control-circuitry and many registers.

- The processor contains "n" general-purpose registers  $R_0$  through  $R_{n-1}$ .

- The IR holds the instruction that is currently being executed.

- The **control-unit** generates the timing-signals that determine when a given action is to take place.

- The **PC** contains the memory-address of the next-instruction to be fetched & executed.

- During the execution of an instruction, the contents of PC are updated to point to next instruction.

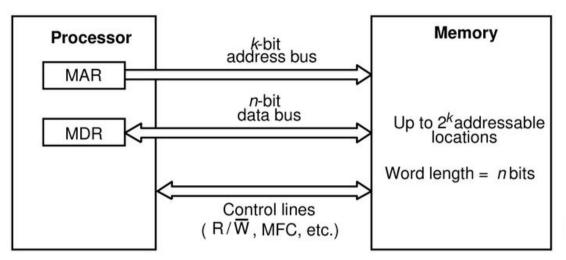

- The **MAR** holds the address of the memory-location to be accessed.

- The **MDR** contains the data to be written into or read out of the addressed location.

# STEPS TO EXECUTE AN INSTRUCTION

- 1) The address of first instruction (to be executed) gets loaded into PC.

- 2) The contents of PC (i.e. address) are transferred to the MAR & control-unit issues Read signal to memory.

3) After certain amount of elapsed time, the first instruction is read out of memory and placed into MDR.

4) Next, the contents of MDR are transferred to IR. At this point, the instruction can be decoded & executed.

5) To fetch an operand, it's address is placed into MAR & control-unit issues Read signal. As a result, the operand is transferred from memory into MDR, and then it is transferred from MDR to ALU.

- 6) Likewise required number of operands is fetched into processor.

- 7) Finally, ALU performs the desired operation.

- 8) If the result of this operation is to be stored in the memory, then the result is sent to the MDR.

9) The address of the location where the result is to be stored is sent to the MAR and a Write cycle is initiated.

10) At some point during execution, contents of PC are incremented to point to next instruction in the program.

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=bjFHDOecebI

https://www.youtube.com/watch?v=tAxSbdxwcw4

https://www.youtube.com/watch?v=Ot09heN1rVI

Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By Bester field , page no: 7

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no:6-9

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L - 03

II/III/A

CSE

: 16CSD12& COMPUTER ARCHITECTURE

**Course Faculty**

**Course Name with Code**

: R.VINUPRIYA

Unit

: I - BASIC STRUCTURE OF COMPUTERS

Date of Lecture:

Topic of Lecture: Bus Structures

### Introduction:

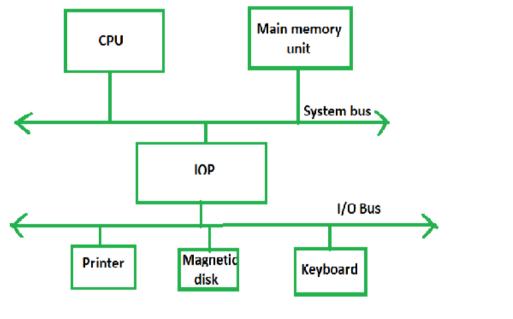

A bus is a group of lines that serves as a connecting path for several devices. A bus may be lines or wires. The lines carry data or address or control signal. There are 2 types of Bus structures: 1) Single Bus Structure and 2) Multiple Bus Structure.

#### Learning objective:

• To understand the basic structure of a digital computer

Prerequisite knowledge for Complete understanding and learning of Topic:

- Evolution of Computer Systems

- Basic Operation of a Computer

### Detailed content of the Lecture:

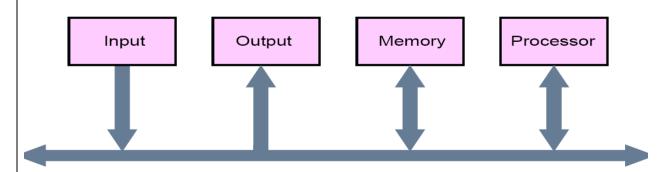

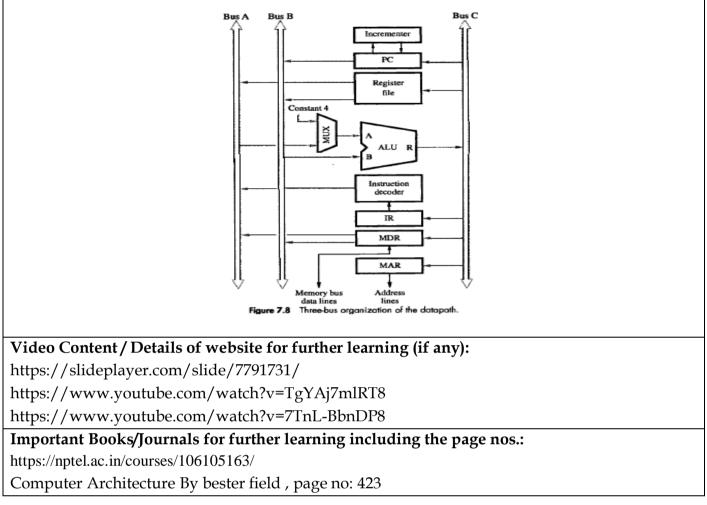

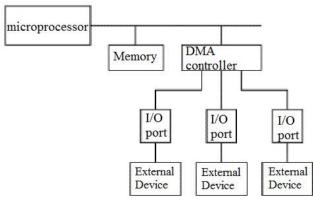

A group of lines that serves a connecting path for several devices is called a bus. In addition to the lines that carry the data, the bus must have lines for address and control purposes. The simplest way to interconnect functional units is to use a single bus, as shown below

## Single Bus Structure

Because the bus can be used for only one transfer at a time, only 2 units can actively use the bus at any given time. Bus control lines are used to arbitrate multiple requests for use of the bus.

Drawbacks: The devices connected to a bus vary widely in their speed of operation.

Some devices are relatively slow, such as printer and keyboard.

Some devices are considerably fast, such as optical disks.

Memory and processor units are the fastest parts of a computer.

Efficient transfer mechanism thus is needed to cope with this problem. A common approach is to include buffer registers with the devices to hold the information during transfers. An approach is to use two-bus structure and an additional transfer mechanism.

Advantages: Low cost & Flexibility for attaching peripheral devices.

### Multiple Bus Structure

Systems that contain multiple buses achieve more concurrency in operations. Two or more transfers can be carried out at the same time.

Advantage: Better performance.

Disadvantage: Increased cost.

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=TgYAj7mlRT8

https://www.youtube.com/watch?v=4w\_5Wp9IrJM

https://www.youtube.com/watch?v=uHqbE3JiDPY

### Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By Bester field, page no: 9

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 9-10

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

L - 04

| II/III/A |

|----------|

|----------|

| Course Name with Code | : 16CSD12& COMPUTER ARCHITECTURE   |

|-----------------------|------------------------------------|

| Course Faculty        | : R.VINUPRIYA                      |

| Unit                  | : I - BASIC STRUCTURE OF COMPUTERS |

|                       | Date of Lecture:                   |

Topic of Lecture: Software Performance

#### Introduction:

The most important measure of the performance of a computer is how quickly it can execute programs. The speed with which a computer executes program is affected by the design of its hardware.

#### Learning objective:

• To understand the basic structure of a digital computer

#### Prerequisite knowledge for Complete understanding and learning of Topic:

- Evolution of Computer Systems

- Basic Operation of a Computer

#### Detailed content of the Lecture:

### PERFORMANCE

- The most important measure of performance of a computer is how quickly it can execute programs.

- The speed of a computer is affected by the design of

- 1) Instruction-set.

- 2) Hardware & the technology in which the hardware is implemented.

- 3) Software including the operating system.

• Because programs are usually written in a HLL, performance is also affected by the compiler that translates programs into machine language. (HLL à High Level Language).

• For best performance, it is necessary to design the compiler, machine instruction set and hardware in a coordinated way.

### PROCESSOR CLOCK

- Processor circuits are controlled by a timing signal called a **Clock**.

- The clock defines regular time intervals called **Clock Cycles**.

- Relation between P and R is given by

$$R = \frac{1}{P}$$

• R is measured in cycles per second.

#### **BASIC PERFORMANCE EQUATION**

• Let T = Processor time required to executed a program. N = Actual

number of instruction executions.

S = Average number of basic steps needed to execute one

machine instruction. R = Clock rate in cycles per second.

• The program execution time is given by

$$T = \frac{N \times S}{R}$$

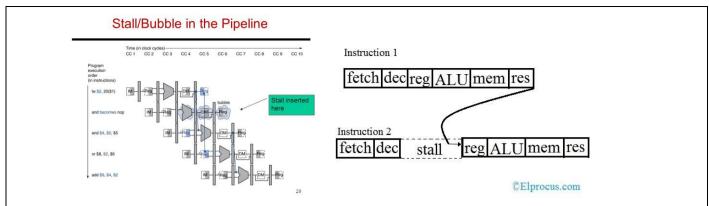

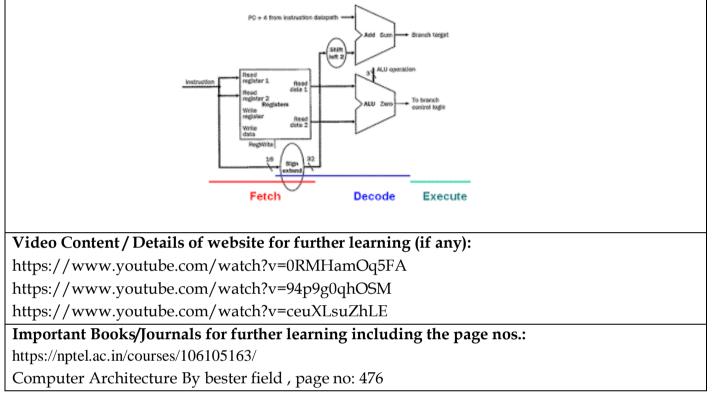

### PIPELINING AND SUPER SCALAR OPERATIONS

- A substantial improvement in performance can be achieved by overlapping the execution of successive instructions using a technique called pipelining

- A higher degree of concurrency can be achieved if multiple instructions pipelines are implemented in the processor.

- Multiple functional units are used creating parallel paths through which different instructions can be executed in parallel

- Hence, it becomes possible to start the execution of several instructions in every clock cycle. This mode of operation is called superscalar execution

## Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=TgYAj7mlRT8

https://www.youtube.com/watch?v=4w\_5Wp9IrJM

https://www.youtube.com/watch?v=uHqbE3JiDPY

Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By Bester field, page no: 9

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 12-16

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L - 05

CSE

| Course Name with Code | : 16CSD12& COMPUTER ARCHITECTURE   |

|-----------------------|------------------------------------|

| Course Faculty        | : R.VINUPRIYA                      |

| Unit                  | : I - BASIC STRUCTURE OF COMPUTERS |

|                       | Date of Lecture:                   |

Topic of Lecture: Memory Location & Addresses

#### Introduction:

**Memory** consists of many millions of storage cells (flip-flops). Each cell can store a bit of information i.e. 0 or 1. Each group of n bits is referred to as a word of information, and n is called the **word length**. The word length can vary from 8 to 64 bits. A unit of 8 bits is called a **byte**. **Learning objective:**

• To understand the basic structure of a digital computer

### Prerequisite knowledge for Complete understanding and learning of Topic:

- Evolution of Computer Systems

- Basic Operation of a Computer

### Detailed content of the Lecture:

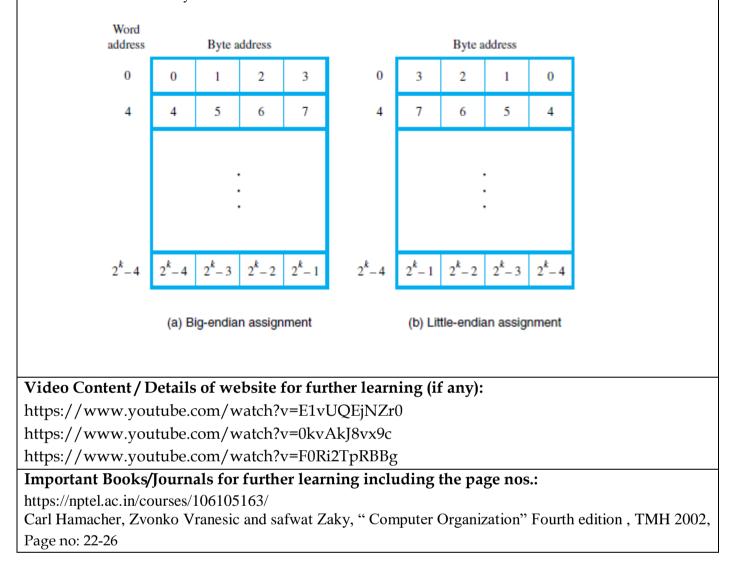

Accessing the memory to store or retrieve a single item of information (word/byte) requires distinct addresses for each item location. (It is customary to use numbers from 0 through  $2^{k-1}$  as the addresses of successive-locations in the memory). If  $2^{k}$  = no. of addressable locations; then  $2^{k}$  addresses constitute the address-space of the computer. For example, a 24-bit address generates an address-space of  $2^{24}$  locations (16 MB).

### **BYTE-ADDRESSABILITY**

- In byte-addressable memory, successive addresses refer to successive byte locations in the memory.

- Byte locations have addresses 0, 1, 2. . . .

- If the word-length is 32 bits, successive words are located at addresses 0, 4, 8. . with each word having 4 bytes.

•

## **BIG-ENDIAN & LITTLE-ENDIAN ASSIGNMENTS**

- There are two ways in which byte-addresses are arranged (Figure 2.3).

- **1) Big-Endian:** Lower byte-addresses are used for the more significant bytes of the word.

2) Little-Endian: Lower byte-addresses are used for the less significant bytes of the

#### word

• In both cases, byte-addresses 0, 4, 8. . . . are taken as the addresses of successive words in the memory.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L - 06

CSE

| Course Name with Code | : 16CSD12& COMPUTER ARCHITECTURE   |

|-----------------------|------------------------------------|

| Course Faculty        | : R.VINUPRIYA                      |

| Unit                  | : I - BASIC STRUCTURE OF COMPUTERS |

|                       | Date of Lecture:                   |

Topic of Lecture: Memory Operations

#### Introduction:

**Memory Operations**. There are two key **operations** on **memory**: fetch (address) returns value without changing the value stored at that address. store (address, value) writes new value into the cell at the given address.

#### Learning objective:

• To understand the basic structure of a digital computer

Prerequisite knowledge for Complete understanding and learning of Topic:

Memory Locations & Addresses

#### Detailed content of the Lecture:

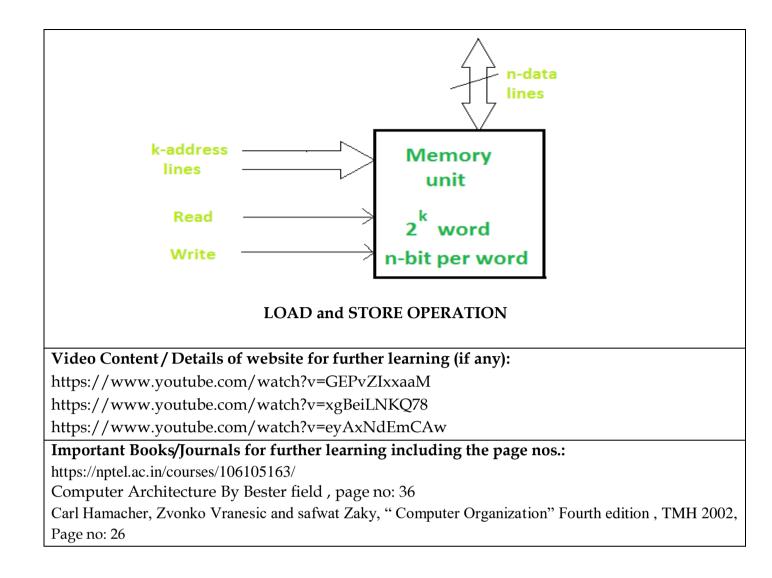

The **Load operation** transfers a copy of the contents of a specific memory-location to the processor. The memory contents remain unchanged.

### Steps for Load operation:

- 1) Processor sends the address of the desired location to the memory.

- 2) Processor issues "read" signal to memory to fetch the data.

- 3) Memory reads the data stored at that address.

- 4) Memory sends the read data to the processor.

The **Store operation** transfers the information from the register to the specified memory-location. This will destroy the original contents of that memory-location.

#### Steps for Store operation are:

- 1) Processor sends the address of the memory-location where it wants to store data.

- 2) Processor issues "write" signal to memory to store the data.

- 3) Content of register (MDR) is written into the specified memory-location.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

| L - 07 |

|--------|

|--------|

CSE

| Course Name with Code | : 16CSD12& COMPUTER ARCHITECTURE   |

|-----------------------|------------------------------------|

| Course Faculty        | : R.VINUPRIYA                      |

| Unit                  | : I - BASIC STRUCTURE OF COMPUTERS |

|                       | Data of Lactura                    |

Date of Lecture:

Topic of Lecture: Instructions and Instruction Sequencing

#### Introduction:

**Instruction sequencing,** the order in which the instructions in a program are carried out. Normally the sequence proceeds in a linear fashion through the program, and the address of the instructions is obtained from the program counter in the control unit.

#### Learning objective:

- To understand the basic structure of a digital computer

- Prerequisite knowledge for Complete understanding and learning of Topic:

- Memory Locations & Addresses

- Memory Operations

#### Detailed content of the Lecture:

A computer must have instructions capable of performing 4 types of operations:

- 1) Data transfers between the memory and the registers (MOV, PUSH, POP, XCHG).

- 2) Arithmetic and logic operations on data (ADD, SUB, MUL, DIV, AND, OR, NOT).

- 3) Program sequencing and control (CALL.RET, LOOP, INT).

- 4) I/0 transfers (IN, OUT).

### **REGISTER TRANSFER NOTATION (RTN)**

| Location      | Hardware Binary Address | Example           |

|---------------|-------------------------|-------------------|

| Memory        | LOC, PLACE, NUM         | R1 [LOC]          |

| Processor     | R0, R1, R2              | [R3] ← [R1] +[R2] |

| I/O Registers | DATAIN, DATAOUT         | R1 ← DATAIN       |

### ASSEMBLY LANGUAGE NOTATION

| Assembly Language Format | Description                                                   |  |  |

|--------------------------|---------------------------------------------------------------|--|--|

| Move LOC, R1             | Transfer data from memory-location LOC to register R1. The    |  |  |

|                          | ntents of LOC are unchanged by the execution of this          |  |  |

|                          | struction, but the old contents of                            |  |  |

|                          | register R1 are overwritten.                                  |  |  |

| Add R1, R2, R3           | Add the contents of registers R1 and R2, and places their sum |  |  |

|                  | into register R3.                    |             |

|------------------|--------------------------------------|-------------|

| BASIC INSTRUC    | ΓΙΟΝ TYPES                           |             |

| Instruction Type | Syntax                               | Example     |

| Three Address    | Opcode Source1, Source2, Destination | Add A, B, C |

| Two Address      | Opcode Source, Destination           | Add A, B    |

| One Address      | Opcode Source/Destination            | Load A      |

|                  |                                      | Add B       |

|                  |                                      | Store C     |

| Zero Address     | Opcode [no Source/Destination]       | Push        |

## INSTRUCTION EXECUTION & STRAIGHT-LINE SEQUENCING The program is executed as follows:

- 1. Initially, the address of the first instruction is loaded into PC.

- 2. Then, the processor control circuits use the information in the PC to fetch and execute instructions, one at a time, in the order of increasing addresses. This is called *Straight-Line sequencing*.

- 3. During the execution of each instruction, PC is incremented by 4 to point to next instruction.

# There are 2 phases for Instruction Execution:

- 1. **Fetch Phase:** The instruction is fetched from the memory-location and placed in the IR.

- 2. **Execute Phase:** The contents of IR are examined to determine which operation is to be performed. The specified-operation is then performed by the processor.

## Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=dPa4T\_EZ7Gs

https://www.youtube.com/watch?v=SFsnysyVhzA

https://www.youtube.com/watch?v=gfFgPvEDNYU

## Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By Bester field , page no: 37

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 26-34.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L -08

| Course Name with Code | : 16CSD12& COMPUTER ARCHITECTURE   |

|-----------------------|------------------------------------|

| Course Faculty        | : R.VINUPRIYA                      |

| Unit                  | : I - BASIC STRUCTURE OF COMPUTERS |

|                       | Detection                          |

Date of Lecture:

Topic of Lecture: Addressing modes, Assembly Language

#### Introduction:

Part of the programming flexibility for each processor is the number and different kind of ways the programmer can refer to data stored in the memory or I/O device. The different ways that a processor can access date are referred to as addressing schemes or addressing modes.

#### Learning objective:

• To understand the basic structure of a digital computer

Prerequisite knowledge for Complete understanding and learning of Topic:

- Memory Operations

- Memory Locations & Addresses

#### Detailed content of the Lecture:

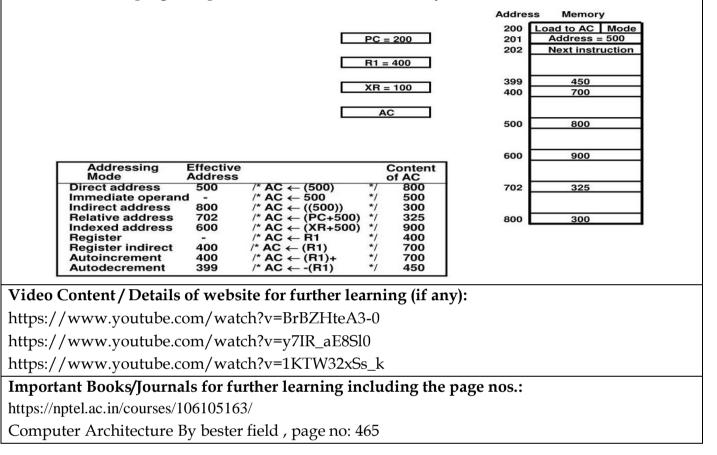

## IMPLEMENTATION OF VARIABLE AND CONSTANTS

- Variable is represented by allocating a memory-location to hold its value.

- Thus, the value can be changed as needed using appropriate instructions.

- There are 2 accessing modes to access the variables:

- 1) Register Mode

- 2) Absolute Mode

## **Register Mode**

- The operand is the contents of a register.

- The name (or address) of the register is given in the instruction.

- Registers are used as temporary storage locations where the data in a register are accessed.

- For example, the instruction

Move R1, R2; Copy content of register R1 into register R2.

### Absolute (Direct) Mode

- The operand is in a memory-location.

- The address of memory-location is given explicitly in the instruction.

- The absolute mode can represent global variables in the program.

- For example, the instruction

Move LOC, R2; Copy content of memory-location LOC into register R2.

### Immediate Mode

- The operand is given explicitly in the instruction.

- For example, the instruction

*Move* #200, *R0*; Place the value 200 in register R0.

• Clearly, the immediate mode is only used to specify the value of a source-operand.

## Indirect Mode

- The EA of the operand is the contents of a register (or memory-location).

- The register (or memory-location) that contains the address of an operand is called a **Pointer**.

- We denote the indirection by

$\rightarrow$  name of the register or

$\rightarrow$  new address given in the instruction.

### INDEXING AND ARRAYS

- A different kind of flexibility for accessing operands is useful in dealing with lists and arrays. **Index mode**

- The operation is indicated as X(Ri)

where X=the constant value which defines an offset (also called a displacement). Ri=the name of the index registers which contains address of a new location.

• The effective-address of the operand is given by EA=X+[Ri]

## **RELATIVE MODE**

• This is similar to index-mode with one difference:

The effective-address is determined using the PC in place of the general-purpose register Ri.

• The operation is indicated as X(PC).

# ADDITIONAL ADDRESSING MODES

- 1. Auto Increment Mode

- 2. Auto Decrement Mode

## Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=3QAdd1ZiIVo

https://www.youtube.com/watch?v=1VnVLJR7EZI

https://www.youtube.com/watch?v=KQ72sSKy8B8

Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By Bester field, page no: 48

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 34-41.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

| L | - | 09 |  |

|---|---|----|--|

|   |   |    |  |

II/III/A

| Course Name with Code | : 16CSD12& COMPUTER ARCHITECTURE   |

|-----------------------|------------------------------------|

| Course Faculty        | : R.VINUPRIYA                      |

| Unit                  | : I - BASIC STRUCTURE OF COMPUTERS |

Date of Lecture:

Topic of Lecture: Basic I/O Operations, Stacks and Queues

#### Introduction:

The problem of moving a character-code from the keyboard to the processor. For this transfer, buffer-register DATAIN & a status control flags (SIN) are used.

### Learning objective:

• To understand the basic structure of a digital computer

### Prerequisite knowledge for Complete understanding and learning of Topic:

- Basic operational concepts

- Instructions and instruction sequencing

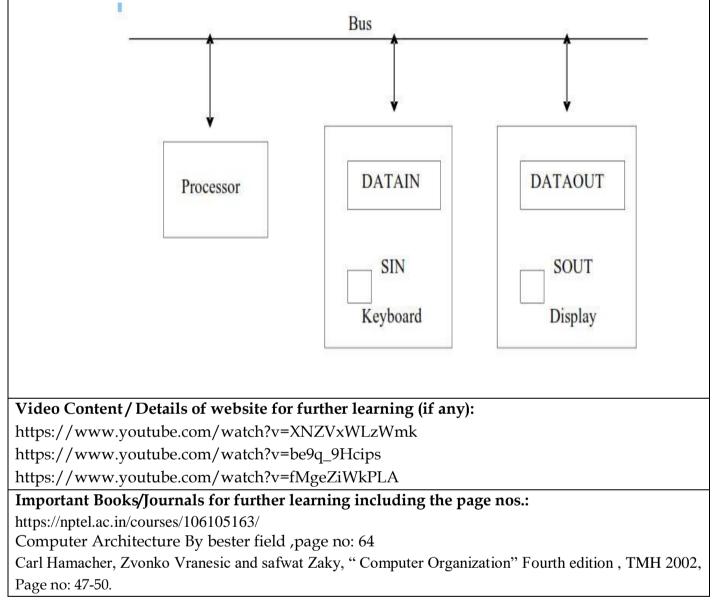

#### Detailed content of the Lecture: BASIC INPUT/OUTPUT OPERATIONS

- A simple way of performing I/O tasks is to use a method known as program-controlled I/O

- The rate of data transfer from the keyboard to a computer is limited by the typing speed of the user, which is unlikely to exceed a few characters per second.

- The rate of output transfers from the computer to the display is much higher.

- It is determined by the rate at which characters can be transmitted over the link between the computer and the display device, typically several thousand characters per second.

- However, this is still much slower than the speed of a processor that can execute many millions of instructions per second.

- The difference in speed between the processor and I/O devices creates the need for mechanisms to synchronize the transfer of data between them

• When a key is pressed, the corresponding ASCII code is stored in a **DATAIN** register associated with the keyboard.

> **SIN=1**, When a character is typed in the keyboard. This informs the processor that a valid character is in DATAIN.

> **SIN=0**, When the character is transferred to the processor.

• An analogous process takes place when characters are transferred from the processor to the display. For this transfer, buffer-register DATAOUT & a status control flag

SOUT are used.

- > **SOUT=1**, When the display is ready to receive a character.

- > **SOUT=0**, When the character is being transferred to DATAOUT.

• The buffer registers DATAIN and DATAOUT and the status flags SIN and SOUT are part of circuitry commonly known as a **device interface**.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L - 10

| II/III/A |

|----------|

|----------|

| Course Name with Code                 | : 16CSD12& COMPUTER ARCHITEC                  | CTURE                        |

|---------------------------------------|-----------------------------------------------|------------------------------|

| Course Faculty                        | : R.Vinupriya                                 |                              |

| Unit                                  | : II - Arithmetic and Logic Unit              | Date of Lecture:             |

| Topic of Lecture: Addition a          | nd Subtraction of Signed Numbers              |                              |

| Introduction:                         |                                               |                              |

| The addition, Subtraction             | on, multiplication and division are           | the four basic arithmetic    |

| instructions and performed            | generally on binary or decimal data. F        | ixed-point numbers are used  |

| to represent integers or fracti       | ons. We can have signed or unsigned n         | legative numbers.            |

| Learning objective:                   |                                               |                              |

| To discuss the operation              | on of various components of computing         | g systems                    |

| Prerequisite knowledge for            | Complete understanding and learning           | g of Topic:                  |

| Basic operational conc                | epts                                          |                              |

| Addition and Subtract                 | ion                                           |                              |

| Detailed content of the Lect          | ıre:                                          |                              |

| ADDITION & SUBTRACTI                  | ON OF SIGNED NUMBERS                          |                              |

| • Following are the two               | rules for addition and subtraction of         | n-bit signed numbers         |

| using the 2's complement r            | epresentation system.                         |                              |

| Rule 1:                               |                                               |                              |

| > To Add two num position.            | bers, add their n-bits and ignore the ca      | arry-out signal from the MSB |

| <ul><li>Result will be alge</li></ul> | ebraically correct, if it lies in the range - | $2^{n-1}$ to $+2^{n-1}-1$ .  |

| Rule 2:                               |                                               |                              |

| > To Subtract two                     | numbers X and Y (that is to perfo             | rm X-Y), take the 2's        |

| complement of Y an                    | d then add it to X as in rule 1.              |                              |

> Result will be algebraically correct, if it lies in the range  $(2^{n-1})$  to  $+(2^{n-1}-1)$ .

- The n-bit adder can be used to add 2's complement numbers X and Y.

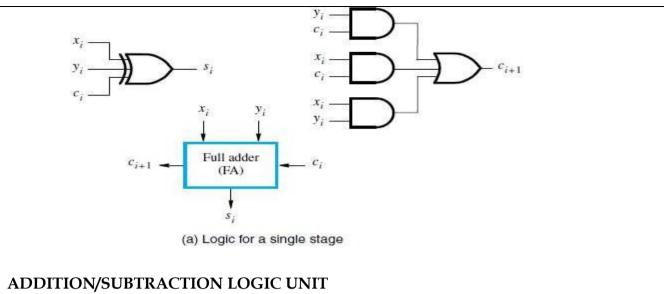

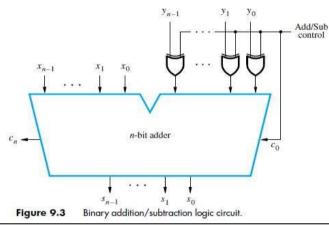

- Overflow can only occur when the signs of the 2 operands are the same. Control-line=0 for addition, applying the Y vector unchanged to one of the adder inputs. Control-line=1 for subtraction, the Y vector is 2's complemented.

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=bQOOsrE11gc&t=67s

https://www.youtube.com/watch?v=o-WXqnagg0c&t=23s

https://www.youtube.com/watch?v=qk1rrfEWyGU

Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By bester field: page no: 368

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 260-264.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

Г

|                                                | LECT                          | <b>FURE HANDOUTS</b>                            | L - 11                     |

|------------------------------------------------|-------------------------------|-------------------------------------------------|----------------------------|

|                                                |                               |                                                 |                            |

| CSE                                            |                               |                                                 | II/III/A                   |

| Course Name with Code                          | : 16CSD12&                    | COMPUTER ARCHITEC                               | TURE                       |

| Course Faculty                                 | : R.Vinupri                   | ya                                              |                            |

| Unit                                           | : II - Arithr                 | netic and Logic Unit                            | Date of Lecture:           |

| Topic of Lecture: DESIG                        | OF FAST ADE                   | DERS                                            |                            |

| Introduction:                                  |                               |                                                 |                            |

| Two approaches can be                          | used to reduce de             | lay in adders:                                  |                            |

| 1. Use the fastest po                          | ssible electronic-t           | echnology in implementing                       | ; the ripple-carry design. |

| 2. Use an augmente                             | d logic-gate netw             | ork structure.                                  |                            |

| Learning objective:                            |                               |                                                 |                            |

| • To discuss the op                            | eration of various            | components of computing                         | systems                    |

| Prerequisite knowledge                         | e for Complete ur             | nderstanding and learning                       | of Topic:                  |

| Basic operational                              | concepts                      |                                                 |                            |

| Addition and Sub                               | otraction                     |                                                 |                            |

| Detailed content of the                        |                               |                                                 |                            |

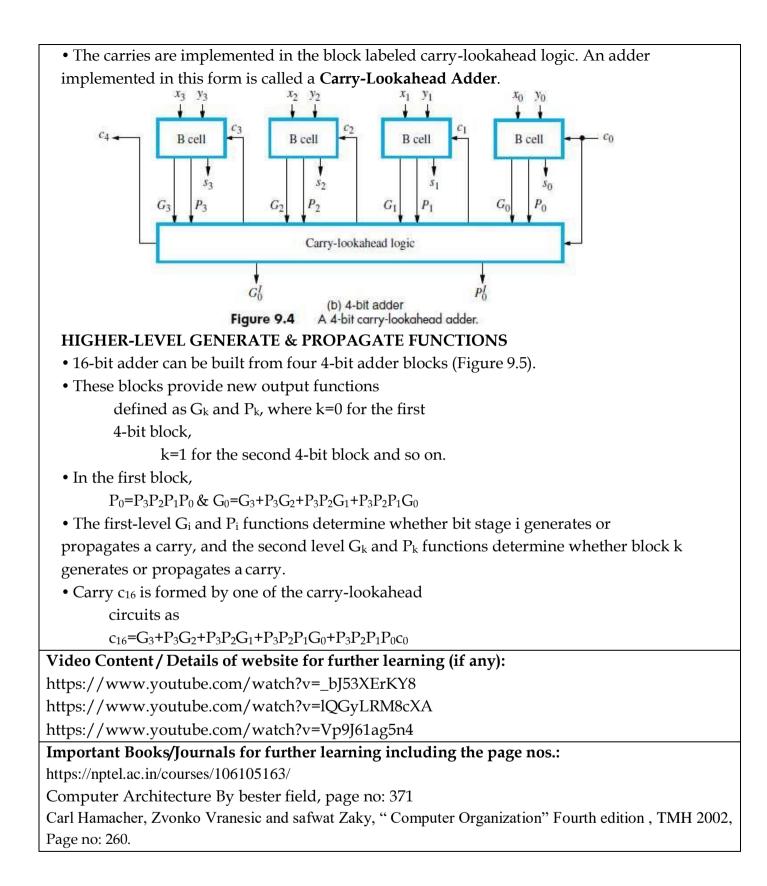

| CARRY-LOOKAHEAD                                | ADDITIONS                     |                                                 |                            |

|                                                |                               | <sub>i+1</sub> (carry-out) of stage i are       |                            |

| $s_i = x_i + y_i + c_i$                        | (1)                           | $c_{i+1} = x_i y_i + x_i c_i + y_i c_i$         | (2)                        |

| • Factoring (2) into                           |                               |                                                 |                            |

|                                                | $x_i + (x_i + y_i)c_i$ we can |                                                 |                            |

|                                                | $P_iC_i$ where $G_i$ =        |                                                 |                            |

| -                                              | e                             | enerate and propagate func                      | ( <b>b</b>                 |

|                                                | -                             | e input carry c <sub>i</sub> . This occurs      | •                          |

|                                                |                               | in input-carry will produce                     | an output-carry            |

| when either $x_i=1$ or y                       |                               | • 1 1 .1 1• 1                                   | 1 1 • 1 • . 1 1            |

|                                                |                               | independently and in paral                      | 0 0 I                      |

|                                                | -                             | variables and substituting in                   |                            |

| 1                                              |                               | $G_{i-1} + P_i P_{i-1} G_{i-2} + P_1 G_0 + P_2$ | $P_{i-1} P_0 C_0$          |

| • Conclusion: Delay th                         |                               |                                                 |                            |

| -                                              | -                             | ys for all sum-bits.                            |                            |

| Consider the design                            |                               | ne carries can be                               |                            |

| implemented as $a = C + R C + R$               |                               |                                                 |                            |

| $c_2 = G_1 + P_1 G_0 + P_1$                    |                               |                                                 |                            |

| $c_3 = G_2 + P_2 G_1 + P_2 T_2$                |                               |                                                 |                            |

| $C_4 - G_3 + \Gamma_3 G_2 + \Gamma_3 \Gamma_3$ | $P_2G_1 + P_3P_2P_1G_0 + P_3$ |                                                 |                            |

$P_2P_1P_0c_0$

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

|                                                          | LECTURI          | E HANDOU             | TS                          | L - 12                                    |

|----------------------------------------------------------|------------------|----------------------|-----------------------------|-------------------------------------------|

| CSE                                                      |                  |                      |                             | II/III/A                                  |

|                                                          |                  |                      |                             |                                           |

| Course Name with Code : 1                                | .6CSD12& CO      | MPUTER A             | RCHITECTUR                  | E                                         |

| Course Faculty : I                                       | R.Vinupriya      |                      |                             |                                           |

| Unit :                                                   | II - Arithmetic  | and Logic U          | nit Date                    | of Lecture:                               |

| Topic of Lecture: MULTIPLICA                             | TION OF POS      | SITIVE NUM           | IBERS                       |                                           |

| Introduction:                                            |                  |                      |                             |                                           |

| The multiplication is a comp                             | lex operation    | than additio         | n and subtraction           | on. It can be performed                   |

| in hardware or software. A wide                          | e variety of alg | orithms hav          | e been used in              | various computers. For                    |

| simplicity we will first see the n                       | nultiplication a | algorithms fo        | or unsigned inte            | egers, and then we will                   |

| see the multiplication algorithm                         | for signed nu    | mbers.               |                             |                                           |

| Learning objective:                                      |                  |                      |                             |                                           |

| • To discuss the operation of                            | of various com   | ponents of c         | computing syste             | ems                                       |

| Prerequisite knowledge for Con                           | mplete unders    | tanding and          | l learning of To            | opic:                                     |

| Basic operational concept                                | S                |                      |                             |                                           |

| Addition and Subtraction                                 | ı                |                      |                             |                                           |

| Detailed content of the Lecture                          | : Detailed con   | tent of the L        | ecture:                     |                                           |

| Multiplication operation steps:                          |                  |                      |                             |                                           |

| Start                                                    |                  | М                    |                             |                                           |

| <b>t</b>                                                 |                  | 1 1 0 1              |                             | Livial Constant                           |

| $M \leftarrow Multiplicand, Q \leftarrow Multiplier$     |                  | 0000                 | 1011                        | <ul> <li>Initial configuration</li> </ul> |

| C, A $\leftarrow$ 0, Count $\leftarrow$ No. of bits of C | 2 C              | A                    | 0                           |                                           |

|                                                          | 0                | 1 1 0 1              | 1 0 1 1                     | Add First cycle                           |

| No Q <sub>0</sub> = 1 Yes A                              | 0                | 0 1 1 0              | 1 1 0 1                     | Shift } First cycle                       |

| $Q_0 = 1$ $A$                                            | ← A + M          | 0011                 | 1 1 0 1                     | Add                                       |

|                                                          | 0                | 1 0 0 1              | 1 1 1 0                     | Shift Second cycle                        |

| Right Shift C, A, Q                                      |                  |                      | $\sim$                      | <b>`</b>                                  |

| Count ← Count - 1                                        | 0                | $1 0 0 1 \\ 0 1 0 0$ | 1 1 1 0<br>$1 1 1 1_{\sim}$ | No add<br>Shift > Third cycle             |

| *                                                        | U                | 0100                 |                             |                                           |

| No Is<br>Count = 0                                       | 1                | 0 0 0 1              | 1111                        | Add Fourth cycle                          |

| ?                                                        | 0                | 1 0 0 0              | 1 1 1 1                     | Shift } Fourth cycle                      |

| Yes                                                      |                  | Pro                  | duct                        |                                           |

| Stop Result in                                           |                  | 4.650                | (b) Multiplication exa      | mple                                      |

| Fig. : Flowchart of Unsigned Binary Multip               | Figur            | e 9.7 Sequent        | ial circuit binary multipl  |                                           |

- Multiplication process involves generation of partial products, one for each digit in the multiplier. These partial products are then summed to produce the final product.

- In the binary system the partial products are easily defined. When the multiplier bit is 0, the partial product is 0, and when the multiplier is 1, the partial product is the multiplicand.

- The final product is produced by summing the partial products. Before summing operation, each successive partial product is shifted one position to left relative to the preceding partial product.

- The product of two n-digit numbers can be accommodated in 2n digits, so the product of the two 4-bit numbers in fits into 8-bits.

### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=B2bKdGf1Qoc

https://www.youtube.com/watch?v=b\_azyJ4ZgVo

https://www.youtube.com/watch?v=XWnm1PyMgaY

# Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By bester field, page no: 376

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 271-273.

**Course Faculty**

Unit

# MUTHAYAMMAL ENGINEERING COLLEGE

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

### **LECTURE HANDOUTS**

L - 13

CSE II/III/A **Course Name with Code** :16CSD12& COMPUTER ARCHITECTURE **Course Faculty** : R.Vinupriya : II - Arithmetic and Logic Unit Date of Lecture: **Topic of Lecture: SIGNED OPERAND MULTIPLICATION** Introduction: A technique which works equally well for both negative and positive multiplier, called Booth Algorithm. There are two techniques for speeding up the multiplication process. In first technique the maximum number of summands are reduced to n/2 for n-bit operands. The second technique, called the carry save addition reduces the time needed to add the summand. Learning objective: To discuss the operation of various components of computing systems Prerequisite knowledge for Complete understanding and learning of Topic: Basic operational concepts Addition and Subtraction Detailed content of the Lecture: BOOTH'S ALGORITHM **Example of Booth's Algorithm** START  $A \leftarrow 0, Q_{-1} \leftarrow 0$ М A 0 Q-1 M ← Multiplicand 0000 0011 0 0111 Initial Values Q ← Multiplier Count  $\leftarrow n$ A A - M First Shift Cycle 1001 0011 0 0111 1100 1001 1 0111 Second } = 10 = 010111 1110 0100 1 Shift Q., Q\_1 Cycle A A + M } Third Shift Cycle 0101 0100 1 0111 = 11 = 00 0010 1010 0 0111  $A \leftarrow A - M$  $A \leftarrow A + M$ Fourth 0001 0101 0 0111 Shift Cycle Arithmetic shift Right: A, Q, Q-1 Count ← Count - 1 No Yes Count = 0?> END

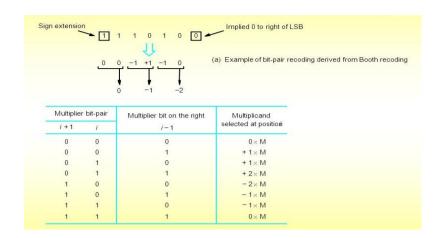

## FAST MULTIPLICATION **BIT-PAIR RECODING OF MULTIPLIERS**

This method

$\rightarrow$  derived from the booth algorithm

- $\rightarrow$  reduces the number of summands by a factor of 2

- Group the Booth-recoded multiplier bits in pairs.

- The pair (+1 -1) is equivalent to the pair (0 +1).

### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=DIp4GqSCZho

https://www.youtube.com/watch?v=cWfaw7b3jKY

https://www.youtube.com/watch?v=gdV-uaPkmxk

## Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By bester field Text Book 1: page no: 380

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 273-277.

**Course Faculty**

Unit

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

### **LECTURE HANDOUTS**

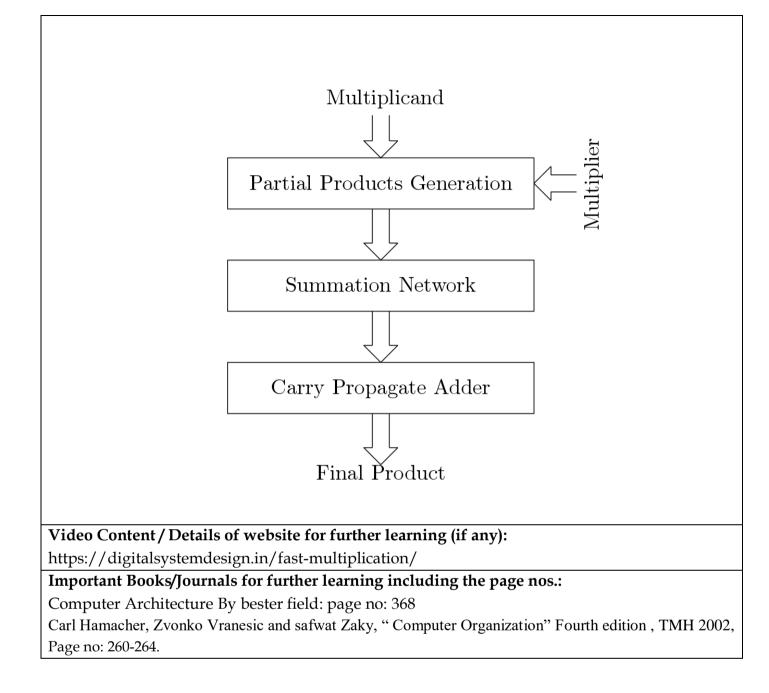

CSE II/III/A **Course Name with Code** :16CSD12& COMPUTER ARCHITECTURE **Course Faculty** : R.Vinupriya : II - Arithmetic and Logic Unit Date of Lecture: Topic of Lecture: Fast Multiplication Introduction: The addition, Subtraction, multiplication and division are the four basic arithmetic instructions and performed generally on binary or decimal data. Fixed-point numbers are used to represent integers or fractions. We can have signed or unsigned negative numbers. Learning objective: To discuss the operation of various components of computing systems Prerequisite knowledge for Complete understanding and learning of Topic: Basic operational concepts

Addition and Subtraction •

Detailed content of the Lecture:

The fast multiplication can be achieved in three general ways.

- 1. The sequential multipliers sequentially generates the partial products and adds them with the previously stored partial products.

- 2. In the second method, high speed parallel multipliers generate the partial products in parallel and adds them by a fast multi-operand adder.

- 3. The third method corresponds to use of array of identical blocks that generates and adds the partial products simultaneously.

- The sequential multipliers have to work at high frequency and thus consumes high power.

- The performance of the parallel multipliers depends on the performance of multi-operand adder and also on the optimal number of partial products.

- The third method is actually the array multiplier having high hardware complexity. An obvious method to design a fast multiplier is to reduce the partial products and then applying fast addition methods.

- Here we will first discuss the methods to reduce the partial products and then fast multioperand addition techniques will be discussed.

- All the steps are described below in details

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

| II/III/A |

|----------|

L - 15

| CSE                   |                           |           |                |                        |                        | II/III/A              |

|-----------------------|---------------------------|-----------|----------------|------------------------|------------------------|-----------------------|

| Course Name           | with Code                 | : 16CSD   | 012& COMP      | UTER ARCHI             | FECTURE                |                       |

| <b>Course Faculty</b> | r                         | : R.Vin   | upriya         |                        |                        |                       |

| Unit                  |                           | : II - A  | rithmetic and  | l Logic Unit           | Date of I              | Lecture:              |

| Topic of Lect         | ure: INTEGER D            | IVISIO    | N              |                        |                        |                       |

| Introduction:         | -                         |           |                |                        |                        |                       |

| The divi              | sion is more con          | mplex †   | than multip    | lication. A <b>div</b> | i <b>sion</b> algorith | m is an algorithm     |

| which, given          | two <b>integers</b> N     | and D,    | computes       | heir quotient a        | and/or remai           | inder, the result of  |

| Euclidean <b>div</b>  | v <b>ision</b> . Some are | e applie  | ed by hand,    | while others           | are employed           | d by digital circuit  |

| designs and s         | oftware.                  |           |                |                        |                        |                       |

| Learning obj          | ective:                   |           |                |                        |                        |                       |

|                       | cuss the operation        |           | 1              | 1                      | 0,                     |                       |

| Prerequisite          | knowledge for C           | Complet   | te understan   | ding and learn         | ing of Topic:          | :                     |

| Basic o               | perational conce          | pts       |                |                        |                        |                       |

| Additi                | on and Subtraction        | on        |                |                        |                        |                       |

| -                     | lication                  |           |                |                        |                        |                       |

|                       | tent of the Lectu         | re: Deta  | ailed conten   | t of the Lecture       | :                      |                       |

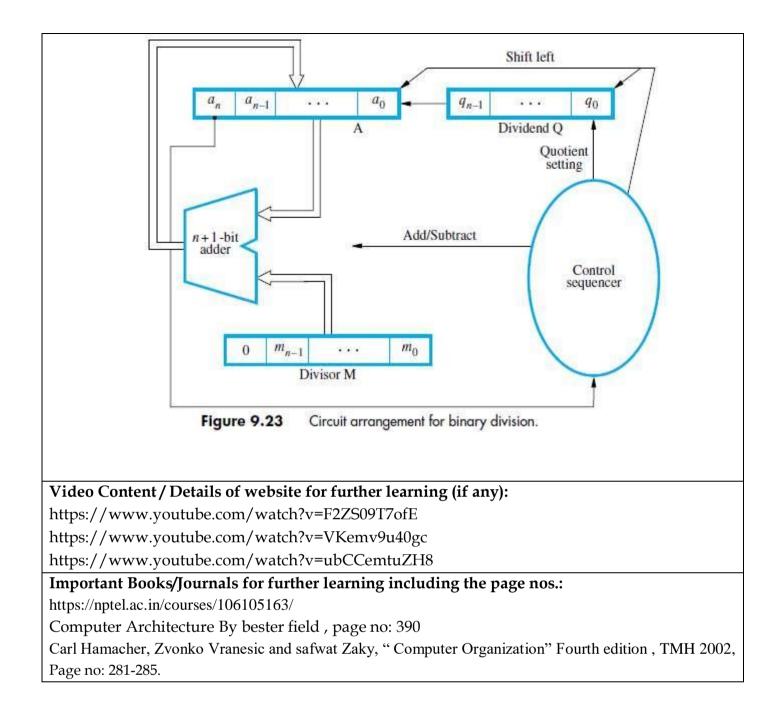

| INTEGER               |                           |           |                |                        |                        |                       |

| _                     | positive-divisor is       |           | -              |                        |                        |                       |

| -                     | positive-dividend         | l is load | led into regis | ster Q at the sta      | rt of the oper         | ation.                |

| • Register A          |                           |           |                |                        | 1.1 1                  | 1 • • •               |

| • After divi          | sion operation, th        | he n-bit  | quotient is i  | n register Q, ar       | nd the remain          | der is in register A. |

|                       |                           |           |                |                        |                        |                       |

|                       | 21                        | -         |                | 10101                  |                        |                       |

|                       | 13)274<br>26              |           | 1101           | ) 100010010<br>1101    |                        |                       |

|                       |                           |           |                | 10000                  |                        |                       |

|                       | 13                        |           |                | 1101                   |                        |                       |

|                       | 1                         | 18        |                | 1110                   |                        |                       |

|                       |                           |           |                | 1101                   |                        |                       |

|                       | Figure                    | 0 22      | longhand       | l<br>division example: |                        |                       |

|                       | rigore                    | 7.22      | Longhana       | avision example:       |                        |                       |

|                       |                           |           |                |                        |                        |                       |

**Course Faculty**

\_n-1?

STOP

Yes 🟹

Quotient in Q

$\texttt{COUNT} \ \leftarrow \texttt{COUNT+1}$

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

| L | - | 16 |  |

|---|---|----|--|

|   |   |    |  |

| CSE                                        |                            |                            |                        | II/III/A           |

|--------------------------------------------|----------------------------|----------------------------|------------------------|--------------------|

| Course Name with Code                      | : 16CSD12& COM             | IPUTER ARCHITI             | ECTURE                 |                    |

| Course Faculty                             | : R.Vinupriya              |                            |                        |                    |

| Unit                                       | : II - Arithmetic a        | and Logic Unit             | Date of I              | Lecture:           |

| Topic of Lecture: INTEGE                   | ER DIVISION                |                            |                        |                    |

| Introduction:                              |                            |                            |                        |                    |

| A division algorithm                       | provides a quotient        | and a remainder            | when we d              | ivide two number.  |

| They are generally of tw                   | vo type slow algorit       | hm and fast algor          | ithm. Slow             | division algorithm |

| is restoring, non-restoring                | , non-performing rest      | oring, SRT algor           | ithm and               | under fast comes   |

| Newton-Raphson and Go                      | ldschmidt.                 |                            |                        |                    |

| Learning objective:                        |                            |                            |                        |                    |

| • To discuss the oper                      | ation of various comp      | oonents of computi         | ng systems             |                    |

| Prerequisite knowledge f                   | or Complete underst        | anding and learning        | ng of Topic            |                    |

| Basic operational co                       | oncepts                    |                            |                        |                    |

| Addition and Subtr                         | action                     |                            |                        |                    |

| Multiplication                             |                            |                            |                        |                    |

| Detailed content of the Lo                 | ecture: Detailed conte     | ent of the Lecture:        |                        |                    |

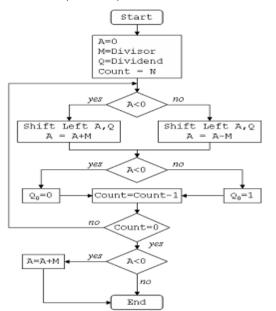

| <b>RESTORING DIVISION</b>                  |                            |                            |                        |                    |

| Procedure: Do the following                | ng n times                 |                            |                        |                    |

| 1. Shift A and Q left o                    | ne binary position.        |                            |                        |                    |

| 2. Subtract M from A,                      | and place the answer       | r back in A.               |                        |                    |

| 3. If the sign of A is 1,                  | , set $q_0$ to 0 and add M | I back to A (restore       | A).                    |                    |

| 4. If the sign of A is 0,                  | set $q_0$ to 1 and no res  | toring done.               |                        |                    |

|                                            | A-Accumulator              |                            |                        |                    |

|                                            | M-Divisor                  |                            | 000 10<br>011          | 0 0                |

| Q ← dividend<br>COUNT← 0                   | Q-Dividend/Quotient        |                            | 001 00<br>101          | 0  First cycle     |

| ₩<br>M ← divisor                           |                            | Set $q_0$ 1 1<br>Restore   | 1 1 0<br>1 1           |                    |

| $\square \rightarrow A \leftarrow \square$ |                            |                            | 0 0 1 0 0<br>0 1 0 0 0 |                    |

| Left-shift A, Q<br>↓                       |                            |                            | <u>1 0 1</u><br>1 1 1  | > Second cycle     |

| $A \leftarrow A-M$                         |                            | Restore 0 0                |                        |                    |

| A < 0? Yes                                 |                            |                            | 1 0 0 0 0<br>1 0 1     | Manafarita da      |

| No V                                       | $Q(0) \leftarrow 0$        |                            | 0 0 1                  | > Third cycle      |

| Q(0) ← 1                                   | A ← A+M                    |                            | 0 1 0 0 0<br>1 0 1 0 0 |                    |

| COUNT= No                                  |                            | Set $q_0$ (1) 1<br>Restore | 1 1 1                  | > Fourth cycle     |

0 0 0 1 0

Remainder

Figure 9.24

0010

Quotient

A restoring division example.

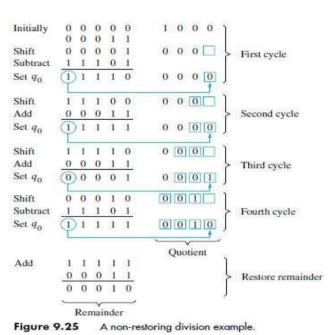

#### NON-RESTORING DIVISION

Procedure: Do the following n times

- If the sign of A is 0, shift A and Q left one-bit position and subtract M from A; otherwise, shift A and Q left and add M to A.

- 2. Now, if the sign of A is 0, set  $q_0$  to 1; otherwise set  $q_0$  to 0.

- 3. If the sign of A is 1, add M to A (restore).

#### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=6ToR6vuRb3M

https://www.youtube.com/watch?v=zVestoCRRbM

https://www.youtube.com/watch?v=KoWT05pfd4k

#### Important Books/Journals for further learning including the page nos.:

https://nptel.ac.in/courses/106105163/

Computer Architecture By Bester field ,page no: 390

Carl Hamacher, Zvonko Vranesic and safwat Zaky, "Computer Organization" Fourth edition, TMH 2002, Page no: 281-285.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

| L | - | 17 |  |

|---|---|----|--|

|   |   |    |  |

II/III/A

| Course Name with Code                                                                                                   | : 16CSD12& COMPUTER ARCHITE                         | CTURE                           |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------|--|--|--|

| Course Faculty                                                                                                          | : R.Vinupriya                                       |                                 |  |  |  |

| Unit                                                                                                                    | : II - Arithmetic and Logic Unit                    | Date of Lecture:                |  |  |  |

| Topic of Lecture: FLOATING                                                                                              | G POINT NUMBERS AND OPERATIC                        | DNS                             |  |  |  |

| Introduction:                                                                                                           |                                                     |                                 |  |  |  |

| 2 parts                                                                                                                 |                                                     |                                 |  |  |  |

| • Mantissa = signed fixe                                                                                                | d point number                                      |                                 |  |  |  |

| • Exponent = the position                                                                                               | n of the decimal point                              |                                 |  |  |  |

| Learning objective:                                                                                                     |                                                     |                                 |  |  |  |

| To discuss the operation                                                                                                | on of various components of computin                | ng systems                      |  |  |  |

| Prerequisite knowledge for                                                                                              | Complete understanding and learnin                  | g of Topic:                     |  |  |  |

| Basic operational conc                                                                                                  | epts                                                |                                 |  |  |  |

| Addition and Subtract                                                                                                   | ion                                                 |                                 |  |  |  |

| Multiplication                                                                                                          |                                                     |                                 |  |  |  |

| Detailed content of the Lectu                                                                                           | ıre:                                                |                                 |  |  |  |

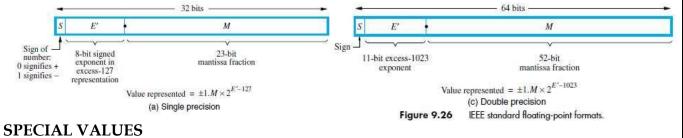

| IEEE STANDARD FOR FI                                                                                                    | LOATING POINT NUMBERS                               |                                 |  |  |  |

| Single precision represent                                                                                              | ation occupies a single 32-bit word.                |                                 |  |  |  |

| The scale factor has                                                                                                    | a range of $2^{-126}$ to $2^{+127}$ (which is appro | ximately equal to $10^{+38}$ ). |  |  |  |

| • The 32-bit word is divided into 3 fields: sign (1 bit), exponent (8 bits) and mantissa (23 bits).                     |                                                     |                                 |  |  |  |

| • Signed exponent=E.                                                                                                    |                                                     |                                 |  |  |  |

| Unsigned exponent E'=E+127. Thus, E' is in the range 0 <e'<255.< td=""></e'<255.<>                                      |                                                     |                                 |  |  |  |

| • The last 23 bits represent the mantissa. Since binary normalization is used, the MSB of                               |                                                     |                                 |  |  |  |

| the mantissa is always equal to 1. (M represents fractional-part).                                                      |                                                     |                                 |  |  |  |

| • The 24-bit mantissa provides a precision equivalent to about 7 decimal-digits (Figure 9.24).                          |                                                     |                                 |  |  |  |

| • Double precision representation occupies a single 64-bit word. And E' is in the range 1 <e'<2046.< td=""></e'<2046.<> |                                                     |                                 |  |  |  |

| • The 53-bit mantissa provi                                                                                             | des a precision equivalent to about 16              | decimal-digits.                 |  |  |  |

|                                                                                                                         |                                                     |                                 |  |  |  |