# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L 01

II / III

Course Name with Code: 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : I- BOOLEAN ALGEBRA AND LOGIC GATES

Date of Lecture:

Topic of Lecture: Review of Number systems, Number Representation

#### Introduction :

Number systems use different number bases. A number base indicates how many different digits are available when using a particular numbering system.

Prerequisite knowledge for Complete understanding and learning of Topic:

A basic idea regarding the initial concepts of Digital Electronics is enough to understand the topics covered.

If base or radix of a number system is 'r', then the numbers present in that number system are ranging from zero to r-1. The total numbers present in that number system is 'r'. So, we will get various number systems, by choosing the values of radix as greater than or equal to two.

In this chapter, let us discuss about the popular number systems and how to represent a number in the respective number system. The following number systems are the most commonly used.

- Decimal Number system

- Binary Number system

- Octal Number system

- Hexadecimal Number system

## Decimal Number System

The base or radix of Decimal number system is 10. So, the numbers ranging from 0 to 9 are used in this number system.

In this number system, the successive positions to the left of the decimal point having weights of 100, 101, 102, 103 and so on. Similarly, the successive positions to the right of the decimal

point having weights of 10-1, 10-2, 10-3 and so on. That means, each position has specific weight, which is power of base 10

## Example

Consider the decimal number 1358.246. Integer part of this number is 1358 and fractional part of this number is 0.246. The digits 8, 5, 3 and 1 have weights of 100, 101, 102 and 103 respectively. Similarly, the digits 2, 4 and 6 have weights of 10-1, 10-2 and 10-3 respectively.

Mathematically, we can write it as

$1358.246 = (1 \times 103) + (3 \times 102) + (5 \times 101) + (8 \times 100) + (2 \times 10-1) +$

$(4 \times 10-2) + (6 \times 10-3)$

After simplifying the right hand side terms, we will get the decimal number, which is on left hand side.

## Binary Number System

All digital circuits and systems use this binary number system. The base or radix of this number system is 2. So, the numbers 0 and 1 are used in this number system.

The part of the number, which lies to the left of the binary point is known as integer part. Similarly, the part of the number, which lies to the right of the binary point is known as fractional part.

In this number system, the successive positions to the left of the binary point having weights of 20, 21, 22, 23 and so on. Similarly, the successive positions to the right of the binary point having weights of 2-1, 2-2, 2-3 and so on. That means, each position has specific weight, which is power of base 2.

## Example

Consider the binary number 1101.011. Integer part of this number is 1101 and fractional part of this number is 0.011. The digits 1, 0, 1 and 1 of integer part have weights of 20, 21, 22, 23 respectively. Similarly, the digits 0, 1 and 1 of fractional part have weights of 2-1, 2-2, 2-3 respectively.

Mathematically, we can write it as

$1101.011 = (1 \times 23) + (1 \times 22) + (0 \times 21) + (1 \times 20) + (0 \times 2-1) +$

$$(1 \times 2-2) + (1 \times 2-3)$$

After simplifying the right hand side terms, we will get a decimal number, which is an equivalent of binary number on left hand side.

## Octal Number System

The base or radix of octal number system is 8. So, the numbers ranging from 0 to 7 are used in this number system.

In this number system, the successive positions to the left of the octal point having weights of 80, 81, 82, 83 and so on. Similarly, the successive positions to the right of the octal point having weights of 8-1, 8-2, 8-3 and so on. That means, each position has specific weight, which is power of base 8.

#### Example

Consider the octal number 1457.236. Integer part of this number is 1457 and fractional part of this number is 0.236. The digits 7, 5, 4 and 1 have weights of 80, 81, 82 and 83 respectively. Similarly, the digits 2, 3 and 6 have weights of 8-1, 8-2, 8-3 respectively.

Mathematically, we can write it as

$1457.236 = (1 \times 83) + (4 \times 82) + (5 \times 81) + (7 \times 80) + (2 \times 8-1) +$

$(3 \times 8-2) + (6 \times 8-3)$

After simplifying the right hand side terms, we will get a decimal number, which is an equivalent of octal number on left hand side.

### Hexadecimal Number System

The base or radix of Hexa-decimal number system is 16. So, the numbers ranging from 0 to 9 and the letters from A to F are used in this number system. The decimal equivalent of Hexa-decimal digits from A to F are 10 to 15.

The part of the number, which lies to the left of the hexadecimal point is known as integer part. Similarly, the part of the number, which lies to the right of the Hexa-decimal point is known as fractional part.

In this number system, the successive positions to the left of the Hexa-decimal point having weights of 160, 161, 162, 163 and so on. Similarly, the successive positions to the right of the Hexa-decimal point having weights of 16-1, 16-2, 16-3 and so on. That means, each position has specific weight, which is power of base 16.

## Example

$1A05.2C4 = (1 \times 163) + (10 \times 162) + (0 \times 161) + (5 \times 160) + (2 \times 16-1) + (10 \times 162) + (10 \times 16$

$(12 \times 16-2) + (4 \times 16-3)$

After simplifying the right hand side terms, we will get a decimal number, which is an equivalent of Hexa-decimal number on left hand side.

Video Content / Details of website for further learning (if any): https://www.khanacademy.org/math/algebra-home/alg-intro-to-algebra/algebra-alternate-numberbases/v/number-systems-introduction https://www.youtube.com/watch?v=L2zsmYaI5ww

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition,2013. Page No (1)

**Course Teacher**

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

CS

II / III

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : I- BOOLEAN ALGEBRA AND LOGIC GATES

**Date of Lecture:**

Topic of Lecture: Boolean algebra, Boolean postulates and laws

**Introduction :** Boolean Algebra is an algebra, which deals with binary numbers & binary variables. Hence, it is also called as Binary Algebra or logical Algebra. A mathematician, named George Boole had developed this algebra in 1854. The variables used in this algebra are also called as Boolean variables.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Decimal Number system

- Binary Number system

- Octal Number system

- Hexadecimal Number system

The range of voltages corresponding to Logic 'High' is represented with '1' and the range of voltages corresponding to logic 'Low' is represented with '0'.

#### Postulates and Basic Laws of Boolean Algebra

In this section, let us discuss about the Boolean postulates and basic laws that are used in Boolean algebra. These are useful in minimizing Boolean functions.

#### **Boolean Postulates**

Consider the binary numbers 0 and 1, Boolean variable xx and its complement x'x'. Either the Boolean variable or complement of it is known as literal. The four possible logical OR operations among these literals and binary numbers are shown below.

x + 0 = x x + 1 = 1 x + x = x x + x' = 1

### **Basic Laws of Boolean Algebra**

Following are the three basic laws of Boolean Algebra.

- Commutative law

- Associative law

• Distributive law

#### **Commutative Law**

If any logical operation of two Boolean variables give the same result irrespective of the order of those two variables, then that logical operation is said to be Commutative. The logical OR & logical AND operations of two Boolean variables x & y are shown below

$$x + y = y + x$$

$$x \cdot y = y \cdot x$$

The symbol '+' indicates logical OR operation. Similarly, the symbol '.' indicates logical AND operation and it is optional to represent. Commutative law obeys for logical OR & logical AND operations.

#### Associative Law

The logical OR & logical AND operations of three Boolean variables x, y & z are shown below.

$\begin{array}{l} x+y+zy+z=x+yx+y+z\\ x.y.zy.z=x.yx.y.z\end{array}$

Associative law obeys for logical OR & logical AND operations.

#### **Distributive Law**

If any logical operation can be distributed to all the terms present in the Boolean function, then that logical operation is said to be Distributive. The distribution of logical OR & logical AND operations of three Boolean variables x, y & z are shown below.

$$\begin{array}{l} x.y+zy+z = x.y+x.z \\ x+y.zy.z = x+yx+y.x+zx+z \end{array}$$

Distributive law obeys for logical OR and logical AND operations.

These are the Basic laws of Boolean algebra. We can verify these laws easily, by substituting the Boolean variables with '0' or '1'.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=gj8QmRQtVao https://www.youtube.com/watch?v=2U71nZYb990

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition,2013. Page No (38)

**Course Teacher**

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L 03

II / III

Course Name with Code: 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : I- BOOLEAN ALGEBRA AND LOGIC GATES

Date of Lecture:

Topic of Lecture: De-Morgan's Theorem - Principle of Duality

#### Introduction :

One part may be obtained from the other if the binary operators and the identity elements are interchanged. This important property of Boolean algebra is called the duality principle.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Decimal Number system

- Binary Number system

- Octal Number system

- Hexadecimal Number system

- Boolean algebra

- Boolean postulates and laws

Theorems of Boolean Algebra

The following two theorems are used in Boolean algebra.

- Duality theorem

- DeMorgan's theorem

#### Duality Theorem

This theorem states that the dual of the Boolean function is obtained by interchanging the logical AND operator with logical OR operator and zeros with ones. For every Boolean function, there will be a corresponding Dual function.

Let us make the Boolean equations relations that we discussed in the section of Boolean postulates and basic laws into two groups. The following table shows these two groups.

| Group1                                              | Group2                     |  |

|-----------------------------------------------------|----------------------------|--|

| $\mathbf{x} + 0 = \mathbf{x}$                       | x.1 = x                    |  |

| x + 1 = 1                                           | x.0 = 0                    |  |

| $\mathbf{x} + \mathbf{x} = \mathbf{x}$              | x.x = x                    |  |

| x + x' = 1                                          | x.x' = 0                   |  |

| $\mathbf{x} + \mathbf{y} = \mathbf{y} + \mathbf{x}$ | x.y = y.x                  |  |

| x + y + zy + z = x + yx + y + z                     | x.y.zy.z = x.yx.y.z        |  |

| x.y+zy+z = x.y + x.z                                | x + y.zy.z = x+yx+y.x+zx+z |  |

|                                                     |                            |  |

In each row, there are two Boolean equations and they are dual to each other. We can verify all these Boolean equations of Group1 and Group2 by using duality theorem.

DeMorgan's Theorem

This theorem is useful in finding the complement of Boolean function. It states that the complement of logical OR of at least two Boolean variables is equal to the logical AND of each complemented variable.

DeMorgan's theorem with 2 Boolean variables x and y can be represented as

x+yx+y' = x'.y'

The dual of the above Boolean function is

$$x.yx.y' = x' + y'$$

Therefore, the complement of logical AND of two Boolean variables is equal to the logical OR of each complemented variable. Similarly, we can apply DeMorgan's theorem for more than 2 Boolean variables also.

Simplification of Boolean Functions

Till now, we discussed the postulates, basic laws and theorems of Boolean algebra. Now, let us simplify some Boolean functions.

Example 1

Let us simplify the Boolean function, f = p'qr + pq'r + pqr' + pqr

We can simplify this function in two methods.

Method 1

Given Boolean function, f = p'qr + pq'r + pqr' + pqr.

Step 1 – In first and second terms r is common and in third and fourth terms pq is common. So, take the common terms by using Distributive law.

$\Rightarrow$  f = p'q+pq'p'q+pq'r + pqr'+rr'+r

Step 2 – The terms present in first parenthesis can be simplified to Ex-OR operation. The terms present in second parenthesis can be simplified to '1' using Boolean postulate

Method 2

Given Boolean function, f = p'qr + pq'r + pqr' + pqr.

Step 1 – Use the Boolean postulate, x + x = x. That means, the Logical OR operation with any Boolean variable 'n' times will be equal to the same variable. So, we can write the last term pqr two more times.

$$\Rightarrow$$

f = p'qr + pq'r + pqr' + pqr + pqr + pqr

Step 2 – Use Distributive law for 1st and 4th terms, 2nd and 5th terms, 3rd and 6th terms.

$\Rightarrow$  f = qrp'+pp'+p + prq'+qq'+q + pqr'+rr'+r

Step 3 – Use Boolean postulate, x + x' = 1 for simplifying the terms present in each parenthesis.

$$\Rightarrow$$

f = qr11 + pr11 + pq11

Step 4 – Use Boolean postulate, x.1 = x for simplifying the above three terms.

$$\Rightarrow f = qr + pr + pq$$

$$\Rightarrow f = pq + qr + pr$$

Therefore, the simplified Boolean function is f = pq + qr + pr.

So, we got two different Boolean functions after simplifying the given Boolean function in each method. Functionally, those two Boolean functions are same. So, based on the requirement, we can choose one of those two Boolean functions.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=yi6oxF8kgXk https://www.youtube.com/watch?v=20bEwa8W4sQ

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (46)

**Course Teacher**

## MUTHAYAMMAL ENGINEERING COLLEGE

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

| Q | AC |

|---|----|

| a |    |

|   |    |

II / III

L 04

| Course Name with Code | : 19GES24/Digital Principles and System Design |                  |

|-----------------------|------------------------------------------------|------------------|

| Course Teacher        | : Ms.S.Priya, AP/ECE                           |                  |

| Unit                  | : I- BOOLEAN ALGEBRA AND LOGIC GATES           | Date of Lecture: |

|                       |                                                | Date of Lettine. |

**Topic of Lecture:** Simplification using Boolean algebra **Introduction :** Boolean algebra is an algebraic structure defined by a set of elements, B, together with two binary operators, + and #, provided that the following (Huntington) postulates are satisfied. **Prerequisite knowledge for Complete understanding and learning of Topic: Binary** operators Basic laws and theorems of Boolean algebra are discussed. Now, let us simplify some Boolean functions. **Example 1** Let us simplify the Boolean function, f = p'qr + pq'r + pqr' + pqrWe can simplify this function in two methods. Method 1 Given Boolean function, f = p'qr + pq'r + pqr' + pqr. Step 1 - In first and second terms r is common and in third and fourth terms pq is common. So, take the common terms by using Distributive law.  $\Rightarrow$  f = p'q+pq'p'q+pq'r + pqr'+rr'+r Step 2 – The terms present in first parenthesis can be simplified to Ex-OR operation. The terms present in second parenthesis can be simplified to '1' using Boolean postulate  $\Rightarrow$  f = p $\oplus$ qp $\oplus$ qr + pq11 Step 3 – The first term can't be simplified further. But, the second term can be simplified to pq using Boolean postulate.  $\Rightarrow$  f = p $\oplus$ qp $\oplus$ qr + pq Therefore, the simplified Boolean function is  $f = p \bigoplus qp \bigoplus qr + pq$ Method 2 Given Boolean function, f = p'qr + pq'r + pqr' + pqr. Step 1 – Use the Boolean postulate, x + x = x. That means, the Logical OR operation with any Boolean variable 'n' times will be equal to the same variable. So, we can write the last term pgr two more times.  $\Rightarrow$  f = p'qr + pq'r + pqr' + pqr + pqr + pqr Step 2 – Use Distributive law for 1st and 4th terms, 2nd and 5th terms, 3rd and 6th terms.  $\Rightarrow$  f = qrp'+pp'+p + prq'+qq'+q + pqr'+rr'+r Step 3 – Use Boolean postulate, x + x' = 1 for simplifying the terms present in each parenthesis.  $\Rightarrow$  f = qr11 + pr11 + pq11

Step 4 – Use Boolean postulate, x.1 = x for simplifying the above three terms.  $\Rightarrow$  f = qr + pr + pq  $\Rightarrow$  f = pq + qr + pr Therefore, the simplified Boolean function is f = pq + qr + pr. So, we got two different Boolean functions after simplifying the given Boolean function in each method. Functionally, those two Boolean functions are same. So, based on the requirement, we can choose one of those two Boolean functions. Example 2 Let us find the complement of the Boolean function, f = p'q + pq'. The complement of Boolean function is f' = p'q+pq'p'q+pq''. Step 1 – Use DeMorgan's theorem, x+yx+y' = x'.y'.  $\Rightarrow$  f' = p'qp'q'.pq'pq'' Step 2 – Use DeMorgan's theorem, x.yx.y' = x' + y' $\Rightarrow$  f' = {p'p'' + q'}.{p' + q'q''} Step3 – Use the Boolean postulate, x'x''=x.  $\Rightarrow$  f' = {p + q'}.{p' + q}  $\Rightarrow$  f' = pp' + pq + p'q' + qq' Step 4 – Use the Boolean postulate, xx'=0.  $\Rightarrow$  f = 0 + pq + p'q' + 0  $\Rightarrow$  f = pq + p'q' Therefore, the complement of Boolean function, p'q + pq' is pq + p'q'. Video Content / Details of website for further learning (if any): https://www.voutube.com/watch?v=0as464WmfCo https://www.youtube.com/watch?v=59BbncMiL8I Important Books/Journals for further learning including the page nos.: Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (43)

**Course Teacher**

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L 05

II / III

Course Name with Code: 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : I- BOOLEAN ALGEBRA AND LOGIC GATES

Date of Lecture:

Topic of Lecture: Canonical forms Sum of product and Product of sum

#### Introduction :

A truth table consists of a set of inputs and outputs. If there are 'n' input variables, then there will be 2n possible combinations with zeros and ones. So the value of each output variable depends on the combination of input variables. So, each output variable will have '1' for some combination of input variables and '0' for some other combination of input variables.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical SoP form

- Canonical PoS form

#### **Canonical SoP form**

Canonical SoP form means Canonical Sum of Products form. In this form, each product term contains all literals. So, these product terms are nothing but the min terms. Hence, canonical SoP form is also called as sum of min terms form.

First, identify the min terms for which, the output variable is one and then do the logical OR of those min terms in order to get the Boolean expression function corresponding to that output variable. This Boolean function will be in the form of sum of min terms.

Follow the same procedure for other output variables also, if there is more than one output variable.

Consider the following truth table.

| Inputs |   | Output |   |  |  |

|--------|---|--------|---|--|--|

| р      | q | r      | f |  |  |

| 0      | 0 | 0      | 0 |  |  |

| 0      | 0 | 1      | 0 |  |  |

| 0      | 1 | 0      | 0 |  |  |

| 0      | 1 | 1      | 1 |  |  |

| 1      | 0 | 0      | 0 |  |  |

| 1      | 0 | 1      | 1 |  |  |

| 1      | 1 | 0      | 1 |  |  |

| 1      | 1 | 1      | 1 |  |  |

#### **Canonical PoS form**

Canonical PoS form means Canonical Product of Sums form. In this form, each sum term contains all literals. So, these sum terms are nothing but the Max terms. Hence, canonical PoS form is also called as product of Max terms form.

First, identify the Max terms for which, the output variable is zero and then do the logical AND of those Max terms in order to get the Boolean expression function corresponding to that output variable. This Boolean function will be in the form of product of Max terms.

#### Standard SoP and PoS forms

We discussed two canonical forms of representing the Boolean outputss. Similarly, there are two standard forms of representing the Boolean outputss. These are the simplified version of canonical forms.

- Standard SoP form

- Standard PoS form

#### Standard SoP form

Standard SoP form means Standard Sum of Products form. In this form, each product term need not contain all literals. So, the product terms may or may not be the min terms. Therefore, the Standard SoP form is the simplified form of canonical SoP form.

We will get Standard SoP form of output variable in two steps.

- Get the canonical SoP form of output variable

- Simplify the above Boolean function, which is in canonical SoP form.

### Standard PoS form

Standard PoS form means Standard Product of Sums form. In this form, each sum term need not contain all literals. So, the sum terms may or may not be the Max terms. Therefore, the Standard PoS form is the simplified form of canonical PoS form.

We will get Standard PoS form of output variable in two steps.

- Get the canonical PoS form of output variable

- Simplify the above Boolean function, which is in canonical PoS form.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=iiIBvuv1QU4 https://www.youtube.com/watch?v=OaLUco7KL1Q https://www.youtube.com/watch?v=Dv0KZ6E3tc4

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (51)

**Course Teacher**

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L 06

II / III

Course Name with Code: 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : I - BOOLEAN ALGEBRA AND LOGIC GATES

Date of Lecture:

Topic of Lecture: Minimization using Karnaugh map

#### Introduction :

The procedure of minimization is awkward because it lacks specific rules to predict each succeeding step in the manipulative process. The map method presented here provides a simple, straightforward procedure for minimizing Boolean functions. This method may be regarded as a pictorial al form of a truth table. The map method is also known as the Karnaugh map or K-map.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

K-Maps for 2 to 5 Variables

K-Map method is most suitable for minimizing Boolean functions of 2 variables to 5 variables. Now, let us discuss about the K-Maps for 2 to 5 variables one by one.

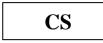

2 Variable K-Map

The number of cells in 2 variable K-map is four, since the number of variables is two. The following figure shows 2 variable K-Map.

- There is only one possibility of grouping 4 adjacent min terms.

- The possible combinations of grouping 2 adjacent min terms are {(m0, m1), (m2, m3), (m0, m2) and (m1, m3)}.

3 Variable K-Map

The number of cells in 3 variable K-map is eight, since the number of variables is three. The following figure shows 3 variable K-Map.

| X | <u> </u>       | 01             | 11             | 10             |

|---|----------------|----------------|----------------|----------------|

| 0 | mo             | m <sub>1</sub> | m <sub>3</sub> | m2             |

| 1 | m <sub>4</sub> | m5             | m7             | m <sub>6</sub> |

- There is only one possibility of grouping 8 adjacent min terms.

- The possible combinations of grouping 4 adjacent min terms are {(m0, m1, m3, m2), (m4, m5, m7, m6), (m0, m1, m4, m5), (m1, m3, m5, m7), (m3, m2, m7, m6) and (m2, m0, m6, m4)}.

- The possible combinations of grouping 2 adjacent min terms are {(m0, m1), (m1, m3), (m3, m2), (m2, m0), (m4, m5), (m5, m7), (m7, m6), (m6, m4), (m0, m4), (m1, m5), (m3, m7) and (m2, m6)}.

- If x=0, then 3 variable K-map becomes 2 variable K-map.

#### 4 Variable K-Map

• The number of cells in 4 variable K-map is sixteen, since the number of variables is four. The following figure shows 4 variable K-Map.

| wx YZ | 00              | 01              | 11              | 10              |

|-------|-----------------|-----------------|-----------------|-----------------|

| 00    | mo              | m <sub>1</sub>  | m <sub>3</sub>  | $m_2$           |

| 01    | m4              | m <sub>5</sub>  | m7              | m <sub>6</sub>  |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| 10    | m <sub>8</sub>  | m9              | m <sub>11</sub> | m <sub>10</sub> |

- There is only one possibility of grouping 16 adjacent min terms.

- Let R1, R2, R3 and R4 represents the min terms of first row, second row, third row and fourth row respectively. Similarly, C1, C2, C3 and C4 represents the min terms of first column, second column, third column and fourth column respectively. The possible combinations of grouping 8 adjacent min terms are {(R1, R2), (R2, R3), (R3, R4), (R4, R1), (C1, C2), (C2, C3), (C3, C4), (C4, C1)}.

- If w=0, then 4 variable K-map becomes 3 variable K-map.

Video Content / Details of website for further learning (if any): <u>https://www.youtube.com/watch?v=wjM2RDG5yTI</u> <u>https://www.youtube.com/watch?v=CpsJoAwreqo</u>

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (73)

**Course Teacher**

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L 07

Course Name with Code: 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

### Unit : I- BOOLEAN ALGEBRA AND LOGIC GATES

Date of Lecture:

**Topic of Lecture:** Minimization using Karnaugh map

#### **Introduction :**

The procedure of minimization is awkward because it lacks specific rules to predict each succeeding step in the manipulative process. The map method presented here provides a simple, straightforward procedure for minimizing Boolean functions. This method may be regarded as a pictorial al form of a truth table. The map method is also known as the Karnaugh map or K-map.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

Minimization of Boolean Functions using K-Maps

Follow these rules for simplifying K-maps in order to get standard sum of products form.

- Select the respective K-map based on the number of variables present in the Boolean function.

- If the Boolean function is given as sum of min terms form, then place the ones at respective min term cells in the K-map.

- Check for the possibilities of grouping maximum number of adjacent ones. It should be powers of two.

- Each grouping will give either a literal or one product term. It is known as prime implicant. The prime implicant is said to be essential prime implicant, if atleast single '1' is not covered with any other groupings but only that grouping covers.

- Note down all the prime implicants and essential prime implicants. The simplified Boolean function contains all essential prime implicants and only the required prime implicants.

#### Example

Let us simplify the following Boolean function, fW,X,Y,ZW,X,Y,Z= WX'Y' + WY + W'YZ' using K-map.

The given Boolean function is in sum of products form. It is having 4 variables W, X, Y & Z. So, we require 4 variable K-map. The 4 variable K-map with ones corresponding to the given product terms is shown in the following figure.

| wx YZ | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    |    |    |    | 1  |

| 01    |    |    |    | 1  |

| 11    |    |    | 1  | 1  |

| 10    | 1  | 1  | 1  | 1  |

Here, 1s are placed in the following cells of K-map.

- The cells, which are common to the intersection of Row 4 and columns 1 & 2 are corresponding to the product term, WX'Y'.

- The cells, which are common to the intersection of Rows 3 & 4 and columns 3 & 4 are corresponding to the product term, WY.

- The cells, which are common to the intersection of Rows 1 & 2 and column 4 are corresponding to the product term, W'YZ'.

Here, we got three prime implicants WX', WY & YZ'. All these prime implicants are essential because of following reasons.

- Two ones (m8 & m9) of fourth row grouping are not covered by any other groupings. Only fourth row grouping covers those two ones.

- Single one (m15) of square shape grouping is not covered by any other groupings. Only the square shape grouping covers that one.

- Two ones (m2 & m6) of fourth column grouping are not covered by any other groupings. Only fourth column grouping covers those two ones.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=wjM2RDG5yTI https://www.youtube.com/watch?v=CpsJoAwreqo

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (78)

**Course Teacher**

## **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

### LECTURE HANDOUTS

L 08

II / III

Course Name with Code: 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

#### Unit : I- BOOLEAN ALGEBRA AND LOGIC GATES

Date of Lecture:

Topic of Lecture: Minimization using Tabulation method

#### **Introduction :**

Quine-McClukey tabular method is a tabular method based on the concept of prime implicants. We know that prime implicant is a product orsumorsum term, which can't be further reduced by combining with any other product orsumorsum terms of the given Boolean function.

#### Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

- :

#### Procedure of Quine-McCluskey Tabular Method

Follow these steps for simplifying Boolean functions using Quine-McClukey tabular method.

Step 1 – Arrange the given min terms in an ascending order and make the groups based on the number of ones present in their binary representations. So, there will be at most 'n+1' groups if there are 'n' Boolean variables in a Boolean function or 'n' bits in the binary equivalent of min terms.

Step 2 – Compare the min terms present in successive groups. If there is a change in only one-bit position, then take the pair of those two min terms. Place this symbol '\_' in the differed bit position and keep the remaining bits as it is.

Step 3 – Repeat step2 with newly formed terms till we get all prime implicants.

Step 4 – Formulate the prime implicant table. It consists of set of rows and columns. Prime implicants can be placed in row wise and min terms can be placed in column wise. Place '1' in the cells corresponding to the min terms that are covered in each prime implicant.

Step 5 – Find the essential prime implicants by observing each column. If the min term is covered only by one prime implicant, then it is essential prime implicant. Those essential prime implicants will be part of the simplified Boolean function.

Step 6 – Reduce the prime implicant table by removing the row of each essential prime implicant and the columns corresponding to the min terms that are covered in that essential prime implicant. Repeat step 5 for Reduced prime implicant table. Stop this process when all min terms of given Boolean function are over.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=l1jgq0R5EwQ https://www.youtube.com/watch?v=P0ULm0cbIhE

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (97)

**Course Teacher**

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## LECTURE HANDOUTS

L 09

Course Name with Code: 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

### Unit : I- BOOLEAN ALGEBRA AND LOGIC GATES

Date of Lecture:

**Topic of Lecture:** Minimization using Tabulation method

#### Introduction :

Quine-McClukey tabular method is a tabular method based on the concept of prime implicants. We know that prime implicant is a product or sum term, which can't be further reduced by combining with any other product or sum terms of the given Boolean function.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

Example

Letus simplify thefollowingBoolean

function,  $f(W,X,Y,Z) = \sum m(2,6,8,9,10,11,14,15)f(W,X,Y,Z) = \sum m(2,6,8,9,10,11,14,15)$  using Quine-McClukey tabular method.

The given Boolean function is in sum of min terms form. It is having 4 variables W, X, Y & Z. The given min terms are 2, 6, 8, 9, 10, 11, 14 and 15. The ascending order of these min terms based on the number of ones present in their binary equivalent is 2, 8, 6, 9, 10, 11, 14 and 15. The following table shows these min terms and their equivalent binary representations.

| Group Name | Min terms | W | Х | Y | Z |

|------------|-----------|---|---|---|---|

| GA1        | 2         | 0 | 0 | 1 | 0 |

|            | 8         | 1 | 0 | 0 | 0 |

| GA2        | 6         | 0 | 1 | 1 | 0 |

| 0/12       | 9         | 1 | 0 | 0 | 1 |

|     | 10 | 1 | 0 | 1 | 0 |

|-----|----|---|---|---|---|

| GA3 | 11 | 1 | 0 | 1 | 1 |

|     | 14 | 1 | 1 | 1 | 0 |

| GA4 | 15 | 1 | 1 | 1 | 1 |

The given min terms are arranged into 4 groups based on the number of ones present in their binary equivalents. The following table shows the possible merging of min terms from adjacent groups.

| Group Name | Min terms | W | Х | Y | Z |

|------------|-----------|---|---|---|---|

|            | 2,6       | 0 | - | 1 | 0 |

| GB1        | 2,10      | - | 0 | 1 | 0 |

|            | 8,9       | 1 | 0 | 0 | - |

|            | 8,10      | 1 | 0 | - | 0 |

|            | 6,14      | - | 1 | 1 | 0 |

| GB2        | 9,11      | 1 | 0 | - | 1 |

|            | 10,11     | 1 | 0 | 1 | - |

|            | 10,14     | 1 | - | 1 | 0 |

| GB3        | 11,15     | 1 | - | 1 | 1 |

|            | 14,15     | 1 | 1 | 1 | - |

The min terms, which are differed in only one-bit position from adjacent groups are merged. That differed bit is represented with this symbol, '-'. In this case, there are three groups and each group contains combinations of two min terms. The following table shows the possible merging of min term pairs from adjacent groups.

| Group Name | Min terms   | W | Х | Y | Z |

|------------|-------------|---|---|---|---|

|            | 2,6,10,14   | - | - | 1 | 0 |

| GB1        | 2,10,6,14   | - | - | 1 | 0 |

|            | 8,9,10,11   | 1 | 0 | - | - |

|            | 8,10,9,11   | 1 | 0 | - | - |

| GB2        | 10,11,14,15 | 1 | _ | 1 | - |

|            | 10,14,11,15 | 1 | _ | 1 | - |

The successive groups of min term pairs, which are differed in only one-bit position are merged. That differed bit is represented with this symbol, '-'. In this case, there are two groups and each group contains combinations of four min terms. Here, these combinations of 4 min terms are available in two rows. So, we can remove the repeated rows. The reduced table after removing the redundant rows is shown below.

| Group Name | Min terms   | W | Х | Y | Z |

|------------|-------------|---|---|---|---|

| GC1        | 2,6,10,14   | - | _ | 1 | 0 |

|            | 8,9,10,11   | 1 | 0 | - | - |

| GC2        | 10,11,14,15 | 1 | - | 1 | - |

Further merging of the combinations of min terms from adjacent groups is not possible, since they are differed in more than one-bit position. There are three rows in the above table. So, each row will give one prime implicant. Therefore, the prime implicants are YZ', WX' & WY.

The prime implicant table is shown below.

| Min terms / Prime<br>Implicants | 2 | 6 | 8 | 9 | 10 | 11 | 14 | 15 |

|---------------------------------|---|---|---|---|----|----|----|----|

| YZ'                             | 1 | 1 |   |   | 1  |    | 1  |    |

| WX′                             |   |   | 1 | 1 | 1  | 1  |    |    |

| WY |  |  | 1 | 1 | 1 | 1 |

|----|--|--|---|---|---|---|

|    |  |  |   |   |   |   |

The prime implicants are placed in row wise and min terms are placed in column wise. 1s are placed in the common cells of prime implicant rows and the corresponding min term columns.

The min terms 2 and 6 are covered only by one prime implicant YZ'. So, it is an essential prime implicant. This will be part of simplified Boolean function. Now, remove this prime implicant row and the corresponding min term columns. The reduced prime implicant table is shown below.

| Min terms / Prime<br>Implicants | 8 | 9 | 11 | 15 |

|---------------------------------|---|---|----|----|

| WX′                             | 1 | 1 | 1  |    |

| WY                              |   |   | 1  | 1  |

The min terms 8 and 9 are covered only by one prime implicant WX'. So, it is an essential prime implicant. This will be part of simplified Boolean function. Now, remove this prime implicant row and the corresponding min term columns. The reduced prime implicant table is shown below.

| Min terms / Prime<br>Implicants | 15 |

|---------------------------------|----|

| WY                              | 1  |

The min term 15 is covered only by one prime implicant WY. So, it is an essential prime implicant. This will be part of simplified Boolean function.

In this example problem, we got three prime implicants and all the three are essential. Therefore, the simplified Boolean function is

fW,X,Y,ZW,X,Y,Z = YZ' + WX' + WY.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=l1jgq0R5EwQ https://www.youtube.com/watch?v=P0ULm0cbIhE

#### Important Books/Journals for further learning including the page nos.:

Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (103)

**Course Teacher**

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

| L 15     |  |

|----------|--|

| II / III |  |

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit

: II- COMBINATIONAL LOGIC Date of Lecture:

**Topic of Lecture:** Encoder. Decoder

### Introduction :

Encoder is a combinational circuit that has '2n' input lines and maximum of n output lines.

Decoder is a combinational circuit that has 'n' input lines and maximum of 2n output lines. One of these outputs will be active High based on the combination of inputs present, when the decoder is enabled. That means decoder detects a particular code. The outputs of the decoder are nothing but the min terms of 'n' input variables lines, when it is enabled

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

## ENCODER

An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has 2n (or fewer) input lines and n output lines.

The encoder can be implemented with OR gates whose inputs are determined directly from the truth table. Output z is equal to 1 when the input octal digit is 1, 3, 5, or 7. Output y is 1 for octal digits 2, 3, 6, or 7, and output x is 1 for digits 4, 5, 6, or 7. These conditions can be expressed by the following Boolean output functions:

$$z = D1 + D3 + D5 + D7$$

$y = D2 + D3 + D6 + D7$

$x = D4 + D5 + D6 + D7$

The encoder can be implemented with three OR gates.

|    |                |                | Inp            | uts            |                |                |                | C | )utput | s |

|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|--------|---|

| Do | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | x | y      | z |

| 1  | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0 | 0      | 0 |

| 0  | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0 | 0      | 1 |

| 0  | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0 | 1      | 0 |

| 0  | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0 | 1      | 1 |

| 0  | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 1 | 0      | 0 |

| 0  | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 1 | 0      | 1 |

| 0  | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 1 | 1      | 0 |

| 0  | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1 | 1      | 1 |

The encoder defined in Table 4.7 has the limitation that only one input can be active at any given time. If two inputs are active simultaneously, the output produces an undefined combination. For example, if D3 and D6 are 1 simultaneously, the output of the encoder will be 111 because all three outputs are equal to 1. The output 111 does not present either binary 3 or binary 6.

#### Decoder

Decoder is a combinational circuit that has 'n' input lines and maximum of 2n output lines. One of these outputs will be active High based on the combination of inputs present, when the decoder is enabled. That means decoder detects a particular code. The outputs of the decoder are nothing but the min terms of 'n' input variables lines, when it is enabled.

#### 2 to 4 Decoder

Let 2 to 4 Decoder has two inputs A1 & A0 and four outputs Y3, Y2, Y1 & Y0. The block diagram of 2 to 4 decoder is shown in the following figure.

| Enable | Inputs |    | Outputs |    |    |    |  |

|--------|--------|----|---------|----|----|----|--|

| Е      | A1     | A0 | Y3      | Y2 | Y1 | Y0 |  |

| 0      | X      | X  | 0       | 0  | 0  | 0  |  |

| 1      | 0      | 0  | 0       | 0  | 0  | 1  |  |

| 1      | 0      | 1  | 0       | 0  | 1  | 0  |  |

| 1      | 1      | 0  | 0       | 1  | 0  | 0  |  |

| 1      | 1      | 1  | 1       | 0  | 0  | 0  |  |

From Truth table, we can write the Boolean functions for each output as

**Video Content / Details of website for further learning (if any):** <u>https://www.youtube.com/watch?v=t3Ed13z9uz8</u> https://www.youtube.com/watch?v=4kgPMT9k3bg

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition,2013. Page No (150)

**Course Teacher**

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

CS

II / III

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : II- COMBINATIONAL LOGIC Date of Lecture:

## Topic of Lecture:

Multiplexer/ Demultiplexer

### **Introduction :**

A multiplexer also known as a data selector, is a device that selects between several analog or digital input signals and forwards it to a single output line.

A demultiplexer (or demux) is a device that takes a single input line and routes it to one of several digital output lines. A demultiplexer of 2n outputs has n select lines, which are used to select which output line to send the input.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

## Multiplexer

A multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally, there are 2n input lines and n selection lines whose bit combinations determine which input is selected.

A two-to-one-line multiplexer connects one of two 1-bit sources to a common destination, as shown in Fig. 4.24 .

The outputs of the AND gates are applied to a single OR gate that provides the one-line output. The function table lists the input that is passed to the output for each combination of the binary selection values. To demonstrate the operation of the circuit, consider the case when S1S0 = 10. The AND gate associated with input I2 has two of its inputs equal to 1 and the third input connected to I2. The other three AND gates have at least one input equal to 0, which makes

their outputs equal to 0. The output of the OR gate is now equal to the value of I2, providing a path

from the selected input to the output. A multiplexer is also called a data selector, since it selects one of many inputs and steers the binary information to the output line. The size of a multiplexer is specified by  $I_0$ 0 MUX V 1 L S (b) Block diagram (a) Logic diagram FIGURE 4.24 Two-to-one-line multiplexer 0 101 (b) Function table (a) Logic diagram FIGURE 4.25 the number 2n of its data input lines and the single output line. The n selection lines are implied from the 2n data lines. As in decoders, multiplexers may have an enable input to control the operation of the unit. When the enable input is in the inactive state, the outputs are disabled, and when it is in the active

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=HU31Wh-4\_K8

state, the circuit functions as a normal multiplexer.

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition,2013. Page No (158)

**Course Teacher**

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

| L 17     |  |

|----------|--|

| II / III |  |

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit

: II - COMBINATIONAL LOGIC

Date of Lecture:

**Topic of Lecture:** Introduction to HDL

#### **Introduction :**

A hardware description language (HDL) is a specialized computer language used to describe the structure and behavior of electronic circuits, and most commonly, digital logic circuits.

It also allows for the synthesis of an HDL description into a netlist which can then be placed and routed to produce the set of masks used to create an integrated circuit.

A hardware description language looks much like a programming language such as C or ALGOL; it is a textual description consisting of expressions, statements and control structures.

Prerequisite knowledge for Complete understanding and learning of Topic:

• VLSI

In computer engineering, a hardware description language (**HDL**) is a specialized computer language used to describe the structure and behavior of electronic circuits, and most commonly, digital logic circuits.

HDL is a language that describes the hardware of digital systems in a textual form. It resembles a programming language, but is specifically oriented to describing hardware structures and behaviors.

The main difference with the traditional programming languages is HDL's representation of extensive parallel operations whereas traditional ones represents mostly serial operations. The most common use of a HDL is to provide an alternative to schematics.

When a language is used for the above purpose (i.e. to provide an alternative to schematics), it is referred to as a structural description in which the language describes an interconnection of components.

Models for each of the primitive components are required. If an HDL is used, then these models can also be written in the HDL providing a more uniform, portable representation for simulation input.

HDL can be used to represent logic diagrams, Boolean expressions, and other more complex digital circuits.

There are two applications of HDL processing: Simulation and Synthesis

- To simulate a digital system

- Design is first described in HDL

There are two standard HDL's that are supported by IEEE.

- VHDL (Very-High-Speed Integrated Circuits Hardware Description Language)

- Verilog HDL

A module is the building block in Verilog. It is declared by the keyword module and is always terminated by the keyword end module. Each statement is terminated with a semicolon, but there is no semi-colon after end module

HDL Example

module smpl\_circuit(A,B,C,x,y);

input A,B,C;

output x,y;

wire e;

and g1(e,A,B);

not g2(y,C);

org3(x,e,y);

end module

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=yFRICQtxrj4

### Important Books/Journals for further learning including the page nos.:

Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition, 2013. Page No (154)

**Course Teacher**

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

II / III

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : II -COMBINATIONAL LOGIC Date of Lecture:

## **Topic of Lecture:**

HDL models of combinational circuits

#### Introduction :

The Verilog HDL model of a combinational circuit can be described in any one of the following modeling styles, ü Gate level modeling-using instantiations of predefined and user defined primitive gates. ü Dataflow modeling using continuous assignment with the keyword assign.

Prerequisite knowledge for Complete understanding and learning of Topic:

### • VLSI

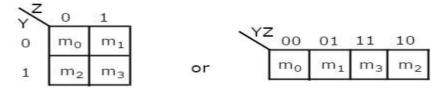

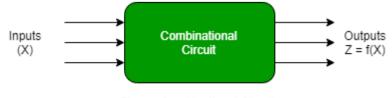

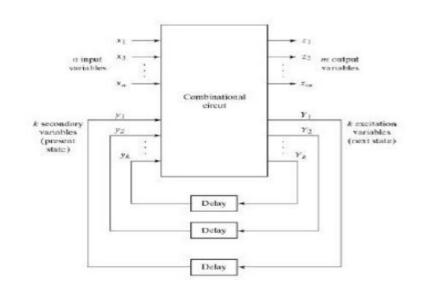

Logic circuits for digital systems may be combinational or sequential. n A combinational circuit consists of input variables, logic gates, and output variables.

Fig. 4-1 Block Diagram of Combinational Circuit

A module can be described in any one (or a combination) of the following modeling techniques.

**Gate-level modeling** using instantiation of primitive gates and user defined modules. This describes the circuit by specifying the gates and how they are connected with each other.

**Dataflow modeling** using continuous assignment statements with the keyword assign. This is mostly used for describing combinational circuits.

**Behavioral modeling** using procedural assignment statements with keyword always. This is used to describe digital systems at a higher level of abstraction.

There are two basic types of design methodologies.

**Top down**: In top-down design, the top level block is defined and then sub-blocks necessary to build the top level block are identified.

Bottom up: Here the building blocks are first identified and then combine to build the top level block.

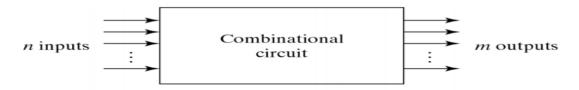

output S,C;

//Instantiate primitive gates xor (S,x,y);

and (C,x,y);

endmodule module fulladder (S,C,x,y,z);

input x,y,z; output S,C;

wire S1,D1,D2;

//Outputs of first XOR and two AND gates

//Instantiate the half adders halfadder HA1(S1,D1,x,y), HA2(S,D2,S1,z); or g1(C,D2,D1);

endmodule

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=CZT7dgX6CTo https://www.youtube.com/watch?v=kgL5UaSVuro

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition,2013. Page No (130)

**Course Teacher**

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

L 10

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit

: II- COMBINATIONAL LOGIC

Date of Lecture:

#### **Topic of Lecture:**

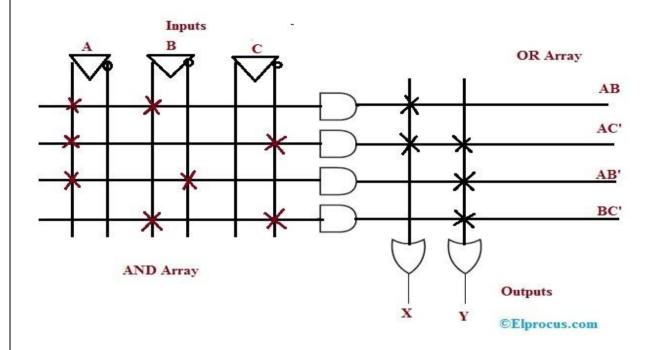

Realization of combinational logic using gates

#### **Introduction** :

Digital circuits are frequently constructed with NAND or NOR gates rather than with AND and OR gates. NAND and NOR gates are easier to fabricate with electronic components and are the basic gates used in all IC digital logic families. Because of the prominence of NAND and NOR gates in the design of digital circuits, rules and procedures have been developed for the conversion from Boolean functions given in terms of AND, OR, and NOT into equivalent NAND and NOR logic diagrams.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

Implement the following Boolean function with NAND gates:

$$F(x, y, z) = (1, 2, 3, 4, 5, 7)$$

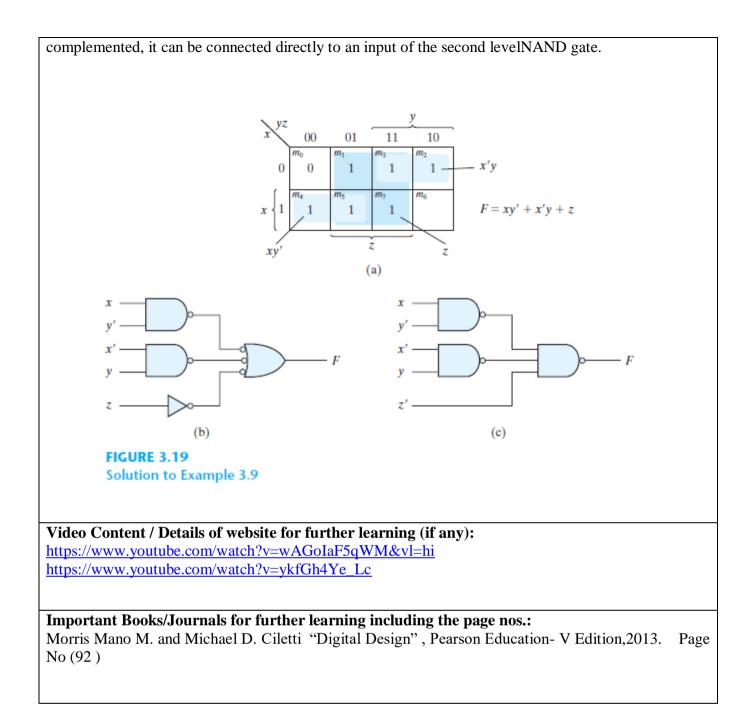

The first step is to simplify the function into sum-of-products form. This is done by means of the map of Fig. 3.19 (a), from which the simplified function is obtained:

$$F = xy_{+} x_{y} + z$$

The two-level NAND implementation is shown in Fig. 3.19 (b) in mixed notation.

Note that input z must have a one-input NAND gate (an inverter) to compensate for the bubble in the second-level gate. An alternative way of drawing the logic diagram is given in Fig. 3.19 (c). Here, all the NAND gates are drawn with the same graphic symbol. Theinverter with input z has been removed, but the input variable is complemented and denoted by z\_.

The procedure described in the previous example indicates that a Boolean function can be implemented with two levels of NAND gates. The procedure for obtaining the logic diagram from a Boolean function is as follows:

1. Simplify the function and express it in sum-of-products form.

2. Draw a NAND gate for each product term of the expression that has at least two literals. The inputs to each NAND gate are the literals of the term. This procedure produces a group of first-level gates.

3. Draw a single gate using the AND-invert or the invert-OR graphic symbol in the second level, with inputs coming from outputs of first-level gates.

4. A term with a single literal requires an inverter in the first level. However, if thesingle literal is

**Course Teacher**

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

LECTURE HANDOUTS

### Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : II- COMBINATIONAL LOGIC Date of Lecture:

#### **Topic of Lecture:**

Design of combinational circuits, Adder , Subtractor

#### **Introduction :**

The basic arithmetic circuits like Binary adder and Binary subtractor. These circuits can be operated with binary values 0 and 1.

#### Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

#### **Binary Adder**

The most basic arithmetic operation is addition. The circuit, which performs the addition of two binary numbers is known as Binary adder. First, let us implement an adder, which performs the addition of two bits.

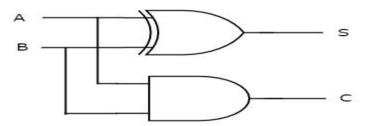

#### Half Adder

Half adder is a combinational circuit, which performs the addition of two binary numbers A and B are of single bit. It produces two outputs sum, S & carry, C.

The Truth table of Half adder is shown below.

|   | Inp      | uts | Outputs |   |  |

|---|----------|-----|---------|---|--|

| А | <b>L</b> | В   | С       | S |  |

| 0 | )        | 0   | 0       | 0 |  |

| 0 | )        | 1   | 0       | 1 |  |

| 1 |          | 0   | 0       | 1 |  |

|  | 1 | 1 | 1 | 0 |  |

|--|---|---|---|---|--|

|  |   |   |   |   |  |

Let, sum, S is the Least significant bit and carry, C is the Most significant bit of the resultant sum. For first three combinations of inputs, carry, C is zero and the value of S will be either zero or one based on the number of ones present at the inputs. But, for last combination of inputs, carry, C is one and sum, S is zero, since the resultant sum is two.

From Truth table, we can directly write the Boolean functions for each output as

#### S=A⊕BS=A⊕B C=ABC=AB

We can implement the above functions with 2-input Ex-OR gate & 2-input AND gate. The circuit diagram of Half adder is shown in the following figure.

In the above circuit, a two input Ex-OR gate & two input AND gate produces sum, S & carry, C respectively. Therefore, Half-adder performs the addition of two bits.

#### **Binary Subtractor**

The circuit, which performs the subtraction of two binary numbers is known as Binary subtractor. We can implement Binary subtractor in following two methods.

- Cascade Full subtractors

- 2's complement method

In first method, we will get an n-bit binary subtractor by cascading 'n' Full subtractors. So, first you can implement Half subtractor and Full subtractor, similar to Half adder & Full adder. Then, you can implement an n-bit binary subtractor, by cascading 'n' Full subtractors. So, we will be having two separate circuits for binary addition and subtraction of two binary numbers.

In second method, we can use same binary adder for subtracting two binary numbers just by doing some modifications in the second input. So, internally binary addition operation takes place but, the output is resultant subtraction.

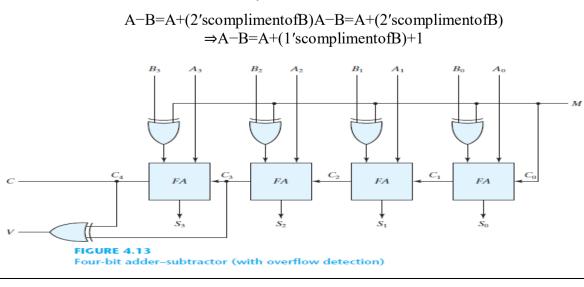

We know that the subtraction of two binary numbers A & B can be written as,

The circuit for subtracting A - B consists of an adder with inverters placed between each data input B and the corresponding input of the full adder. The input carry C0 must be equal to 1 when subtraction is performed. The operation thus performed becomes A, plus the 1's complement of B, plus 1. This is equal to A plus the 2's complement of B. For unsigned numbers, that gives A - B if A Ú B or the 2's complement of 1B - A2 if A 6 B. For signed numbers, the result is A - B, provided that there is no overflow.

**Video Content / Details of website for further learning (if any):** <u>https://www.youtube.com/watch?v=clCQ8J-yk7I</u>

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition,2013. Page No (133)

**Course Teacher**

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

CS

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : II- COMBINATIONAL LOGIC Date of Lecture:

# **Topic of Lecture:**

Parallel adder Subtractor, Carry look ahead adder

### Introduction :

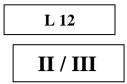

Addition of n-bit numbers requires a chain of n full adders or a chain of one-half adder and n 9 1 full adders. In the former case, the input carry to the least significant position is fixed at 0. The interconnection of four full-adder (FA) circuits to provide a four-bit binary ripple carry adder

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

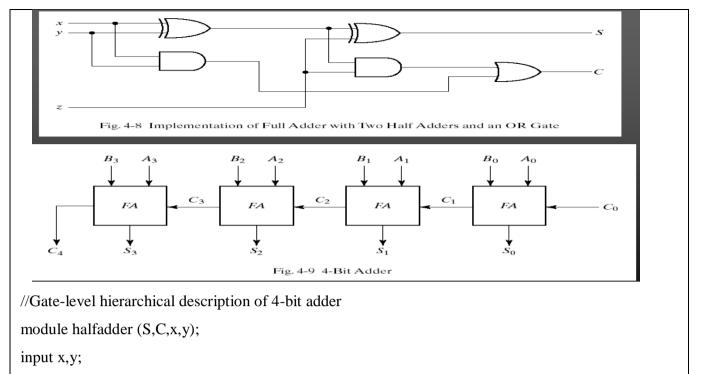

### 4-bit Binary Adder

The 4-bit binary adder performs the addition of two 4-bit numbers. Let the 4-bit binary numbers, A=A3A2A1A0A=A3A2A1A0 and B=B3B2B1B0B=B3B2B1B0. We can implement 4-bit binary adder in one of the two following ways.

- Use one Half adder for doing the addition of two Least significant bits and three Full adders for doing the addition of three higher significant bits.

- Use four Full adders for uniformity. Since, initial carry Cin is zero, the Full adder which is used for adding the least significant bits becomes Half adder.

The block diagram of 4-bit binary adder is

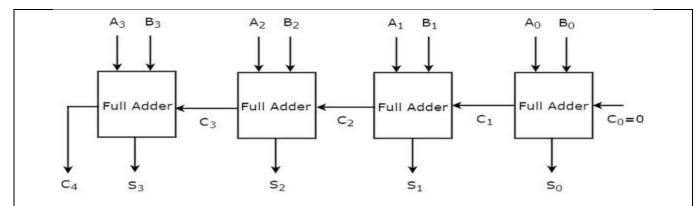

#### **Carry Propagation**

The addition of two binary numbers in parallel implies that all the bits of the augendand addend are available for computation at the same time. As in any combinational circuit, the signal must propagate through the gates before the correct output sum is available in the output terminals. The total propagation time is equal to the propagation delay of a typical gate, times the number of gate levels in the circuit.

the output sum and carry can respectively be expressed as

Si = Pi { Ci

$$Ci+1 = Gi + PiCi$$

Gi is called a carry generate , and it produces a carry of 1 when both Ai and Bi are 1, regardless of the input carry Ci. Pi is called a carry propagate , because it determines whether a carry into stage i will propagate into stage i + 1 (i.e., whether an assertion of Ci will propagate to an assertion of Ci+1 ).

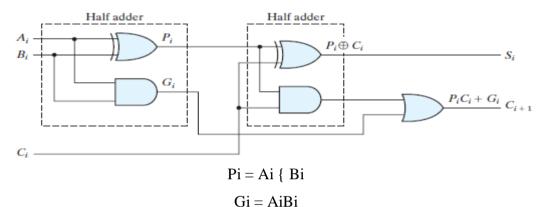

We now write the Boolean functions for the carry outputs of each stage and substitute the value of each Ci from the previous equations:

$$C0 = input carry$$

$$C1 = G0 + P0C0$$

$$C2 = G1 + P1C1 = G1 + P11G0 + P0C02 = G1 + P1G0 + P1P0C0$$

$$C3 = G2 + P2C2 = G2 + P2G1 + P2P1G0 = P2P1P0C0$$

**Course Teacher**

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

CS

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : II- COMBINATIONAL LOGIC Date of Lecture:

**Topic of Lecture:**

Magnitude Comparator, Code conversion

# **Introduction :**

The comparison of two numbers is an operation that determines whether one number is greater than, less than, or equal to the other number. A magnitude comparator is a combinational circuit that compares two numbers A and B and determines their relative magnitudes.

To convert from binary code A to binary code B, the input lines must supply the bit combination of elements as specified by code A and the output lines must generate the corresponding bit combination of code B.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

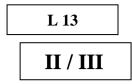

# Magnitude Comparator :

The comparison of two numbers is an operation that determines whether one number is greater than, less than, or equal to the other number. A magnitude comparator is a combinational circuit that compares two numbers A and B and determines their relative magnitudes. The outcome of the comparison is specified by three binary variables that indicate whether A 7 B, A = B, or A 6 B.

The algorithm is a direct application of the procedure a person uses to compare the relative magnitudes of two numbers. Consider two numbers, A and B , with four digits each. Write the coefficients of the numbers in descending order of significance:

$$A = A3 A2 A1 A0$$

$$B = B3 B2 B1 B0$$

the numbers are binary, the digits are either 1 or 0, and the equality of each pair of bits can be expressed logically with an exclusive-NOR function as

$xi = AiBi + A_i B_i$  for i = 0, 1, 2, 3

where xi = 1 only if the pair of bits in position i are equal (i.e., if both are 1 or both are 0).

### **Code Converters:**

The bit combinations assigned to the BCD and excess-3 codes are listed in Table 1.5. Since each code uses four bits to represent a decimal digit, there must be four input variables and four output variables. We designate the four input binary variables by the symbols A, B, C, and D, and the four output variables by w, x, y, and z. The truth table relating the input and output variables is shown in Table 4.2

| Input BCD |   |   |   | Output Excess-3 Code |   |   |   |

|-----------|---|---|---|----------------------|---|---|---|

| Α         | В | C | D | w                    | x | y | z |

| 0         | 0 | 0 | 0 | 0                    | 0 | 1 | 1 |

| 0         | 0 | 0 | 1 | 0                    | 1 | 0 | 0 |

| 0         | 0 | 1 | 0 | 0                    | 1 | 0 | 1 |

| 0         | 0 | 1 | 1 | 0                    | 1 | 1 | 0 |

| 0         | 1 | 0 | 0 | 0                    | 1 | 1 | 1 |

| 0         | 1 | 0 | 1 | 1                    | 0 | 0 | 0 |

| 0         | 1 | 1 | 0 | 1                    | 0 | 0 | 1 |

| 0         | 1 | 1 | 1 | 1                    | 0 | 1 | 0 |

| 1         | 0 | 0 | 0 | 1                    | 0 | 1 | 1 |

| 1         | 0 | 0 | 1 | 1                    | 1 | 0 | 0 |

Video Content / Details of website for further learning (if any): <u>https://www.youtube.com/watch?v=BhUUmbz76P0</u> <u>https://www.youtube.com/watch?v=3BiSCqXXGo0</u>

**Important Books/Journals for further learning including the page nos.:** Morris Mano M. and Michael D. Ciletti "Digital Design", Pearson Education- V Edition,2013. Page No (148)

**Course Teacher**

CS

#### MUTHAYAMMAL ENGINEERING COLLEGE (An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

LECTURE HANDOUTS

II / III

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit

: II- COMBINATIONAL LOGIC

**Date of Lecture:**

Topic of Lecture:

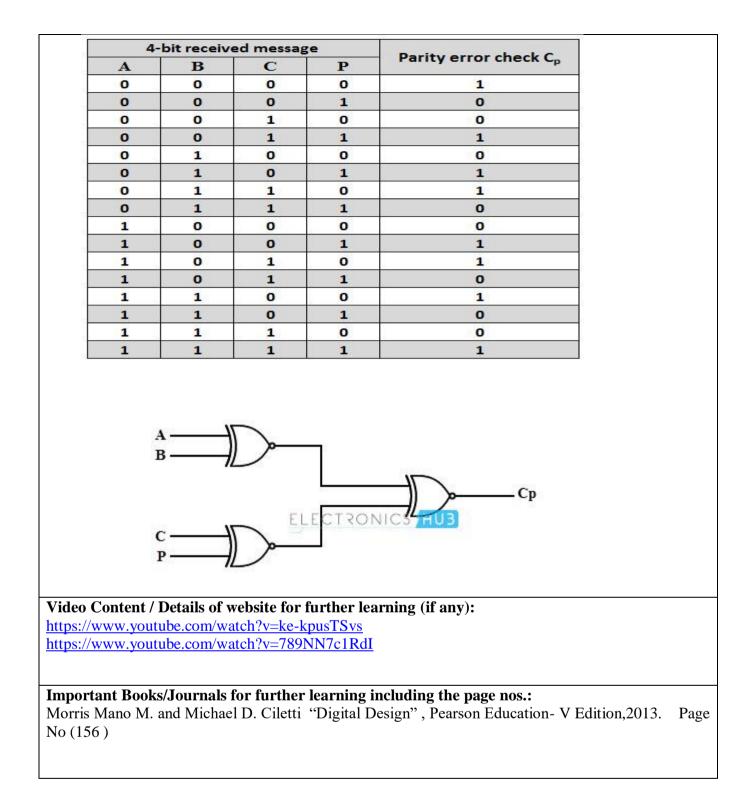

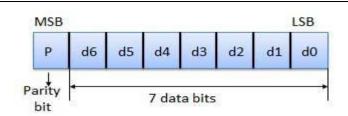

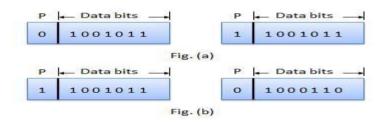

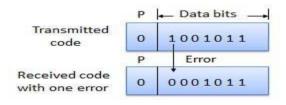

Parity generator and checker

# Introduction :

The parity generating technique is one of the most widely used error detection techniques for the data transmission. In digital systems, when binary data is transmitted and processed, data may be subjected to noise so that such noise can alter 0s (of data bits) to 1s and 1s to 0s.

# Prerequisite knowledge for Complete understanding and learning of Topic:

- Boolean algebra

- Boolean postulates and laws

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

# Parity generator and checker

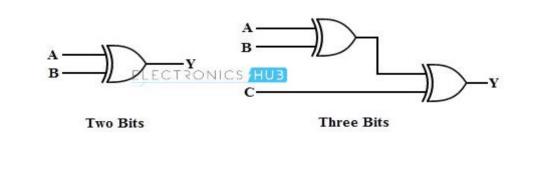

A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. On the other hand, a circuit that checks the parity in the receiver is called parity checker. A combined circuit or devices of parity generators and parity checkers are commonly used in digital systems to detect the single bit errors in the transmitted data word.

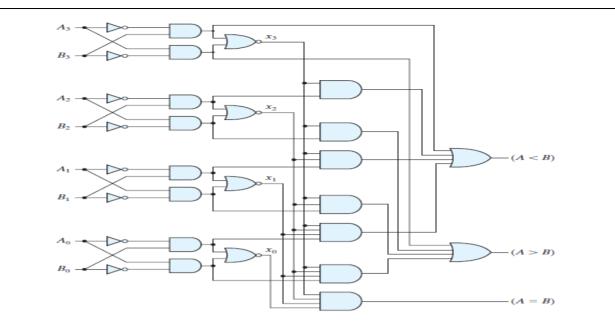

To produce two bits sum, one Ex-OR gate is sufficient whereas for adding three bits two Ex-OR gates are required as shown in below figure.

# **Even Parity Generator**

Let us assume that a 3-bit message is to be transmitted with an even parity bit. Let the three inputs A, B and C are applied to the circuits and output bit is the parity bit P. The total number of 1s must be even, to generate the even parity bit P.

The figure below shows the truth table of even parity generator in which 1 is placed as parity bit in order to make all 1s as even when the number of 1s in the truth table is odd.

| 3- | bit messa | ge | Even parity bit generator (P |  |

|----|-----------|----|------------------------------|--|

| Α  | В         | с  | Y                            |  |

| 0  | 0         | 0  | 0                            |  |

| 0  | 0         | 1  | 1                            |  |

| 0  | 1         | 0  | 1                            |  |

| 0  | 1         | 1  | 0                            |  |

| 1  | 0         | 0  | 1                            |  |

| 1  | 0         | 1  | 0                            |  |

| 1  | 1         | 0  | 0                            |  |

| 1  | 1         | 1  | 1                            |  |

# Parity Check

When a parity error occurs, the 'sum even' output goes low and 'sum odd' output goes high. If this logic circuit is used as an odd parity checker, the number of input bits should be odd, but if an error occurs the 'sum odd' output goes low and 'sum even' output goes high.

### **Odd Parity Checker**

The below figure shows the truth table for odd parity generator where PEC = 1 if the 4-bit message received consists of even number of 1s (hence the error occurred) and PEC= 0 if the message contains odd number of 1s (that means no error).

**Course Teacher**

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

LECTURE HANDOUTS

CS

Course Name with Code : 19GES24/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit : III- SYNCHRONOUS SEQUENTIAL LOGIC Date of Lecture:

# **Topic of Lecture:**

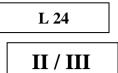

Shift registers - Types - Universal shift registers

### **Introduction :**

A register is a group of flip-flops, each one of which shares a common clock and is capable of storing one bit of information. An n -bit register consists of a group of n flip-flops capable of storing n bits of binary information.

### Prerequisite knowledge for Complete understanding and learning of Topic:

- Latches

- Logic Gates

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

### Shift registers

A register capable of shifting the binary information held in each cell to its neighboring cell, in a selected direction, is called a shift register.

The simplest possible shift register is one that uses only flip-flops, as shown in Fig. 6.3. The output of a given flip-flop is connected to the D input of the flip-flop at its right. This shift register is unidirectional (left-to-right). Each clock pulse shifts the contents of the register one bit position to the right. The configuration does not support a left shift. The serial input determines what goes into the leftmost flip-flop during the shift. The serial output is taken from the output of the rightmost flip-flop. Sometimes it is necessary to control the shift so that it occurs only with certain pulses, but not with others.

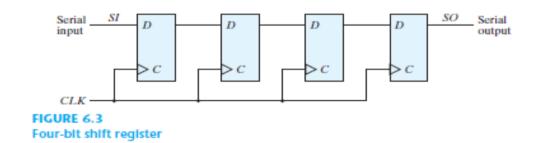

**Universal Shift Register**

If the flip-flop outputs of a shift register are accessible, then information entered serially by shifting can be taken out in parallel from the outputs of the flip-flops. If a parallel load capability is added to a shift register, then data entered in parallel can be taken out in serial fashion by shifting the data stored in the register.

1. A clear control to clear the register to 0.

2. A clock input to synchronize the operations.

3. A shift-right control to enable the shift-right operation and the serial input and output lines associated with the shift right.

4. A shift-left control to enable the shift-left operation and the serial input and output lines associated with the shift left.

5. A parallel-load control to enable a parallel transfer and the n input lines associated with the parallel transfer.

6. n parallel output lines.

7. A control state that leaves the information in the register unchanged in response to the clock. Other shift registers may have only some of the preceding functions, with at least one shift operation.

**Course Teacher**

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

LECTURE HANDOUTS

L 25

II / III

Course Name with Code : 19GES34/Digital Principles and System Design

Course Teacher : Ms.S.Priya, AP/ECE

Unit

: III- SYNCHRONOUS SEQUENTIAL LOGIC

**Date of Lecture:**

**Topic of Lecture:**

Ring counter

### **Introduction :**

Counters can be designed to generate any desired sequence of states. A divide-by- N counter (also known as a modulo- N counter) is a counter that goes through a repeated sequence of N states. The sequence may follow the binary count or may be any other arbitrary sequence. Counters are used to generate timing signals to control the sequence of operations in a digital system. Counters can also be constructed by means of shift registers.

Prerequisite knowledge for Complete understanding and learning of Topic:

- Latches

- Logic Gates

- Canonical forms Sum of product and Product of sum

- Minimization using Karnaugh map

# **Ring Counter**