(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

L 01

## **LECTURE HANDOUTS**

MDE

# Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

**Course Faculty**

: Mrs.M.Birunda

Unit

: I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture: 18.08.2021

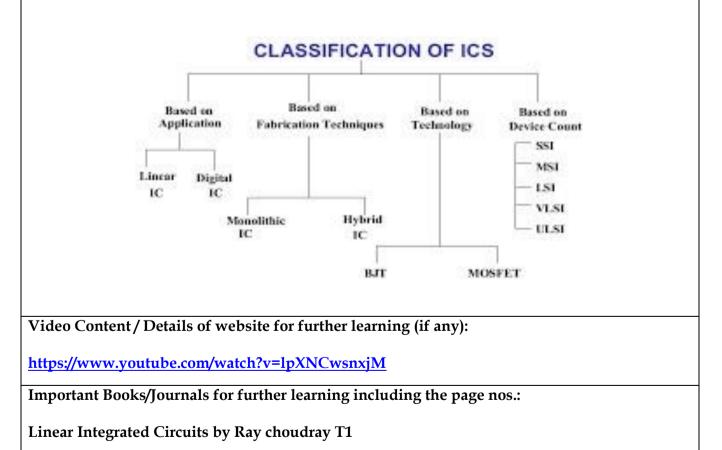

Topic of Lecture: Introduction to Integrated Circuits- & Classification of IC's

#### Introduction :

An integrated circuit or monolithic integrated circuit (also referred to as an IC, a chip, or a microchip) is a set of electronic circuits on one small flat piece (or "chip") of semiconductor material that is normally silicon.

### **Prerequisite knowledge for Complete understanding and learning of Topic:** Basic Analog electronics and Electronic Devices, and Circuit theory

## Introduction to Integrated Circuits- & Classification of IC's:

The concept of IC was first introduced in the year 1958. Due to its small dimension, low cost, and very high reliability even the common man is familiar with its applications like smart phones and laptops. All IC's consist of both active and passive components and the connections between them are so small that it may be impossible to see them even though a microscope. All the components (active and passive) are interconnected through fabrication process.

## **Advantages of Integrated Circuits**

1. Miniature in size. As fabrication process is used for the integration of active and passive components on to a silicon chip, the IC becomes a lot smaller. When compared to a discrete circuit, it may be at least a thousand times smaller.

2. Due to small size, the weight of the IC also reduces, when compared to the discrete circuit.

3. To produce hundreds of discrete circuits on a PCB for the same logic takes more time and increase the cost factor. But for the production of hundreds of IC's the cost of production will be very low and less time consuming.

4. The PCB consisting soldered joints will be less reliable. This problem is omitted in IC's because of no soldered joints, with fewer interconnections, and thus highly reliable.

5. The small size of IC's causes lesser power consumption and lesser power loss.

6. In a discrete circuitry, if a single transistor becomes faulty, the whole circuit may fail to work. This transistor has to be desoldered and replaced. It is difficult to find out which component has failed. This problem can be omitted in an IC by replacing an entire IC as it is low in cost.

7. Increased operating speed because of absence of parasitic capacitance effect.

8. As the IC's are produced in bulk the temperature coefficients and other parameters will be closely matching.

9. Improved functional performance as more complex circuits can be fabricated for achieving better characteristics.

10. All IC's are tested for operating ranges in very low and very high temperatures.

11. As all the components are fabricated very close to each other in an IC, they are highly suitable for small signal operation, as there won't be any stray electrical pickup.

12. As all the components are fabricated inside the chip, there will not be any external projections.

### **Disadvantages of Integrated Circuits**

1. Some complex IC's maybe costly. If such integrated circuits are used roughly and become faulty, they have to be replaced by a new one. They cannot be repaired as the individual components inside the IC are too small.

2. The power rating for most of the IC's does not exceed more than 10 watts. Thus it is not possible to manufacture high power IC's.

3. Some components like transformers and inductors cannot be integrated into an IC. They have to be connected externally to the semiconductor pins.

4. High grade P-N-P assembly is not possible.

5. The IC will not work properly if wrongly handled or exposed to excessive heat.

6. It is difficult to achieve low temperature coefficient.

7. It is difficult to fabricate an IC with low noise.

8. It is not possible to fabricate capacitors that exceed a value of 30pF. Thus, high value capacitors are to be connected externally to the IC.

9. There is a large value of saturation resistance of transistors.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

MDE

II / IV

Course Name with Code ENGINEERS Course Faculty : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL

Unit

: Mrs.M.Birunda

### : I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture: 18.08.2021

Topic of Lecture: Basic IC Fabrication Planar Process-Fabrication of Diode and BJT

### Introduction :

The active and passive components such as resistors, diodes, transistors etc and external connections are usually fabricated in on extremely tiny single chip of silicon. ... In IC chips, the fabrication of circuit elements such as transistors, diodes, capacitors etc. and their interconnections are done at same time.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Basic Analog electronics and Electronic Devices, and Circuit theory Introduction to IC

## **Basic IC Fabrication Planar Process-Fabrication of Diode and BJT:**

The planar process is a manufacturing process used in the semiconductor industry to build individual components of a transistor, and in turn, connect those transistors together. It is the primary process by which silicon integrated circuit chips are built. The process utilizes the surface passivation and thermal oxidation methods.

## P-layer Substrate Manufacture

The silicon is then cut into thin slices with high precision using a diamond saw. After cutting hundreds of them each wafer is polished and cleaned to form a P-type substrate layer.

## N-type Epitaxial Growth

The epitaxial groth process of a low resistive N-type over a high resistive P-type is to be carried out. This is done by placing the n-type layer on top of the P-type and heating.

## The Silicon Dioxide Insulation Layer

This layer is required contamination of the N-layer epitaxy.

## Photolithographic Process for SiO2

To diffuse the impurities with the N-type epitaxial region, the silicon dioxide layer has to be etched in selected areas. Thus openings must be brought at these areas through photolithographic process. In this process, the SiO2 layer is coated with a thin layer of a photosensitive material called photoresist.

## **Isolation Diffusion**

To get a proper time period for allowing a P-type impurity to penetrate into the N-type epitaxial layer, isolation diffusion is to be carried out. By this process, the P-type impurity will travel through the openings in SiO2 layer, and the N-type layer and thus reach the P-type substrate, Isolation junctions are used to isolate between various components of the IC.

#### **Base Diffusion**

This process is done to create a new layer of SiO2 over the wafer. P-regions are formed under regulated environments by diffusing P-type impurities

#### **Emitter Diffusion**

Masking and etching process is again carried out to form a layer of silicon dioxide over the entire surface and opening of the P-type region. The transistor emitters, the cathode regions for diodes, and junction capacitors are grown by diffusion using N-type impurities

#### **Aluminium Metallization**

The windows made in the N-region after creating a silicon dioxide layer are then deposited with aluminium on the top surface.

#### Scribing and Mounting

After the metallization process, the silicon wafer is then scribed with a diamond tipped tool and separated into individual chips.

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=35jWSQXku74

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits by Ray choudray T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

MDE

II / IV

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

# Unit : I - IC FABRICATION AND OPERATIONAL AMPLIFIER

Date of Lecture:

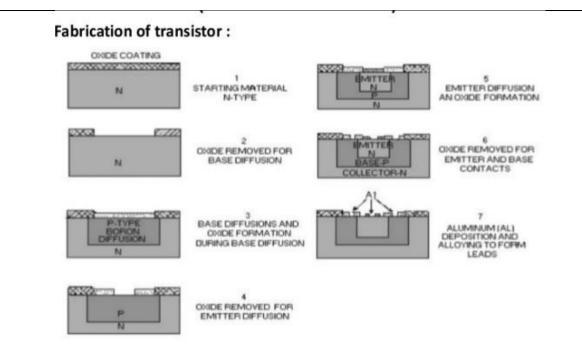

Topic of Lecture: Fabrication of Diode and BJT

#### **Introduction :**

The fabrication of the transistor is the process of creating the transistor that is used in electrical and electronics circuit. It is a photo-lithographic or chemical process of creating the transistor on the wafer of semiconductor material. Two commonly used techniques for Diode Fabrication Process and Packaging are the alloy method and the diffusion method. To construct an alloy diode, a pn-junction is formed by melting a tiny pellet of aluminum (or some other p-type impurity) on the surface of an n-type crystal.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Introduction to IC, Basic IC fabrication process steps.

#### Fabrication of Diode and BJT:

The fabrication process of a transistor is shown in the figure below. A P-type substrate is first grown and then the collector, emitter, and base regions are diffused on top of it as shown in the figure. The surface terminals for these regions are also provided for connection.

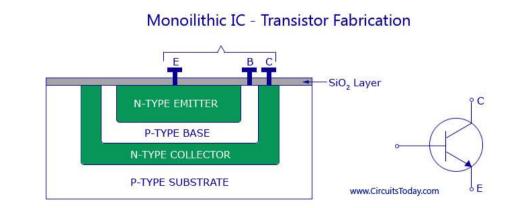

## **Monoilithic IC - Transistor Fabrication**

Both transistors and diodes are fabricated by using the epitaxial planar diffusion process that is explained earlier. In case of discrete transistors, the P-type substrate is considered as the collector. `But this is not possible in monolithic IC's, as all the transistors connected on one P-

type substrate would have their collectors connected together. This is why separate collector regions are diffused into the substrate. Even though separate collector regions are formed, they are not completely isolated from the substrate. For proper functioning of the circuit it is necessary that the P-type substrate is always kept negative with respect to the transistor collector. This is achieved by connecting the substrate to the most negative terminal of the circuit supply. The unwanted or parasitic junctions, even when reverse-biased, can still affect the circuit performance adversely. The junction reverse leakage current can cause a serious problem in circuits operating at very low current levels. The capacitance of the reverse-biased junction may affect the circuit high-frequency performance, and the junction break down voltage imposes limits on the usable level of supply voltage. All these adverse effects can be reduced to the minimum if highly resistive material is employed for the substrate. If the substrate is very lightly doped, it will behave almost as an insulator.

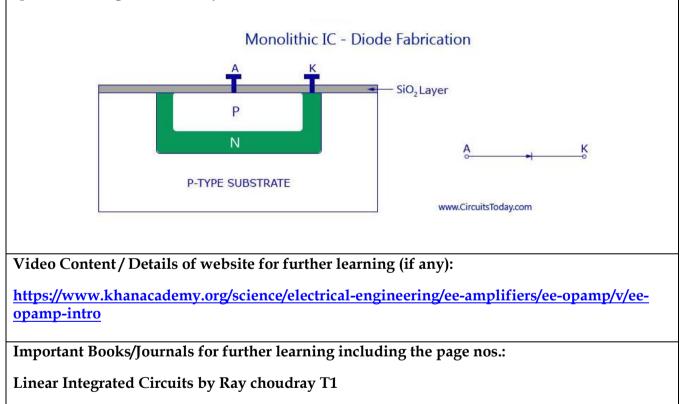

## Diodes

They are also fabricated by the same diffusion process as transistors are. The only difference is that only two of the regions are used to form one P-N junction. In figure, collector-base junction of the transistor is used as a diode. Anode of the diode is formed during the base diffusion of the transistor and the collector region of the transistor becomes the cathode of the diode. For high speed switching emitter base junction is used as a diode.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# LECTURE HANDOUTS

II / IV

10/

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture:

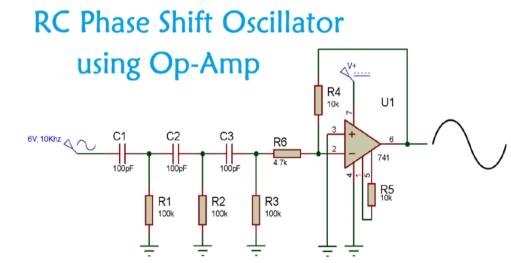

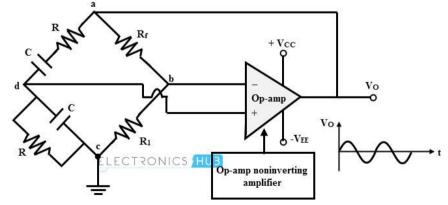

Topic of Lecture: Operational Amplifier: Basic Information of op-amp

### Introduction :

An Operational Amplifier or op-amp is a voltage amplifying device designed to be used with external feedback components such as resistors and capacitors between its output and input terminals. It is a high-gain electronic voltage amplifier with a differential input and usually a single-ended output.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Transistor operation as a differential amplifier

## **Operational Amplifier: Basic Information of op-amp** :

Operational Amplifiers, also known as Op-amps, are basically a voltage amplifying device designed to be used with components like capacitors and resistors, between its in/out terminals. They are essentially a core part of analog devices. Feedback components like these are used to determine the operation of the amplifier. The amplifier can perform many different operations (resistive, capacitive, or both), giving it the name Operational Amplifier.

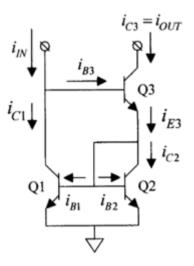

## **Operational Amplifier Block Diagram:**

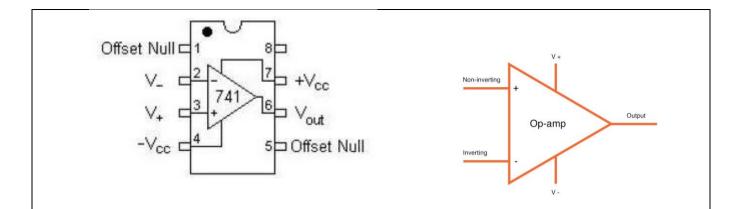

## **OPAMP Pin Configuration:**

Op-amps are linear devices that are ideal for DC amplification and are used often in signal conditioning, filtering or other mathematical operations (add, subtract, integration and d3.8.ifferentiation).

The operational amplifier is arguably the most useful single device in analog electronic circuitry. With only a handful of external components, it can be made to perform a wide variety of analog signal processing tasks. It is also quite affordable, most general-purpose amplifiers selling for under a dollar apiece. Modern designs have been engineered with durability in mind as well: several "op-amps" are manufactured that can sustain direct short-circuits on their outputs without damage.

One key to the usefulness of these little circuits is in the engineering principle of feedback, particularly negative feedback, which constitutes the foundation of almost all automatic control processes. The principles presented in this section, extend well beyond the immediate scope of electronics. It is well worth the electronics student's time to learn these principles and learn them well.

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=kiiA6WTCQn0

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits by Ray choudray T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L 05

**MDE**

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture:

Topic of Lecture: Ideal Op Amp

### Introduction :

An Operational Amplifier or op-amp is a voltage amplifying device designed to be used with external feedback components such as resistors and capacitors between its output and input terminals. It is a high-gain electronic voltage amplifier with a differential input and usually a single-ended output.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Basics of operational amplifier, Operation of Transistor as a differential amplifier.

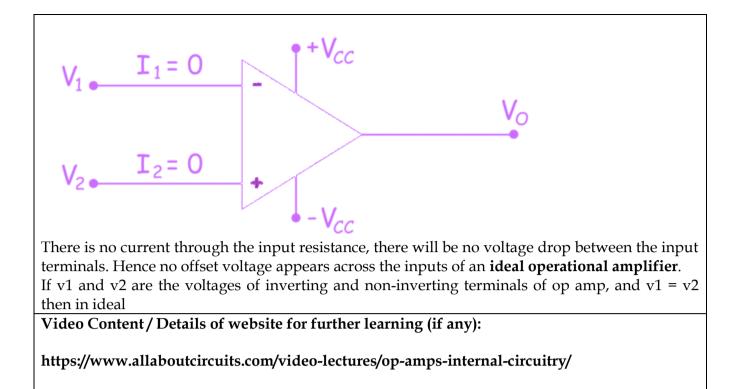

## Ideal Op Amp

We know that, the input resistance of an op amp must be very high where as the output resistance should be quite low. An op amp should also have very high open loop gain. In ideal cases, the input resistance and open loop gain of an op amp should be infinity whereas the output resistance would be zero. So an **ideal op amp** should have following characteristics.

| Characteristic        | Value     |

|-----------------------|-----------|

| Open Loop Gain (A)    | $\propto$ |

| Input Resistance      | $\propto$ |

| Output Resistance     | 0         |

| Bandwith of Operation | $\propto$ |

| Offset Voltage        | 0         |

So, an **ideal op amp** is defined as, a differential amplifier with infinite open loop gain, infinite input resistance and zero output resistance. The **ideal op amp** has zero input current. This is because of infinite input resistance. As the input resistance of **ideal op amp** is infinite, an open circuit exists at input, hence current at both input terminals is zero.

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits by Ray choudray T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

L 06

MDE

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

#### Unit

: I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture:

Topic of Lecture: Operational Amplifier Internal Circuit

### Introduction :

An Operational Amplifier or op-amp is a voltage amplifying device designed to be used with external feedback components such as resistors and capacitors between its output and input terminals. It is a high-gain electronic voltage amplifier with a differential input and usually a single-ended output.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Basic Analog electronics, Operation of Transistor as a differential amplifier, Constant current source.

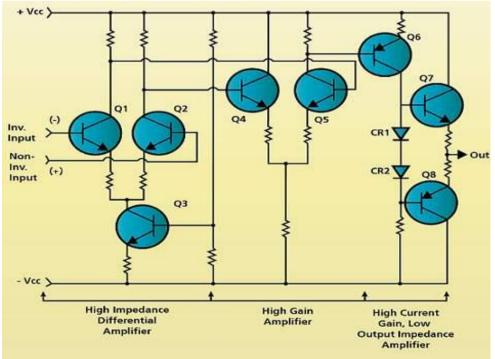

## **Operational Amplifier Internal Circuit :**

• The input signals to the inverting and non-inverting terminals are directly coupled to high impedance, differential amplifier composed of transistors Q` and Q.

- Transistor Q senses the negative and positive supply voltages and functions as a constant current source to regulate against voltage supply variations.

- Transistors Q? and Qr form another differential amplifier to provide additional voltage gain. Transistor Qq controls the biasing of transistors Qo and Qp, which are connected as emitter-followers to provide a high current gain and low output impedance.

- Diodes CR` and CR provide temperature stability.

- The actual operating characteristics of an op amp come very close to the characteristics of an "ideal amplifier.

Video Content / Details of website for further learning (if any):

https://www.allaboutcircuits.com/video-lectures/op-amps-internal-circuitry/

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits by Ray choudray T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

L 07

MDE

II / IV

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture:

Topic of Lecture: Differential Amplifier

#### **Introduction :**

A differential amplifier is designed to give the difference between two input signals. When a differential amplifier is driven at one of the inputs, the output appears at both the collector outputs

**Prerequisite knowledge for Complete understanding and learning of Topic:** Basic Analog electronics and Electronic Devices, and Circuit theory, Transistor operation

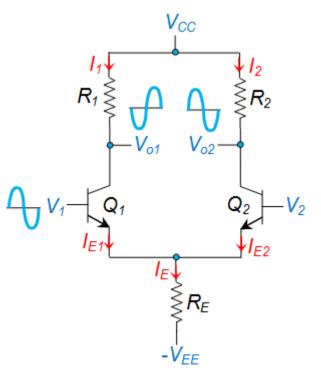

## **Differential Amplifier:**

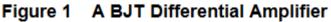

Figure 1 shows such a circuit made of two BJTs (Q1 and Q2) and two power supplies of opposite polarity viz., VCC and -VEE which uses three resistors among which two are the collector

resistors, RC1 and RC2 (one for each transistor) while one is the emitter resistor RE common to both transistors.

Here the input signals (V1 and V2) are applied to the base of the transistors while the output is collected across their collector terminals (Vo1 and Vo2).

$V_0 = A_d (V_1 - V_2)$

Where V1 and V2 represent the voltages applied at its inverting and non-inverting input terminals (can be taken in any order) and Ad refers to its differential gain. As per this equation, the output of the OpAmp must be zero when the voltages applied at its terminals are equal to each other. However practically it will not be so as the gain will not be same for both of the inputs.

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=tC43ztgutwo

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits by Ray choudray T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L 08

MDE

II / IV

## Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture:

Topic of Lecture: Analysis of current sources-Widlar

#### Introduction :

A Widlar current source is a modification of the basic two-transistor current mirror that incorporates an emitter degeneration resistor for only the output transistor, enabling the current source to generate low currents using only moderate resistor values.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Basic Analog electronics and Electronic Devices, and Circuit theory, Basic constant current so working and its necessity

Analysis of current sources-Widlar :

$$egin{aligned} &V_B = V_{BE1} = V_{BE2} + (eta_2 + 1)I_{B2}R_2 \ &\Rightarrow rac{1}{R_2}\left(V_{BE1} - V_{BE2}

ight) = (eta_2 + 1)I_{B2} \;, \ &(eta_2 + 1)I_{B2} = \left(1 + rac{1}{eta_2}

ight)I_{C2} = rac{1}{R_2}\left(V_{BE1} - V_{BE2}

ight) \ &= rac{V_{ ext{T}}}{R_2}\left[\ln(I_{C1}I_{S2}) - \ln(I_{C2}I_{S1})

ight] = rac{V_{ ext{T}}}{R_2}\lnigg(rac{I_{C1}I_{S2}}{I_{C2}I_{S1}}igg) \end{aligned}$$

Finding the current with given resistor values

$$\begin{split} I_{R1} &= I_{C1} + I_{B1} + I_{B2} \\ &= I_{C1} + \frac{I_{C1}}{\beta_1} + \frac{I_{C2}}{\beta_2} \\ &= \frac{1}{R_1} \left( V_{CC} - V_{BE1} \right) \\ I_{C1} &= \frac{\beta_1}{\beta_1 + 1} \left( \frac{V_{CC} - V_{BE1}}{R_1} - \frac{I_{C2}}{\beta_2} \right) \\ V_{BE1} &= V_{T} \ln \left( \frac{I_{C1}}{I_{S1}} \right) . \\ I_{C2} &= \frac{V_{T}}{\left( 1 + \frac{1}{\beta_2} \right) R_2} \ln \left( \frac{I_{C1}}{I_{C2}} \right) \end{split}$$

These three relations are a nonlinear, implicit determination for the currents that can be solved by iteration.

- We guess starting values for  $I_{C1}$  and  $I_{C2}$ .

- We find a value for  $V_{\text{BE1}}$ :

$$egin{aligned} V_{BE1} &= V_{

m T} \ln igg(rac{I_{C1}}{I_{S1}}igg) \ &I_{C1} &= rac{eta_1}{eta_1 + 1} \left(rac{V_{CC} - V_{BE1}}{R_1} - rac{I_{C2}}{eta_2}igg) \ &I_{C2} &= rac{V_{

m T}}{igg(1 + rac{1}{eta_2}igg) R_2} \ln igg(rac{I_{C1}}{I_{C2}}igg) \,. \end{aligned}$$

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=B6yus5h8Sek

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits by Ray choudray T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L 09

MDE

II / IV

## Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: I - IC FABRICATION AND OPERATIONAL AMPLIFIER Date of Lecture:

Topic of Lecture: Wilson Current Sources

#### Introduction :

A Wilson current mirror or Wilson current source, named after George Wilson, is an improved mirror circuit configuration designed to provide a more constant current source or sink. It provides a much more accurate input to output current gain.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Basic Analog electronics and Electronic Devices, and Circuit theory, Basic constant current so working and its necessity

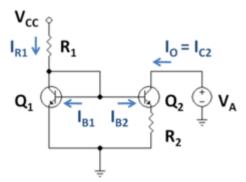

Wilson Current Sources :

- There are three principal metrics of how well a current mirror will perform as part of a larger circuit. The first measure is the static error, the difference between the input and output currents expressed as a fraction of the input current.

- Minimizing this difference is critical in such applications of a current mirror as the differential to single-ended output signal conversion in a differential amplifier stage because this difference controls the common mode and power supply rejection ratios.

- The second measure is the output impedance of the current source or equivalently its inverse, the output conductance.

- This impedance affects stage gain when a current source is used as an active load and

affects common mode gain when the source provides the tail current of a differential pair.

• The last metric is the pair of minimum voltages from the common terminal, usually a power rail connection, to the input and output terminals that are required for proper operation of the circuit.

The Wilson current mirror has the particular advantages over alternatives that:

- . The static error, the input-output current difference, is reduced to very small levels attributable almost entirely to random device mismatches while the output impedance is raised by a factor of {\displaystyle \scriptstyle {\frac {\beta }{2}}} simultaneously

- The circuit uses minimum resources. It does not require additional bias voltages or large area resistors as do cascaded or resistively degenerated mirrors.

- The low impedance of its input and internal nodes makes it possible to bias the circuit for operation at frequencies up to {\displaystyle \scriptstyle {\frac {f\_{T}}{10}}}.

- The four-transistor version of the circuit has extended linearity for operation at high currents.

The Wilson current mirror has the limitations that:

- The minimum potentials from input or output to the common rail connection that are needed for proper operation are higher than for the standard two-transistor mirror. This reduces the headroom available to generate the input current and limits the compliance of the output.

- This mirror uses feedback to raise the output impedance in such a way that the output transistor contributes collector current fluctuation noise to the output. All three transistors of the Wilson current mirror add noise to the output.

- For stable, low-noise operation it may be necessary to modify the circuit to eliminate this effect.

- In some applications of a current mirror, particularly for biasing and active load applications, it is advantageous to produce multiple current sources from a single input reference current.

- This is not possible in the Wilson configuration while maintaining an accurate match of the input current to the output currents.{\displaystyle V\_{BE1}=V\_{\text{T}}\ln \left({\frac {I\_{C1}}{I\_{S1}}}\right)\.}

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=CiXfrsx0--Q

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits by Ray choudray T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

MDE

IQAC

L 10

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: II - Characteristics of OP Amp and Applications

Date of Lecture:

Topic of Lecture: Characteristics of Op- Amp - DC Characteristics

## Introduction :

Operational Amplifier: The operational amplifier is a direct-coupled high gain amplifier.

It is a versatile multi-terminal device that can be used to amplify dc as well as ac input signals. It was originally designed for performing mathematical operations such as addition, subtraction, multiplication and integration and is abbreviated as op-amp.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Operational Amplifier

## Dc characteristics:

An ideal op- amp draws no current from the source and its response is also independent of temperature. However, a real op-amp does not work this way. Current is taken from the source into the op-amp inputs. Also the inputs respond differently to current and voltage due to mismatch in transistors. A real op-amp also shifts its operation with temperature. These non- ideal dc characteristics that add error components to the dc output voltage are:

- 1. Input bias current

- 2. Input offset current

- 3. Input offset voltage

- 4. Thermal drift

# 1. Input bias current:

It is defined as the average value of the base currents entering into the input terminals of an op-amp during the input bias current. The op-amp input is a differential amplifier, which may be made of BJT or FET. In either case, the input transistors must be biased into their linear region by supplying currents into the bases by the external circuit.

In an ideal op-amp we assume that no current is drawn from the input terminals. However, practically, input terminals do conduct a small value of dc current to bias the input transistors.

The base currents entering into the inverting and non-inverting terminals are shown as  $IB^{(-)}$  and  $IB^{(+)}$  respectively.

Even though both the transistors are identical,  $IB^{(-)}$  and  $IB^{(+)}$  are not exactly equal due to internal imbalances between the two inputs.

$IB = IB^{(+)} + IB^{(-)}/2$ ,

Where IB<sup>^</sup> (+) - bias current at non- inverting terminal IB (-) - bias current at inverting

### terminal

Input bias current compensation:

## • IB for BJT is 500Ma

• IB for FET is 50pA

By introducing compensation resistor at the non-inverting input terminal we can able to reduce the input bias current.

Rcomp=R1/ Rf= (R1\* Rf) / (R1+Rf)

# 2. Input offset current:

Bias current compensation will work efficiently if both the bias currents  $IB^{(+)}$  and  $IB^{(-)}$  are equal. The input transistors cannot be made identical. Hence there will be difference in bias currents. This difference is called as input offset current Ios and can be written as

$$| \text{ Ios } | = \text{IB}^{(+)} - \text{IB}^{(-)}$$

The absolute value sign indicates that there is no way to predict which of the bias currents will be larger.

Input offset current for BJT is 200nA.

Input offset current for FET is 10pA.

The effect of Ios can be minimized by having the feedback resistor value to be small.

## 3. Input offset voltage:

In spite of the use of the above compensation techniques, it is found that the output voltage may still not be zero with zero input voltage. This is due to unavoidable imbalances inside the op-amp and one may have to apply a small voltage at the input terminals to make output voltage zero. This voltage is called input offset voltage Vios. This is the voltage required to be applied at the input for making output voltage to zero volts.

The voltage V2 at negative terminal is

$V2 = R \ 1.V0/R1 + Rf \ Or$  V0 = (R1 + Rf)V2/R1 = (1 + Rf/R1)V2Since VOS = |Vi - V2| and  $Vi = 0 \ VOS = |0 - V2| = V2$

## 4. Thermal drift:

Bias current, offset current and offset voltage change with temperature. A circuit carefully mulled at 25 degree Celsius may not remain so when the temperature rises to 35 degree Celsius. This is called drift. Often, offset current drift is expressed in nA/0C and offset voltage drift in mV/0C. These indicate the change in offset for each degree Celsius change in temperature.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=uyOfonR\_rEw

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication "Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs". Maxim Application Note 1108. Archived from the original on 2007-06-26. Retrieved November 10, 2007.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

II / IV

L 11

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: II - Characteristics of OP Amp and Applications

Date of Lecture:

**Topic of Lecture:** AC Characteristics, Frequency Response – Frequency Compensation, Slew rate

## Introduction :

Operational Amplifier: The operational amplifier is a direct-coupled high gain amplifier.

It is a versatile multi-terminal device that can be used to amplify dc as well as ac input signals. It was originally designed for performing mathematical operations such as addition, subtraction, multiplication and integration and is abbreviated as op-amp.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Operational Amplifier

## Detailed content of the Lecture:

## Ac characteristics:

For small signal sinusoidal applications the a.c. characteristics are

1. Frequency response

2. Slew rate

# 1. Frequency response:

An ideal op-amp has infinite band width that is open loop gain is 90dB with d.c.signal and this gain should remain the same through audio and radio frequency.

But practically op-amp gain decreases at high frequency. This is due to a capacitive component in the equivalent circuit of op-amp.

Due to R0C, the gain decreases by 20 dB per decay and the frequency is said to be brake or corner frequency and is given by

# 2. Slew rate:

The slew rate is defined as the maximum rate of change of output voltage caused by a step input voltage and is usually specified in V/ $\mu$ s. for e.g. A 1V/ $\mu$ s slew rate means that the output rises or falls by 1V in one 1 $\mu$ s.

The rate of change of output voltage due to the step input voltage and is usually specified as V/micro sec.

For example: 1V/micro sec. slew rate denotes the output rises or falls by 1 volts in 1 micro seconds. The rate at which the voltage across the capacitor dVc/dt is given by dVc/dt = I/C Slew rate SR dVc/dt | max = Imax/C

### For IC741

Imax= 15 micro amps, C= 30 Pico farad Slew rate = 0.5V/ micro sec.

## **Frequency Compensation**

However, all techniques are categorized into two basic types of compensation technique. The first one is external compensation across the op-amp and the second one is the internal compensation technique.

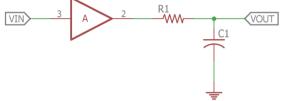

## 1. Dominant pole Compensation

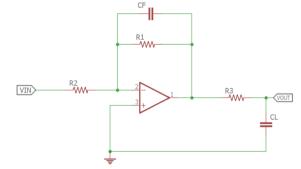

This technique uses a simple RC network connected across the output of the operational amplifier circuit. A sample dominant pole compensation circuit is shown below.

This works great to overcome the instability issue. The RC network creates a pole at unity or 0dB gain that dominates or cancels out other high-frequency poles effect. The transfer function of the dominant pole configuration is –

$$A(s) = \frac{A \times \omega 1 \times \omega 2 \times \omega 3}{(s + \omega 1) \times (s + \omega 2) \times (s + \omega 3)}$$

Where, A(s) is the uncompensated transfer function, A is the open-loop gain,  $\omega 1$ ,  $\omega 2$ , and  $\omega 3$  are the frequencies where the gain roll-off at -20dB, -40dB, -60dB respectively. The Bode plot below shows what happens if the dominant pole compensation technique is added across the op-amp output, where fd is the dominant pole frequency.

## 2. Miller compensation

Another effective compensation technique is the miller compensation technique and it is an in-loop compensation technique where a simple capacitor is used with or without load isolation resistor (Nulling resistor). That means a capacitor is connected in the feedback loop to compensate the op-amp frequency response.

The miller compensation circuit is shown below. In this technique, a capacitor is connected to the feedback with a resistor across the output.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=uyOfonR\_rEw

## Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication "Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs". Maxim Application Note 1108. Archived from the original on 2007-06-26. Retrieved November 10, 2007.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

L 12

MDE

II / IV

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: II - Characteristics of OP Amp and Applications

Date of Lecture:

Topic of Lecture: Applications: Closed Loop Op Amp Configuration

## Introduction :

In this configuration, the input voltage signal, (VIN) is applied directly to the non-inverting ( + ) input terminal which means that the output gain of the amplifier becomes "Positive" in value in contrast to the "Inverting Amplifier" circuit whose output gain is negative in value. The result of this is that the output signal is "in-phase" with the input signal.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Operational Amplifier

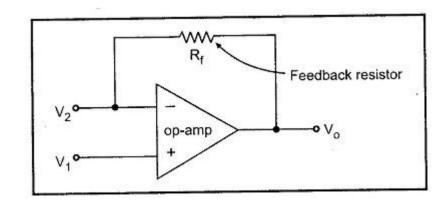

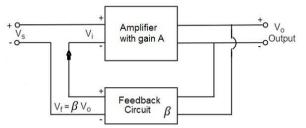

# **Closed Loop Op Amp Configuration:**

- The op-amp can be effectively utilized in linear applications by providing a feedback from the output to the input, either directly or through another network.

- If the signal feedback is out- of-phase by 1800 with respect to the input, then the feedback is referred to as negative feedback or degenerative feedback.

- Conversely, if the feedback signal is in phase with that at the input, then the feedback is referred to as positive feedback or regenerative feedback

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=uyOfonR\_rEw

## Important Books/Journals for further learning including the page nos.:

- Linear Integrated Circuits Sixth Edition Ganesh Babu T.R, Suseela B, SCITECH Publication

- Programmable OP-AMP Configurations Mayuresh Sardar, Dept. of Electronics and Tele Communication Engineering, Vishwakarma Institute of Information Technology, International Research Journal of Engineering and Technology (IRJET), Volume: 03 Issue: 10 | Oct -2016

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L 13

MDE

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: II - Characteristics of OP Amp and Applications

Date of Lecture:

Topic of Lecture: Inverting and Non inverting Amplifiers, Inverters

## Introduction :

In this configuration, the input voltage signal, (VIN) is applied directly to the non-inverting (+) input terminal which means that the output gain of the amplifier becomes "Positive" in value in contrast to the "Inverting Amplifier" circuit whose output gain is negative in value. The result of this is that the output signal is "in-phase" with the input signal.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Operational Amplifier

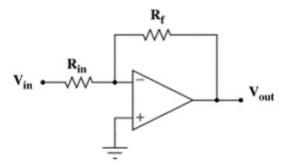

## **Inverting Amplifier:**

The output voltage V0 is feedback to the inverting input terminal through Rf – R1 network where Rf is the feedback resistor. Input signal is applied to the inverting input through R1and non-inverting input terminal is grounded.

## Analysis:

For simplicity assume an ideal op-amp for analysis. As Vd = 0, node'a' is at ground potential an the current i1 through R1 is

i1= Vi/ R1

Since op-amp draws no current all the current flowing through R1must flow through Rf. Therefore Output voltage ,

V0 = -i1Rf = -ViRf/R1

Gain ACL =

$$V0/Vi = -Rf/R1$$

Negative sign indicates a phase shift of 1800 between Vi and V0. R1 should be kept fairly large to avoid loading effect.

### Non-inverting Amplifier:

Here the signal is applied to the positive input terminal and feedback is given; the circuit amplifies without inverting the input signal hence it is called non-inverting amplifier. The voltage at node 'a' is Vi.

Vi = (V0/R1+Rf).R1 V0/Vi = (Ri+Rf)/R1 = 1+Rf/R1i.e. ACL = 1+Rf/R1

The gain can be adjusted to unity or more by proper seletion of resistors Rf and R1. Comparing with inverting amplifier the input resistance Ri is extremely large.

## Inverter

An inverter can be defined as it is a compact and rectangular shaped electrical equipment used to convert direct current (DC) voltage to alternating current (AC) voltage in common appliances. Direct current is used in many of the small electrical equipment such as solar power systems, power batteries, power-sources, fuel cells because these are simply produced direct current.

These devices are standalone devices for some applications like solar power. There are different types of inverters available in the market based on the switching waveform shape. An inverter uses DC power sources to provide an AC voltage to giving the supply to the electronic as well as electrical equipment.

## Working of Inverter

The working of an inverter is, it converts DC to AC, and these devices never generate any kind of power because the power is generated by the DC source. In some situations like when the DC voltage is low then we cannot use the low DC voltage in a home appliance. So due to this reason, an inverter can be used whenever we utilize solar power panel.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=uyOfonR\_rEw

**Important Books/Journals for further learning including the page nos.:** Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication Programmable OP-AMP Configurations Mayuresh Sardar, Dept. of Electronics and Tele Communication Engineering, Vishwakarma Institute of Information Technology, International Research Journal of Engineering and Technology (IRJET), Volume: 03 Issue: 10 | Oct -2016

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

MDE

L 14

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

## : II - Characteristics of OP Amp and Applications

Date of Lecture:

Topic of Lecture: Voltage Follower, Summing Amplifier, Averaging Circuits - Subtractor

### Introduction :

Unit

An op-amp based adder produces an output equal to the sum of the input voltages applied at its inverting terminal. It is also called as a summing amplifier, since the output is an amplified one. In the above circuit, the non-inverting input terminal of the op-amp is connected to ground.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Operational Amplifier, Differential Amplifier

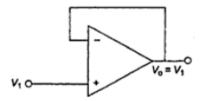

## Voltage follower:

The output voltage follows the input voltage exactly hence the circuit is called a voltage follower. Voltage follower is obtained from the non-inverting amplifier if Rf = 0 and  $R1 = \infty$ . V0 = Vi

Voltage follower is used as buffer for impedance matching. i.e. to connect a high impedance source to a low impedance load.

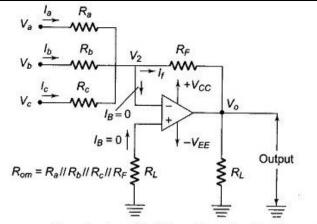

## **Summing Amplifier Circuit:**

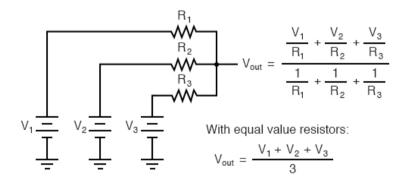

Figure shows an Summing Amplifier Circuit in inverting configuration with three inputs Va, Vb, Vc. Depending on the relation between Ra, Rb, Rc and RF, the circuit can be used as a Summing amplifier, Scaling amplifer or Average ampli-fier.

Fig.

Using Kirchoff's circuit equation, we have la + lb + lc = IB + If. But  $IB \equiv 0$  and  $V1 \equiv V2 \equiv 0$ Therefore

$$I_a + I_b + I_c = I_f$$

$$\frac{V_a}{R_a} + \frac{V_b}{R_b} + \frac{V_c}{R_c} = -\frac{V_o}{R_F}$$

$$R_a = R_b = R_c$$

$$V_o = -\frac{R_F}{R_a} (V_a + V_b + V_c)$$

In this circuit Ra = Rb = Rc = RF. Therefore Vo = -(Va + Vb + Vc). (14.7) Hence the output voltage is the negative sum of all the input voltages. If each input voltages is amplified by a different factor, i.e. weighted differently at the output, the circuit is called a scaling or weighted amplifier. The condition can be obtained by making Ra, Rb, and Rc, different in value. The output voltage of the scaling amplifier is then

$$V_o = -\left(\frac{R_F}{R_a}V_a + \frac{R_F}{R_b}V_b + \frac{R_F}{R_c}V_c\right)$$

where  $R_F/R_a \neq R_F/R_b \neq R_F/R_c$ .

In this amplifier, the output voltage is the average value of the input voltages. This modification can be obtained by making Ra = Rb = Rc. = R. Also, the gain by which input is amplified must be equal to 1 over the number of inputs, i.e. RF/R = 1/n where n is the number of inputs. Therefore the output voltage is given by Vo = Va + Vb + Vc. Therefore the output voltage for three inputs is RF/R = 1/3. The output voltage is given by

$$V_o = -\frac{V_a + V_b + V_c}{3}$$

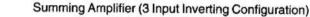

Subtractor

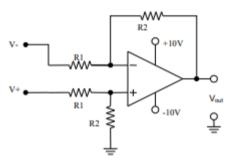

A subtractor circuit using a basic differential amplifier is as shown in Fig.

By selecting the appropriate values for the external resistance, the input signal can be scaled (attenuated) to the desired value. If this is done, the circuit is referred to as a scaling amplifier.

As in Fig., all values of the external resistance are equal, and the gain of the amplifier is unity.

Therefore, the output voltage of differential amplifier with unity gain is

$$V_o = -\frac{R}{R} [V_a - V_b]$$

$$V_o = -[V_a - V_b]$$

Hence the circuit is called a subtractor.

### **Averaging Amplifier**

An Averaging Amplifier is a variation of a Summing Amplifier. The input resistors must all be the same –in this case they are all set to 100 k $\Omega$ . The feedback resistor is selected so that its value of the value of RF divided by the number of inputs. So RF = 100 k $\Omega/4$  = 25 k $\Omega$ "Passive Averager" Circuit

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=3RRSR6SByz4

**Important Books/Journals for further learning including the page nos.:** Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication Paul Horowitz and Winfield Hill, <u>The Art of Electronics</u>. 2nd ed. Cambridge University Press, Cambridge, 1989 <u>ISBN 0-521-37095-7</u>

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

# **LECTURE HANDOUTS**

L 15

**MDE**

II / IV

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

## : II - Characteristics of OP Amp and Applications

Date of Lecture:

Topic of Lecture: Differential Amplifier, Multiplier, Differentiator

## Introduction :

Unit

A differential amplifier is a type of electronic amplifier that amplifies the difference between two input voltages but suppresses any voltage common to the two inputs. Differentiator or Differentiation amplifier is a circuit which performs mathematical operation of differentiation. i.e., the output waveform is the derivative of the input waveform.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Operational Amplifier, Differential Amplifier

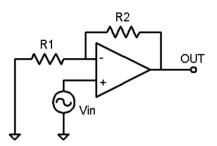

# **Differential Amplifier**

Applying KCL,

$$\frac{V_2 - V_X}{R_1} = \frac{V_X - 0}{R_2}$$

$$\therefore \frac{V_2}{R_1} = \frac{V_X}{R_1} + \frac{V_X}{R_2}$$

$$\frac{V_2}{R_1} = V_X \left[ \frac{1}{R_1} + \frac{1}{R_2} \right]$$

$$V_X = V_Y$$

$$V_X = \frac{V_2}{R_1 \left[ \frac{1}{R_1} + \frac{1}{R_2} \right]} = \frac{V_2}{\left( 1 + \frac{R_1}{R_2} \right)}$$

Similarly Vy

$$\begin{split} V_1 &= V_Y \Bigg[ 1 + \frac{R_1}{R_2} \Bigg] - V_0 \, \frac{R_1}{R_2} \\ V_1 &= \frac{V_2}{1 + \frac{R_1}{R_2}} \Bigg[ 1 + \frac{R_1}{R_2} \Bigg] - V_0 \, \frac{R_1}{R_2} \\ V_0 &= \frac{R_2}{R_1} \Big[ V_2 - V_1 \Big] \end{split}$$

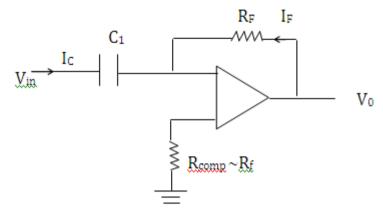

**Ideal Differentiator**

The node A is at virtual ground i.e., VA= 0  $\,$

The current through capacitor is The circuit iF though RF is given by

$$I_F = \frac{V_0 - V_A}{R_F} = \frac{V_0}{R_F}$$

.....(2) since  $V_A = 0$

At node A, by KCL (i.e) equations (1) + (2)

$$I_{C} + I_{F} = 0$$

$$\Rightarrow C_{1} \frac{d.V_{in}}{dt} + \frac{V_{0}}{R_{F}} = 0$$

$$C_{1} \frac{d.V_{in}}{dt} = -\frac{V_{0}}{R_{F}}$$

$$V_{0} = -R_{F}.C_{1}.\frac{d.V_{in}}{dt}$$

------(A)

$\Rightarrow$

Thus the outputvoltage, V0 is (-RFC1) times the derivative of input voltage Vin. The minus indicates phase shift of 180° between i/p signals. Writing eq

$$V_0(s) = -R_F C_1 . S . V_{IN}(S)$$

Now gain 'A' of the differentiator is

$$|A| = \left| \frac{V_0(s)}{V_{in}(s)} \right| = |-SR_F.C_1| = |-j\omega.R_F.C_1| = \omega.R_F.C_1$$

(s = j\omega, \omega = 2\pi f)

$$\therefore |A| = 2\pi f.R_FC_1 = \frac{f}{fa}$$

Where

$$fa = \frac{1}{2\pi R_F C_1}$$

At f=fa, |A| = 1, i.e 0 dB and gain increases at a rate of +20dB/decade.

Demerits

The i/p impedance (1/ $\omega$ C1) decreases with increase in frequency, thereby making the circuit sensitive to high frequency noise.

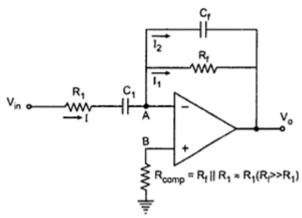

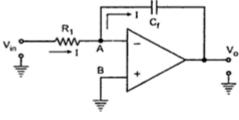

Also, at high frequencies, the circuit becomes unstable and enters into oscillation. **Practical Differentiator**

#### Practical differentiator circuit

Both stability and high frequency noise problems can be corrected by adding two components, R1 & CF as shown in above circuit. The transfer function of this circuit is

For

$$\frac{V_0(s)}{V_{in}(s)} = \frac{-Z_f}{Z_i} = \frac{-SR_FC_1}{(1+SR_1C_1)(1+SR_FC_F)}$$

R1C1 = RFCF,

$|A| = \left|\frac{V_0(s)}{V_{in}(s)}\right| = \frac{-SR_FC_1}{(1+SR_1C_1)^2} = \frac{-SR_FC_1}{\left(1+j\frac{f}{fb}\right)^2}$

where

$$f_{b} = \frac{1}{2\pi R_{1}C_{1}} = \frac{1}{2\pi R_{F}C_{F}}$$

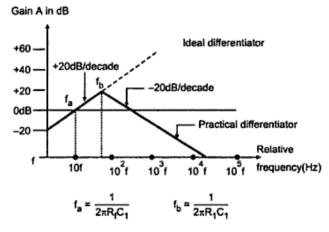

Frequency response

fa is the frequency at which gain is 0 dB.

fb is the gain limiting frequency

fC is the unity gain bandwidth of Op-Amp.

#### Frequency response of the practical differentiator

From fa to fb gain increases at rate of +20db/decade. After fb the gain decreases at -20dB/decade. This change in gain is caused by R1C1 & RFCF combinations. The value of fb should be selected such that

$f_a < f_b < f_c$

For good differentiation, the time period T of input signal is  $T \ge RFC1$ .

## **APPLICATIONS:**

In wave shaping circuits to detect high frequency components in input signal. As Rate of change detector in FM Modulator.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=-KxxD68sra0

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication Paul Horowitz and Winfield Hill, The Art of Electronics. 2nd ed. Cambridge University Press, Cambridge, 1989 ISBN 0-521-37095-7

A novel differential differentiator, M.A. Al-Alaoui, IEEE Transactions on Instrumentation and Measurement.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L 16

**MDE**

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: II - Characteristics of OP Amp and Applications

Date of Lecture:

| Topic of | Lecture: | Integrator |

|----------|----------|------------|

|----------|----------|------------|

#### Introduction :

A circuit in which the output voltage wave is the integral of the input voltage waveform is the **Integrator** or **Integration Amplifier.**

Replacing the feedback resistor Rf of the amplifier in the inverting mode by a capacitor.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Integrator

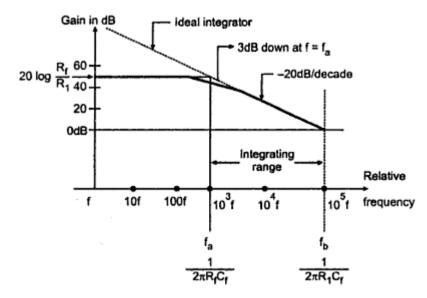

#### Integrator

A circuit in which the output voltage wave is the integral of the input voltage waveform is the **Integrator** or **Integration Amplifier.**

Op-amp integrator

## **Ideal Integrator**

The nodal equation at node A is,

$$\frac{V_{in} - V_A}{R_1} + C_F \frac{d(V_0 - V_A)}{dt} = 0$$

Since node A is at virtual ground,  $V_A = 0$

$$\Rightarrow \frac{V_{in}}{R_1} + C_F \frac{dV_0}{dt} = 0$$

$$\Rightarrow \frac{dV_0}{dt} = -\frac{1}{R_1 C_F} V_{in}$$

Integrating on both sides we get,

$$V_{0} = -\frac{1}{R_{1}C_{F}} \int_{0}^{t} V_{in}dt + C$$

(A)

Where, C is the integration constant. Thus the output voltage is directly proportional to negative integral of input voltage and inversely proportional to time constant  $R_1C_F$ .

In Op-amp integrator the effective input capacitance by Millers theorem is  $C_f$  (1-A<sub>v</sub>). Where,  $A_V \rightarrow$  gain of the Op - Amp

Gain  $A_V$  is infinite for ideal Op-Amp, so effective time of Op-amp becomes large which results in perfect integration.

The equation (A) written in phasor notation,

$$V_0(s) = -\frac{1}{sR_1C_F} V_{IN}(s)$$

In steady state,  $s = j\omega$

$$\rightarrow |A| = \left| \frac{V_0(s)}{V_{in}(s)} \right| = \left| \frac{-1}{SR_1C_F} \right| = \left| \frac{1}{-j\omega R_1C_F} \right|$$

$$\Rightarrow |A| = \frac{1}{\omega R_1C_F}$$

$$\therefore |A| = \frac{f_b}{f} \quad \text{where,}$$

$$f_b = \frac{1}{2\pi R_1C_F}$$

Where  $f_{b is}$  the frequency where gain is 0dB.

#### **Errors in ideal integrator**

- At low frequencies ( $\omega \approx -0$ ), the gain becomes infinite (saturates).

- Input offset voltage gets amplified and appears as error voltage which causes saturation.

- It is difficult to pull integrator out of saturation; hence perfect integration is not possible.

- Limited bandwidth.

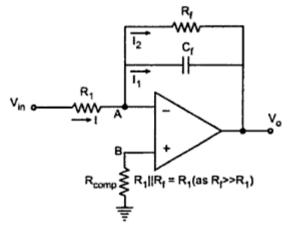

## Practical integrator

#### Practical integrator circuit

The demerits of ideal circuit are overcome by practical integrator circuit, in which feedback resistor  $R_F$  is connected across  $C_F$ . It reduces the low frequency gain of the Op-Amp. It is also called **Lossy Integrator.**

Nodal equation at node A gives,

$$\frac{V_{in}(s)}{R_1} + sC_F V_0(S) + \frac{V_0(s)}{R_F} = 0$$

$$\Rightarrow V_0(s) = -\left(\frac{1}{sR_1C_F + \frac{R_1}{R_F}}\right) V_{in}(s)$$

$$\Rightarrow \frac{V_0(s)}{V_{in}(s)} = -\frac{-R_F / R_1}{1 + sR_F C_F}$$

Put  $s = j\omega$ ,

$$\Rightarrow |A| = \left| \frac{V_0(j\omega)}{V_{in}(j\omega)} \right| = \left| \frac{-R_F / R_1}{1 + j\omega R_F C_F} \right| = \left| \frac{-R_F / R_1}{1 + j2\pi f R_F C_F} \right|$$

$$\therefore |A| = \frac{-R_F / R_1}{\left| 1 + j\frac{f}{fa} \right|}$$

Where,

$f_a = \frac{1}{2\pi R_F C_F}$ , is the break frequency at which gain is (0.707) R<sub>F</sub>/R<sub>1</sub>

#### Frequency response of the practical integrator

- The value of  $f_a$  is selected such that  $f_a < f_b$

- $f_b$ , the input frequency should be 10 times.  $f_a$ . i.e  $f_b = 10 f_a$ .

- For perfect integration, time period T of input signal should be,  $T \ge R_F C_{F.}$

## Applications:

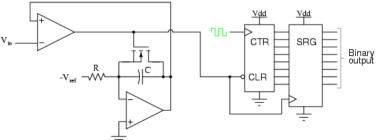

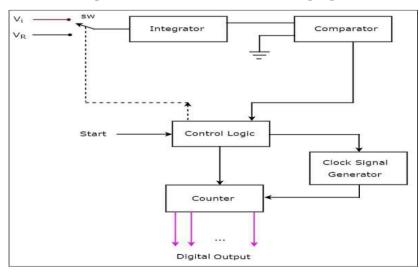

- 1. Analog computers, ADC's

- 2. Wave shaping circuits.

- 3. Ramp generators.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=vOOjcrbY0LQ

**Important Books/Journals for further learning including the page nos.:** Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication Wideband Differentiator and Integrator With Ideal Phase Response,Jayalaxmi Devate ; S. Y. Kulkarni ; K. R. Pai, IEEE Transactions on Instrumentation and Measurement.

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

**MDE**

II / IV

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

### : II - Characteristics of OP Amp and Applications

Date of Lecture:

Topic of Lecture: Instrumentation Amplifier

### Introduction :

A differential amplifier is a type of electronic amplifier that amplifies the difference between two input voltages but suppresses any voltage common to the two inputs.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Operational Amplifier, Differential Amplifier

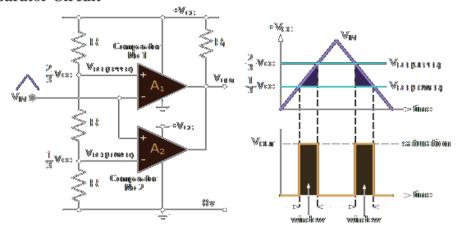

### **Instrumentation Amplifier**

1. It constructed using three Op-Amps as shown in Fig

2. Op-Amps A1 and A2 are connected basically, in noninverting amplifier configuration.

3. The only change is that instead of grounding inverting terminals of both Op-Amps as in noninverting configuration), they are connected to resistor RG

4. Effectively, the inverting terminals of Op-Amp A1 is fed a voltage Vl through RG and the inverting terminal of Op-Amp A2 is fed by a voltage V2 through RG. This is obvious by virtual ground concept. Derivation for Output Voltage

As per the superposition theorem, the output of A1 (Vo') and A2 (Vo'') is given below

$$\mathbf{V}_{o}' = \left(1 + \frac{\mathbf{R}_{2}}{\mathbf{R}_{G}}\right) \mathbf{V}_{1} - \frac{\mathbf{R}_{2}}{\mathbf{R}_{G}} \mathbf{V}_{2}$$

$$\mathbf{V}_{o}'' = \left(1 + \frac{\mathbf{R}_{2}}{\mathbf{R}_{G}}\right) \mathbf{V}_{2} - \frac{\mathbf{R}_{2}}{\mathbf{R}_{G}} \mathbf{V}_{1}$$

The output of two op-amps (A1 and A2) are applied to the input of differential amplifier. Therefore, the final output of the instrumentation amplifier is written as follows

Output

$$\mathbf{V}_{o} = \frac{\mathbf{R}_{f}}{\mathbf{R}_{1}} (\mathbf{V}_{o}'' - \mathbf{V}_{o}')$$

$$V_{o} = \frac{R_{f}}{R_{1}} \left( \left( \left( 1 + \frac{R_{2}}{R_{G}} \right) V_{2} - \frac{R_{2}}{R_{G}} V_{1} \right) - \left( 1 + \frac{R_{2}}{R_{G}} \right) V_{1} + \frac{R_{2}}{R_{G}} V_{2} \right)$$

$$= \frac{R_{f}}{R_{1}} \left( \left( \left( 1 + \frac{R_{2}}{R_{G}} \right) (V_{2} - V_{1}) + \frac{R_{2}}{R_{G}} (V_{2} - V_{1}) \right) \right)$$

$$= \frac{R_{f}}{R_{1}} (V_{2} - V_{1}) \left( \left( 1 + \frac{R_{2}}{R_{G}} \right) + \frac{R_{2}}{R_{G}} \right)$$

Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=-KxxD68sra0

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication Paul Horowitz and Winfield Hill, <u>The Art of Electronics</u>. 2nd ed. Cambridge University Press, Cambridge, 1989 <u>ISBN 0-521-37095-7</u>

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L 18

**MDE**

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

#### Unit

### : II - Characteristics of OP Amp and Applications

Date of Lecture:

Topic of Lecture: Precision rectifier, V/I & I/V Converter

### **Introduction :**

The precision rectifier, also known as a super diode, is a configuration obtained with an operational amplifier in order to have a circuit behave like an ideal diode and rectifier. It is very useful for high-precision signal processing.

The circuits in instrumentation for analog representation of certain physical quantities (weight, pressure, motion etc), DC current is preferred.

This is because DC current signals will be constant throughout the circuit in series from the source to the load.

The current sensing instruments also have the advantage of less noise. So, sometimes it is essential to create current which is corresponding or proportional to a definite voltage. For this purpose Voltage to Current Converters are used.

**Prerequisite knowledge for Complete understanding and learning of Topic:** Precision rectifier, Voltage to current convertor, current to voltage convertor

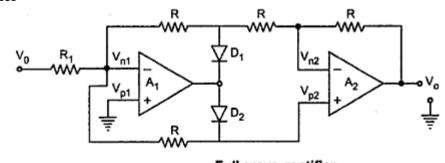

**Precision rectifier**

Full wave rectifier

- Full Wave rectifier accepts a.c input signal, inverts either positive or negative half and delivers both the inverted and non-inverted halves at the output.

- For positive inputs (V<sub>i</sub> > 0), diode D<sub>1</sub> is ON and D<sub>2</sub> is OFF. Both the Op-amps A<sub>1</sub>and A<sub>2</sub> acts as inverters. So the output is V<sub>0</sub> = V<sub>i</sub>.

Equivalent ckt. For  $V_i > 0$ .

• Hence output voltage, V<sub>0</sub> is given as,

$$v_{0} = \left(1 + \frac{R}{2R}\right)\left(\frac{-2}{3}v_{i}\right) = -v_{i}$$

$$\Rightarrow v_{0} = -v_{i}$$

(A)

• So for negative input, the output is positive.

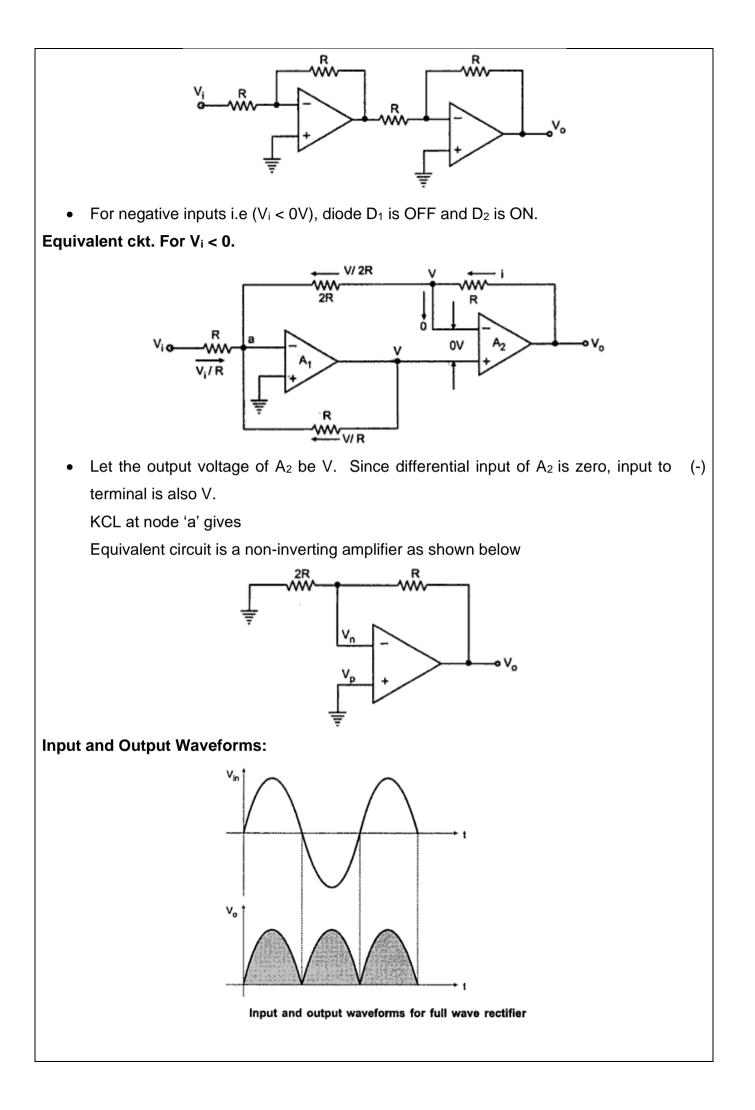

### V to I Converter

- The voltage to current converter is a circuit the output load current is proportional to the input voltage.

- According to connection of load, there are two types,

i. Floating load. ii. Grounded load.

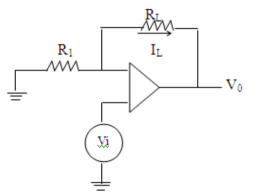

## Floating Load V-I Converter

• As the input current to an Op-Amp is zero,

$$I_{L} = I_{i} = \frac{V_{i}}{R_{1}}$$

$$\Rightarrow I_{L} \alpha V_{i}$$

- Thus the load current is proportional to input voltage and the circuit acts as a voltage to current converter.

- If the load is a capacitor, it charges and discharges at a constant rate. Such converters are used to generate Saw tooth or triangular waveforms.

- The proportionality constant is generally 1/R<sub>1</sub>. Hence the circuit is called Transconductance amplifier. It is also called voltage controlled current source. (VCCS).

- The load current, I<sub>L</sub>= V<sub>i</sub>/R<sub>1</sub> is same for all types of loads. Load can be linear (e.g Resistor), or non-linear (e.g LED) or it can have time dependent.

- No matter what the load is, the Op-amp will draw the current I<sub>i</sub> whose magnitude depends only Vi and R.

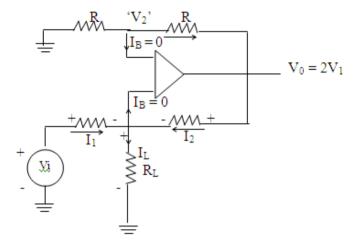

### Grounded Load V – I Converter:

- When one end of the load is grounded, it is called grounded V-I converter. The circuit is also called as HOWLAND CURRENT CONVERTER.

- Applying KCL at node, V<sub>1</sub>

$$I_1 + I_2 = I_L$$

$$\Rightarrow \frac{V_i - V_1}{R} + \frac{V_0 - V_1}{R} = I_L$$

$$\Rightarrow V_i + V_0 - 2V_1 = I_L.R$$

$$\therefore V_i = \frac{V_i + V_0 - I_L R}{2}$$

(1)

The gain of an Op-Amp in non- inverting mode is given as,

$$A_{CL} = 1 + \frac{R_F}{R_1}$$

------ (2)

For this circuit,  $R_f = R_1 = R$ ,

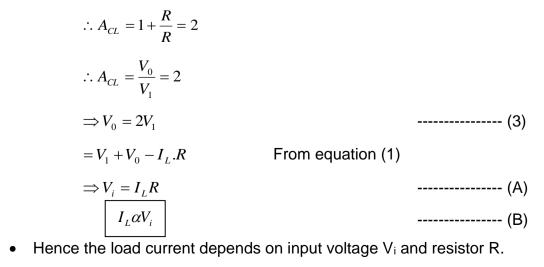

I to V Converter

The circuit in which the output voltage is proportional to input current is called current to voltage converter. Consider, input current Ii and output voltage V<sub>0</sub>, then

$$V_0 = A I_i \tag{1}$$

Where,  $A \rightarrow Gain of the circuit.$

- As we measure gain in ohms it is appropriate to denote gain by R. Hence I-V converter is also called as Transresistance amplifier.

- Node B is grounded. Hence node A is at virtual ground.

$$\therefore V_A = 0$$

$$\Rightarrow I_i = \frac{V_A - V_0}{R} = \frac{-V_0}{R}$$

$$\Rightarrow V_0 - R.I_i$$

$$\Rightarrow V_0 \alpha R.I_i$$

- Here the output voltage (V<sub>0</sub>) is proportional to input current (I<sub>i</sub>), therefore the circuit is a current to voltage converter.

- The circuit is also called as current controlled voltage source [CCVS].

- It the resistance in the circuit is replaced with impedance Z, the circuit is called Trans impedance Amplifier.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=5HweBajP-5g

Important Books/Journals for further learning including the page nos.: Linear Integrated Circuits Sixth Edition Ganesh Babu T.R,Suseela B,SCITECH Publication New precision rectifier circuits with high accuracy and wide bandwidth,S. J. G. Gift ,Pages 601-617 | Received 16 Sep 2003, Accepted 30 Mar 2005, Published online: 19 Aug 2006

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

MDE

II / IV

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

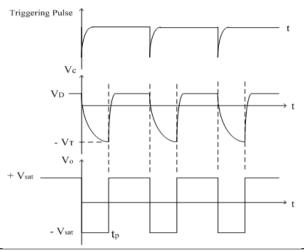

: III - Comparator and Waveform Generators

Date of Lecture:

Topic of Lecture: Comparators, open loop Op Amp configuration

### **Introduction :**

A **comparator** is an electronic circuit, which compares the two inputs that are applied to it and produces an output. The output value of the comparator indicates which of the inputs is greater or lesser. Please note that comparator falls under non-linear applications of ICs.

### Prerequisite knowledge for Complete understanding and learning of Topic:

Operation of Op Amp, Basic Analog electronics and Electronic Devices, and Circuit theory

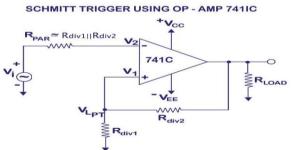

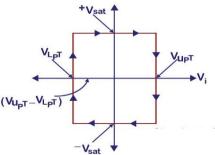

#### Comparators, open loop Op Amp configuration:

A **comparator** is an electronic circuit, which compares the two inputs that are applied to it and produces an output. The output value of the comparator indicates which of the inputs is greater or lesser. Please note that comparator falls under non-linear applications of ICs.

An op-amp consists of two input terminals and hence an op-amp based comparator compares the two inputs that are applied to it and produces the result of comparison as the output. This chapter discusses about **op-amp based comparators**.

Types of Comparators

Comparators are of two types : **Inverting** and **Non-inverting**. This section discusses about these two types in detail.

Inverting Comparator

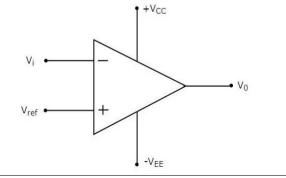

An **inverting comparator** is an op-amp based comparator for which a reference voltage is applied to its non-inverting terminal and the input voltage is applied to its inverting terminal. This comparator is called as **inverting** comparator because the input voltage, which has to be compared is applied to the inverting terminal of op-amp.

The circuit diagram of an inverting comparator is shown in the following figure.

The **operation** of an inverting comparator is very simple. It produces one of the two values, +Vsat+Vsat and -Vsat-Vsat at the output based on the values of its input voltage ViVi and

the reference voltage VrefVref.

- The output value of an inverting comparator will be -Vsat-Vsat, for which the input ViVi voltage is greater than the reference voltage VrefVref.

- The output value of an inverting comparator will be +Vsat+Vsat, for which the input ViVi is less than the reference voltage VrefVref.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=fWN17g-JGro

Important Books/Journals for further learning including the page nos.:

Linear Integrated Circuits By D. Roy Choudhury, Shail B. Jain T1

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**LECTURE HANDOUTS**

L 20

II / IV

MDE

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: III - Comparator and Waveform Generators

Date of Lecture:

Topic of Lecture: Inverting, Non-inverting Comparators

#### **Introduction :**

A **comparator** is an electronic circuit, which compares the two inputs that are applied to it and produces an output. The output value of the comparator indicates which of the inputs is greater or lesser. Please note that comparator falls under non-linear applications of ICs.

### Prerequisite knowledge for Complete understanding and learning of Topic:

Operation of Op Amp, Basic Analog electronics and Electronic Devices, and Circuit theory

### Inverting, Non-inverting Comparators

Types of Comparators

Comparators are of two types : **Inverting** and **Non-inverting**. This section discusses about these two types in detail.

Inverting Comparator

An **inverting comparator** is an op-amp based comparator for which a reference voltage is applied to its non-inverting terminal and the input voltage is applied to its inverting terminal. This comparator is called as **inverting** comparator because the input voltage, which has to be compared is applied to the inverting terminal of op-amp.

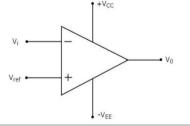

The circuit diagram of an inverting comparator is shown in the following figure.

The **operation** of an inverting comparator is very simple. It produces one of the two values, +Vsat+Vsat and -Vsat-Vsat at the output based on the values of its input voltage ViVi and the reference voltage VrefVref.

- The output value of an inverting comparator will be -Vsat-Vsat, for which the input ViVi voltage is greater than the reference voltage VrefVref.

- The output value of an inverting comparator will be +Vsat+Vsat, for which the input ViVi is less than the reference voltage VrefVref.

The operation of the inverting comparator shown above is discussed below –

- During the **positive half cycle** of the sinusoidal input signal, the voltage present at the inverting terminal of op-amp is greater than zero volts. Hence, the output value of the inverting comparator will be equal to -Vsat-Vsat during positive half cycle of the sinusoidal input signal.

- Similarly, during the **negative half cycle** of the sinusoidal input signal, the voltage present at the inverting terminal of the op-amp is less than zero volts. Hence, the output value of the inverting comparator will be equal to +Vsat+Vsat during negative half cycle of the sinusoidal input signal.

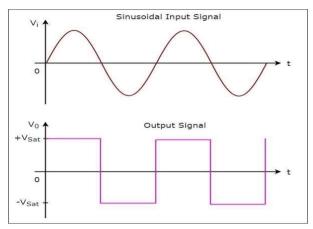

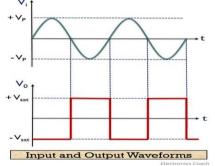

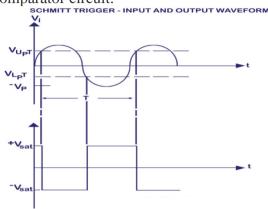

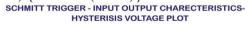

The following figure shows the **input and output waveforms** of an inverting comparator, when the reference voltage is zero volts.

observe the In the figure shown above, we can that output transitions either from -Vsat-Vsat to +Vsat+Vsat or from +Vsat+Vsat to -Vsat-Vsat whenever the sinusoidal input signal is crossing zero volts. In other words, output changes its value when the input is crossing zero volts. Hence, the above circuit is also called as **inverting zero crossing detector**.

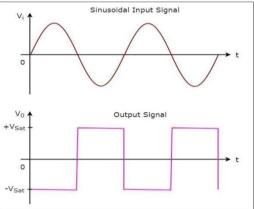

#### **Non-Inverting Comparator**

A non-inverting comparator is an op-amp based comparator for which a reference voltage is applied to its inverting terminal and the input voltage is applied to its non-inverting terminal. This op-amp based comparator is called as **non-inverting** comparator because the input voltage, which has to be compared is applied to the non-inverting terminal of the op-amp.

The circuit diagram of a non-inverting comparator is shown in the following figure

The **operation** of a non-inverting comparator is very simple. It produces one of the two values, +Vsat+Vsat and -Vsat-Vsat at the output based on the values of input voltage VtVt and the reference voltage +Vref+Vref.

- The output value of a non-inverting comparator will be +Vsat+Vsat, for which the input voltage ViVi is greater than the reference voltage +Vref+Vref.

- The output value of a non-inverting comparator will bee –Vsat–Vsat, for which the input voltage ViVi is less than the reference voltage +Vref+Vref.

The operation of a non-inverting comparator is explained below –

- During the **positive half cycle** of the sinusoidal input signal, the voltage present at the noninverting terminal of op-amp is greater than zero volts. Hence, the output value of a noninverting comparator will be equal to +Vsat+Vsat during the positive half cycle of the sinusoidal input signal.

- Similarly, during the **negative half cycle** of the sinusoidal input signal, the voltage present at the non-inverting terminal of op-amp is less than zero volts. Hence, the output value of non-

inverting comparator will be equal to -Vsat-Vsat during the negative half cycle of the sinusoidal input signal.

The following figure shows the **input and output waveforms** of a non-inverting comparator, when the reference voltage is zero volts.

From the figure shown above, we can observe that the output transitions either from +Vsat+Vsat to -Vsat-Vsat or from -Vsat-Vsat to +Vsat+Vsat whenever the sinusoidal input signal crosses zero volts. That means, the output changes its value when the input is crossing zero volts. Hence, the above circuit is also called as **non-inverting zero crossing detector**.

Video Content / Details of website for further learning (if any): https://www.youtube.com/watch?v=cfO8PDgsrN8

Important Books/Journals for further learning including the page nos.: Linear Integrated Circuits By D. Roy Choudhury, Shail B. Jain T1

**Course Faculty**

**MDE**

# **MUTHAYAMMAL ENGINEERING COLLEGE**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

## **LECTURE HANDOUTS**

L 21

II / IV

Course Name with Code : 19MDC04 - LOGIC CIRCUITS FOR CLINICAL ENGINEERS

Course Faculty : Mrs.M.Birunda

Unit

: III - Comparator and Waveform Generators

Date of Lecture:

Topic of Lecture: Applications of comparator

### **Introduction :**

A **comparator** is an electronic circuit, which compares the two inputs that are applied to it and produces an output. The output value of the comparator indicates which of the inputs is greater or lesser. Please note that comparator falls under non-linear applications of ICs.

Prerequisite knowledge for Complete understanding and learning of Topic: Operation of Op Amp, Basic Analog electronics and Electronic Devices, and Circuit theory

### **Applications of comparator:**

### **Zero Crossing Detector**

**Definition**: An op-amp detector that has the ability to detect the change from positive to negative or negative to a positive level of a sinusoidal waveform is known as a zero crossing detector. More specifically, we can say that it detects the zero crossing of the applied ac signal.

It is basically a voltage comparator whose output changes when the input signal crosses the zero of the reference voltage level. Thus it is named so.

It is also known to be a **square wave generator** as the applied input signal is converted into a square wave by the zero crossing detector.

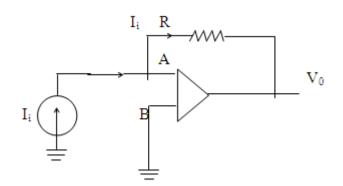

Circuit Diagram of Zero Crossing Detector

The figure below represents the circuit of a zero crossing detector using inverting op-amp:

$R_{1} = 0$   $V_{ref} = 0$   $V_{i}$   $V_{ref} = 0$   $V_{i}$

Here, the input signal V<sub>i</sub> is provided to the inverting terminal of the op-amp while the non-inverting

terminal is grounded by making use of two resistors  $R_1$  and  $R_2$ .

As we can see that analog input signal is provided at the inverting terminal of the op-amp. Thus, the waveform of the signal at the output will hold reverse polarity. This we will discuss under working of the detector.

Working of Zero Crossing Detector

As we have already discussed that it detects the point where the input signal crosses zero of the reference voltage level. For every crossing, the saturation level of the output signal changes from one to another.

As we have already mentioned that the reference level is set at 0 and applied at the non-inverting terminal of the op-amp. The sine wave applied at the inverting terminal of the op-amp is compared with the reference level each time the phase of the wave changes either from positive to negative or negative to positive.

Firstly, when positive half of the sinusoidal signal appears at the input. Then the op-amp comparator compares the reference voltage level with the peak level of the applied signal

$$V_0 = V_{ref} - V_i$$

And we know the reference level is 0, thus

$$V_0 = 0 - (+ V_{sat})$$

So, we will have

$V_0 = - V_{sat}$

Secondly, in case of the negative half of the sinusoidal signal, the op-amp comparator again compares the reference voltage level with the peak of the applied signal.

As this time the circuit is dealing with negative half of the signal, thus the peak will have a negative polarity.

$$V_0 = V_{ref} - V_i$$

Thus,

$$V_0 = 0 - (-V_{sat})$$

So, we get

$$V_0 = + V_{sat}$$

In this way, the zero crossing detector detects the change in the level of the applied signal. Input and Output Waveform

From the beginning, we are mentioning that a zero crossing detector is also known to be a square wave generator. As the output of the window comparator is nothing but a square wave.

Let us now have a look at the input and output waveform of a zero crossing detector:

Applications of Zero Crossing Detector

Zero crossing detectors widely find applications in electronics circuits mainly for switching purpose and in phase locked loop. Also, these are used in frequency counters and in phase meters.

It can also be used as phase meters, as it can be used to measure the phase angle between two voltage applied at its terminals.

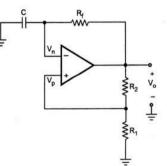

## Window Comparator