(An Autonomous Institution)

**L1**

#### LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

**Course Faculty** : Mrs. P.Subhasundari

**Date of Lecture:** 18.8.2021 Unit : I - INTRODUCTION TO 80X86 PROCESSORS

**Topic of Lecture:** 16/32bit processor 80x86

#### Introduction:

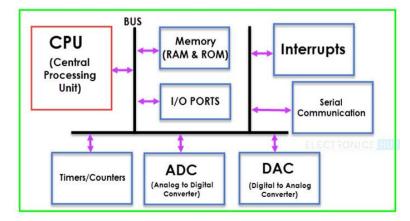

A microprocessor is an electronic component that is used by a computer to do its work. It is a central processing unit on a single integrated circuit chip containing millions of very small components including transistors, resistors, and diodes that work together.

# Prerequisite knowledge for Complete understanding and learning of Topic:

Basics of Digital circuits

#### **Detailed content of the Lecture:**

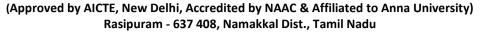

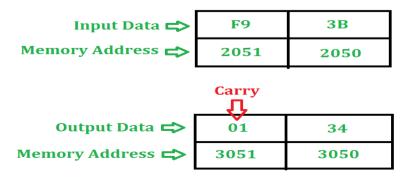

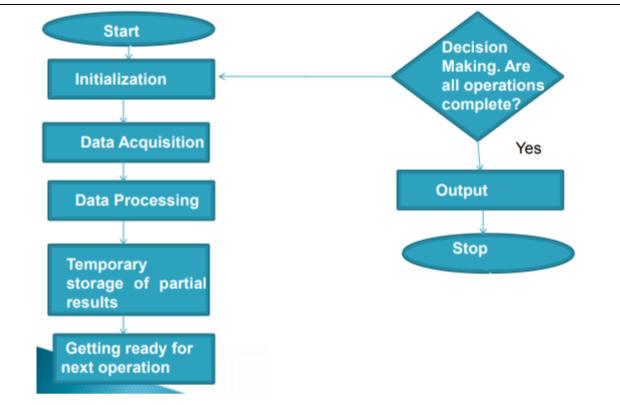

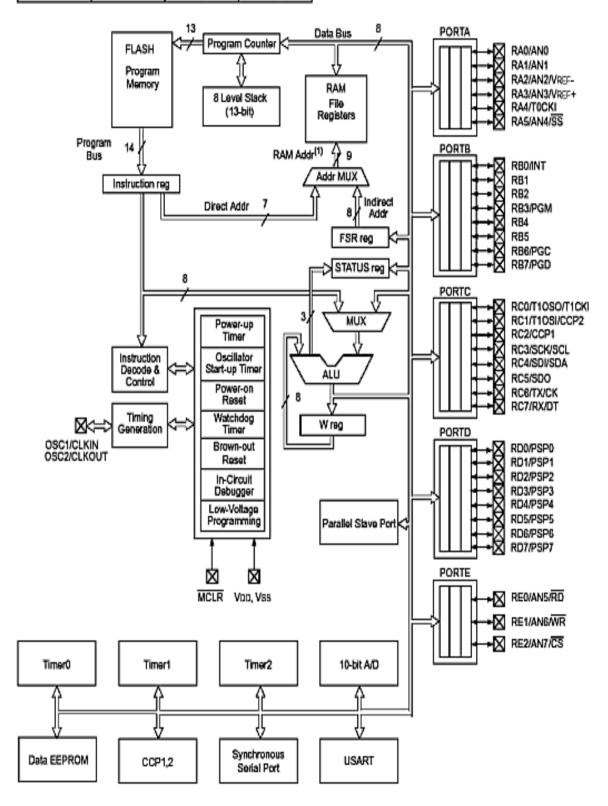

A typical Microprocessor structure looks like this.

### **Clock Speed of different Microprocessor:**

#### **16-bit Microprocessor**

- 8086: 4.7MHz, 8MHz, 10MHz

- 8088: more than 5MHz

- 80186/80188: 6MHz

### 32-bit Microprocessor

- INTEL 80386: 16MHz to 33MHz

- INTEL 80486: 16MHz to 100MHz

It does not have any 128-bit Microprocessor in work at present one among the reasons for this is that we are a long way from exhausting the 64 bit address space itself, we use it a constant rate of roughly 2 bits every 3 years. At present we have only used 48 bits of 64 bits so why require 128 bit address space. Also 128 bit Microprocessor would be much slower than the 64 bit Microprocessor.

### **Types of Processor:**

### Complex Instruction Set Computer (CISC) -

CISC or Complex Instruction Set Computer is a computer architecture where instructions are such that a single instruction can execute multiple low level operations like loading from memory, storing into memory or an arithmetic operation etc. It has multiple addressing nodes within single instruction. CISC makes use of very few registers.

#### Example:

- Intel 386

- Intel 486

- Pentium

- Pentium Pro

- Pentium II

- Pentium III

- Motorola 68000

- Motorola 68020

- Motorola 68040 etc.

# Reduced Instruction Set Computer (RISC)

RISC or Reduced Instruction Set Computer is a computer architecture where instruction are simple and designed to get executed quickly. Instructions get completed in one clock cycle this is because of the optimization of instructions and pipelining(a technique that allows for simultaneous execution of parts, or stages, of instructions to more efficiently process instructions). RISC makes use of multiple registers to avoid large interactions with memory. It has few addressing nodes.

#### **Example:**

- IBM RS6000

- MC88100

- DEC Alpha 21064

- DEC Alpha 21164

# > Explicitly Parallel Instruction Computing (EPIC)

EPIC or Explicitly Parallel Instruction Computing permits computer to execute instructions parallel using compilers. It allows complex instructions execution without using higher clock frequencies. EPIC encodes its instruction into 128 bit bundles. Each bundle contains three instructions which are encoded in 41 bits each and a 5-bit template field (contains information about types of instructions in bundle and which instructions can be executed in parallel).

# Video Content / Details of website for further learning (if any):

www.youtube.com/watch?v=liRPtvj7bFU&noredirect=1

# Important Books/Journals for further learning including the page nos.:

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (4-10)

**Course Faculty**

(An Autonomous Institution)

**L2**

#### LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : I - INTRODUCTION TO 80X86 PROCESSORS Date of Lecture: 20.08.2021

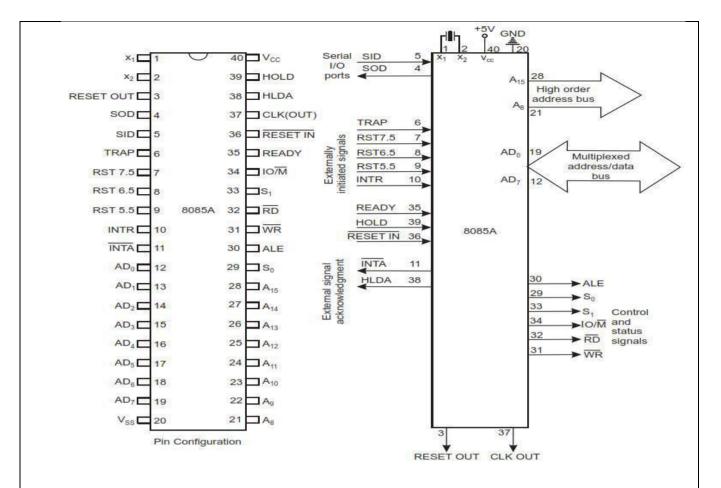

**Topic of Lecture:** , 80386 Features and Architecture, Pin Description, Functional Description, Architecture of 8085 Microprocessor

#### **Introduction:**

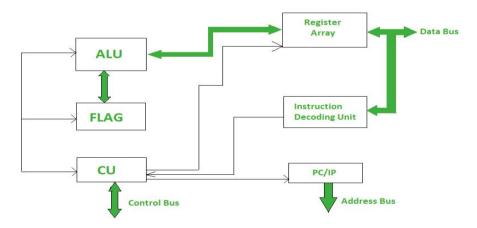

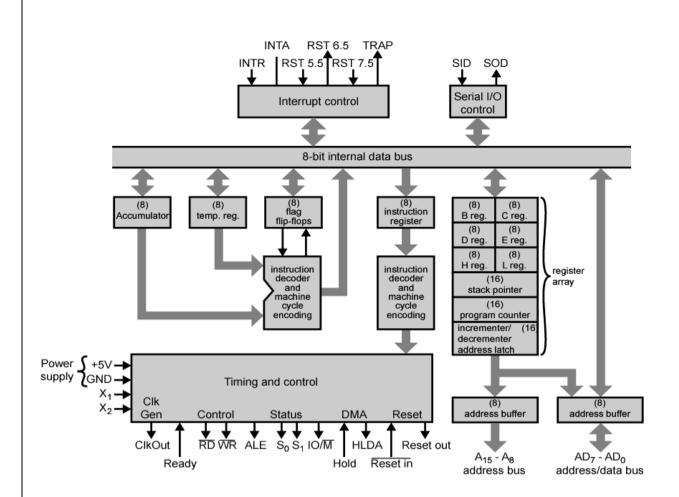

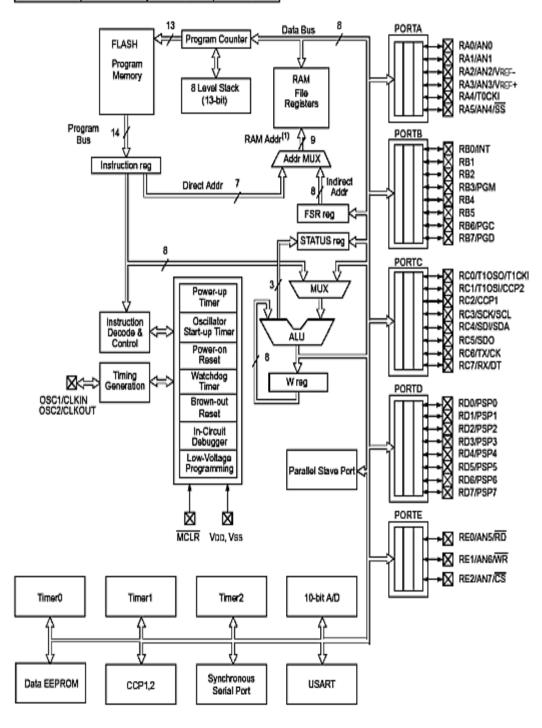

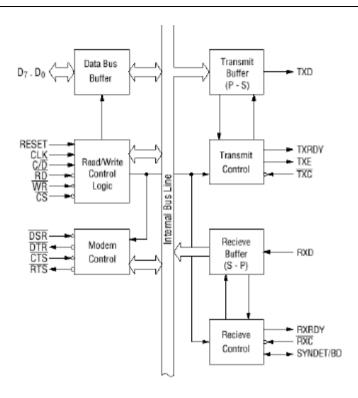

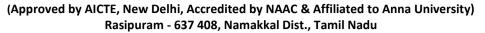

The architecture of 8085 microprocessor mainly includes the timing & control unit, Arithmetic and logic unit, decoder, instruction register; interrupt control, a register array, serial input/output control. The most important part of the **microprocessor** is the central processing unit.

# Prerequisite knowledge for Complete understanding and learning of Topic:

- Processors and controllers

- Central processing unit

- Memory Devices

# Detailed content of the Lecture:

#### 8085 MICROPROCESSOR ARCHITECTURE

- 8-bit processor available as a 40-pin IC package

- It uses +5 V for power.

- It can run at a maximum frequency of 3 MHz. Its data bus width is 8-bit and address bus width is 16-bitthus it can address  $2^{16} = 64$  KB of memory.

#### Arithmetic and Logic Unit

- The ALU performs the actual numerical and logical operations such as Addition (ADD), Subtraction (SUB), AND, OR etc.

- It uses data from memory and from Accumulator to perform operations.

- The results of the arithmetic and logical operations are stored in the accumulator.

# **Registers**

- The 8085 includes six registers, one accumulator and one flag register, as shown in Figure. In addition, it has two 16-bit registers: stack pointer and program counter.

- The 8085 has six general-purpose registers to store 8-bit data; these are identified as B, C, D, E, H and L. they can be combined as register pairs BC, DE and HL to perform.

#### Accumulator

- The accumulator is an 8-bit register that is a part of ALU.

- This register is used to store 8-bit data and to perform arithmetic and logical operations.

- The result of an operation is stored in the accumulator.

- The accumulator is also identified as register A.

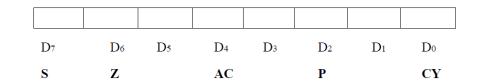

### Flag register

- The ALU includes five flip-flops, which are set or reset after an operation according to data condition of the result in the accumulator and other registers.

- They are called Zero (Z), Carry (CY), Sign (S), Parity (P) and Auxiliary Carry (AC) flags.

- Their bit positions in the flag register are shown in Figure. The microprocessor uses these flags to test data conditions.

Flag register

### **Program Counter (PC)**

- This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer.

- The microprocessor uses this register to sequence the execution of the instructions.

- The function of the program counter is to point to the memory address from which the next byte is to be fetched.

- When a byte is being fetched, the program counter is automatically incremented by one to point to the next memory location.

#### Stack Pointer (SP)

- The stack pointer is also a 16-bit register, used as a memory pointer.

- It points to a memory location in R/W memory, called stack.

- The beginning of the stack is defined by loading 16- bit address in the stack pointer.

# **Instruction Register/Decoder**

- It is an 8-bit register that temporarily stores the current instruction of a program.

- Latest instruction sent here from memory prior to execution.

- Decoder then takes instruction and decodes or interprets the instruction.

#### Control Unit

• Generates signals on data bus, address bus and control bus within microprocessor to carry out the instruction, which has been decoded.

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=\_qtCAuLIaew

# Important Books/Journals for further learning including the page nos.:

➤ Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (24-30)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University)

Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

### LECTURE HANDOUTS

L3

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : I - INTRODUCTION TO 80X86 PROCESSORS Date of Lecture: 23.08.2021

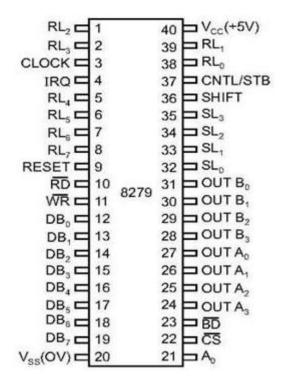

Topic of Lecture: Register Set, 80386 Real mode, Pin Diagram

#### Introduction:

The 40 pins of the microprocessor can be divided into six groups such as address bus, data bus, control signals & status signals; power supply & frequency, externally started signals and serial input/output ports.

# Prerequisite knowledge for Complete understanding and learning of Topic:

Basics of digital electronics

#### **Detailed content of the Lecture:**

#### **Timing and Control Unit**

✓ The timing and control unit accepts information from the instruction decoder andgenerates different control signal. This unit synchronizes all the microprocessor operation and generates control and status signal necessary for communication between the microprocessor and peripherals.

#### A8 - A15 (Output 3 State):

✓ Address Bus: The most significant 8 bits of the memory address or the 8 bits of the I/O address,3 stated during Hold and Halt modes.

# AD0 - AD7 (Input / Output 3 state):

- ➤ Multiplexed Address/Data Bus; Lower 8 bits of the memory address (or I/0 address) appear on the bus during the first clock cycle of a machine state.

- ➤ It then becomes the data bus during the second and third clock cycles. 3 stated during Hold and Halt modes.

# ALE (Output):

- ➤ Address Latch Enable: It occurs during the first clock cycle of a machine state and enables the address to get latched into the on chip latch of peripherals.

- ➤ The falling edge of ALE is set to guarantee setup and hold times for the address information. ALE can also be used to strobe the status information. ALE is never 3stated.

#### SO, S1 (Output):

Data Bus Status. Encoded

status of the bus cycle:

S1 S0

00 HALT

0 1 WRITE

10 READ

1 1 FETCH S1 can be used as an advanced R/W status.

#### RD (Output 3state):

READ: indicates the selected memory or I/0 device is to be read and that the Data Bus is available for the data transfer.

#### WR (Output 3state):

- ➤ WRITE: indicates the data on the Data Bus is to be written into the selected memory or I/Olocation.

- ➤ Data is set up at the trailing edge of WR. 3stated during Hold and Halt modes.

### **READY** (Input):

- ➤ If Ready is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data.

- ➤ If Ready is low, the CPU will wait for Ready to go high before completing the read or write cycle.

### **HOLD** (Input):

- ➤ HOLD: indicates that another Master is requesting the use of the Address and Data Buses.

- ➤ The CPU, upon receiving the Hold request will relinquish the use of buses as soon as the completion of the current machine cycle.

- ➤ Internal processing can continue. The processor can regain the buses only after the Hold is removed. When the Hold is acknowledged, the Address, Data, RD, WR, and IO/M lines are 3stated.

### HLDA (Output):

- ➤ HOLD ACKNOWLEDGE: indicates that the CPU has received the Hold request and that it will relinquish the buses in the next clock cycle.

- ➤ HLDA goes low after the Hold request is removed. The CPU takes the buses one half clock cycle after HLDA goes low.

#### INTR (Input):

- ➤ INTERRUPT REQUEST is used as a general purpose interrupt. It is sampled only during the next to the last clock cycle of the instruction. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued.

- ➤ During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted.

#### INTA (Output):

- ➤ INTERRUPT ACKNOWLEDGE: is used instead of (and has the same timing as) RD during the Instruction cycle after an INTR is accepted.

- ➤ It can be used to activate the 8259 Interrupt chip or some other interrupt port.

#### **RESTART INTERRUPTS:**

These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted.

RST 7.5 Highest Priority

RST 6.5

**RST 5.5 Lowest Priority**

### **RESET IN (Input):**

- ➤ Reset sets the Program Counter to zero and resets the Interrupt Enable and HLDA flipflops.

- ➤ None of the other flags or registers (except the instruction register) are affected The CPU is held in the reset condition as long as Reset is applied.

### **RESET OUT (Output):**

✓ Indicates CPIJ is being reset. Can be used as a system RESET. The signal is synchronized to the processor clock.

# X1, X2 (Input):

Crystal or R/C network connections to set the internal clock generator X1 can also be an external clock input instead of a crystal. The input frequency is divided by 2 to give the internal operating frequency.

### CLK (Output):

Clock Output for use as a system clock when a crystal or R/ C network is used as an input to the CPU. The period of CLK is twice the X1, X2 input period.

### IO/M (Output):

IO/M indicates whether the Read/Write is to memory or I/O Tristated during Hold and Halt modes.

#### SID (Input):

Serial input data line The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

#### SOD (output):

Serial output data line. The output SOD is set or reset as specified by the SIM instruction.

Vcc: +5 volt supply.

Vss: Ground Reference.

### Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=ii7PCV2zvms

### Important Books/Journals for further learning including the page nos.:

➤ Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (24-30)

**Course Faculty**

(An Autonomous Institution)

L4

### LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : I - INTRODUCTION TO 80X86 PROCESSORS Date of Lecture: 24.08.2021

Topic of Lecture: Instruction Set, Segmentation, Bus Cycles Initialization

#### **Introduction:**

- ➤ An instruction of a computer is a command given to the computer to perform a specified operation on given data.

- ➤ In microprocessor, the instruction set is the collection of the instructions that the microprocessor is designed to execute.

### Prerequisite knowledge for Complete understanding and learning of Topic:

Digital Concepts

# **Detailed content of the Lecture:**

### **DATA TRANSFER GROUP:**

| DATA TRANSFER GROUP: |                           |                                                     |                                |  |  |

|----------------------|---------------------------|-----------------------------------------------------|--------------------------------|--|--|

| Opcode               | Operand                   | Meaning                                             | Example                        |  |  |

| MOV                  | Rd, Sc<br>M, Sc<br>Dt, M  | Copy from the source (Sc) to the destination(Dt)    | Example – MOV K, L             |  |  |

| MVI                  | Rd, data<br>M, data       | Move immediate 8-bit                                | Example – MVI K, 55L           |  |  |

| LDA                  | 16-bit address            | Load the accumulator                                | Example – LDA 2034K            |  |  |

| LDAX                 | B/D Reg. pair             | Load the accumulator indirect                       | Example – LDAX K               |  |  |

| LXI                  | Reg. pair, 16-bit<br>data | Load the register pair immediate                    | Example – LXI K,<br>3225L      |  |  |

| LHLD                 | 16-bit address            | Load H and L registers direct                       | <b>Example</b> – LHLD<br>3225K |  |  |

| STA                  | 16-bit address            | 16-bit address                                      | Example – STA 325K             |  |  |

| STAX                 | 16-bit address            | Store the accumulator indirect <b>Example</b> – STA |                                |  |  |

| SHLD | 16-bit address        | Store H and L registers direct                                   | <b>Example</b> – SHLD<br>3225K |

|------|-----------------------|------------------------------------------------------------------|--------------------------------|

| XCHG | None                  | Exchange H and L with D and E                                    | Example – XCHG                 |

| SPHL | None                  | Copy H and L registers to the stack pointer                      | Example – SPHL                 |

| XTHL | None                  | Exchange H and L with top of stack                               | Example – XTHL                 |

| PUSH | Reg. pair             | Push the register pair onto the stack                            | Example – PUSH K               |

| POP  | Reg. pair             | Pop off stack to the register pair                               | the <b>Example</b> – POPK      |

| OUT  | 8-bit port<br>address | Output the data from the accumulator to a port with 8bit address | Example – OUT K9L              |

| IN   | 8-bit port<br>address | Input data to accumulator from a port with 8-bit address         | Example – IN5KL                |

# **CONTROL INSTRUCTIONS:**

| Opcode | Operand | Meaning                      | Explanation                                                                                                                                     |

|--------|---------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP    | None    | No operation                 | No operation is performed, i.e., the instruction is fetched and decoded.                                                                        |

| HLT    | None    | Halt and enter<br>wait state | The CPU finishes executing the current instruction and stops further execution. An interrupt or reset is necessary to exit from the halt state. |

| DI     | None    | Disable<br>interrupts        | The interrupt enable flip-flop is reset and all the interrupts are disabled except TRAP.                                                        |

| EI     | None    | Enable<br>interrupts         | The interrupt enable flip-flop is set and all the interrupts are enabled.                                                                       |

| RIM    | None    | Read<br>interrupt<br>mask    | This instruction is used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit.                                         |

| SIM    | None    | Set interrupt<br>mask        | This instruction is used to implement the interrupts 7.5, 6.5, 5.5, and serial data output.                                                     |

# LOGICAL INSTRUCTIONS:

| Opco<br>de | Operand       | Meaning                                              | Explanation                                                                                                                                                                                       |

|------------|---------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СМР        | R<br>M        | Compare the register or memory with the accumulator  | The contents of the operand (register or memory) are M compared with the contents of the accumulator.                                                                                             |

| СРІ        | 8-bit<br>data | Compare immediate with the accumulator               | The second byte data is compared with the contents of the accumulator.                                                                                                                            |

| ANA        | R<br>M        | Logical AND register or memory with the accumulator  | The contents of the accumulator are logically AND with M the contents of the register or memory, and the result is placed in the accumulator.                                                     |

| ANI        | 8-bit<br>data | Logical AND immediate with the accumulator           | The contents of the accumulator are logically AND with the 8-bit data and the result is placed in the accumulator.                                                                                |

| XRA        | R<br>M        | Exclusive OR register or memory with the accumulator | The contents of the accumulator are Exclusive OR with M the contents of the register or memory, and the result is placed in the accumulator.                                                      |

| XRI        | 8-bit<br>data | Exclusive OR immediate with the accumulator          | The contents of the accumulator are Exclusive OR with the 8-bit data and the result is placed in the accumulator.                                                                                 |

| ORA        | R<br>M        | Logical OR register or memory with the accumulator   | The contents of the accumulator are logically OR with M the contents of the register or memory, and result is placed in the accumulator.                                                          |

| ORI        | 8-bit<br>data | Logical OR immediate with the accumulator            | The contents of the accumulator are logically OR with the 8-bit data and the result is placed in the accumulator.                                                                                 |

| RLC        | None          | Rotate the accumulator left                          | Binary bit of the accumulator is rotated left by one position. Bit D7 is placed in the position of D0 as well as in the Carry flag.                                                               |

| RRC        | None          | Rotate the accumulator right                         | Each binary bit of the accumulator is rotated right by one position. Bit D0 is placed in the position of D7 as well as in the Carry flag. CY is modified according to bit D0.                     |

| RAL        | None          | Rotate the accumulator left through carry            | Each binary bit of the accumulator is rotated left by one position through the Carry flag. Bit D7 is placed in the Carry flag, and the Carry flag is placed in the least significant position D0. |

| RAR | None | Rotate the accumulator right through carry | Each binary bit of the accumulator is rotated right by one position through the Carry flag. Bit D0 is placed in the Carry flag, and the Carry flag is placed in the most significant position D7. CY is modified according to bit D0. |

|-----|------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMA | None | Complement accumulator                     | The contents of the accumulator are complemented. No flags are affected.                                                                                                                                                              |

| СМС | None | Complement                                 | The Carry flag is complemented. No other flags are affected.                                                                                                                                                                          |

| STC | None | Set Carry                                  | Set Carry                                                                                                                                                                                                                             |

# ARITHMETIC INSTRUCTUIONS:

| Opcode | Operand                  | Meaning                                                                 | Example           |

|--------|--------------------------|-------------------------------------------------------------------------|-------------------|

| ADD    | R<br>M                   | Add register or memory, to the accumulator                              | Example – ADD K.  |

| ADC    | R<br>M                   | Add register to the accumulator with carry                              | Example – ADC K   |

| ADI    | 8-bit data               | Add the immediate to the accumulator                                    | Example – ADI 55K |

| ACI    | 8-bit data               | Add the immediate to the accumulator with carry                         | Example – ACI 55K |

| LXI    | Reg. pair, 16bit<br>data | Load the register pair immediate Example – LXI K, 3025N                 |                   |

| DAD    | Reg. pair                | Add the register pair to H and L registers                              | Example – DAD K   |

| SUB    | R<br>M                   | Subtract the register or the memory from the accumulator                | Example – SUB K   |

| SBB    | R<br>M                   | Subtract the source and borrow from the accumulator                     | Example – SBB K   |

| SUI    | 8-bit data               | Subtract the immediate from the accumulator                             | Example – SUI 55K |

| SBI    | 8-bit data               | Subtract the immediate from the accumulator with borrow  Example – XCHG |                   |

| INR    | R<br>M                   | Increment the register or the memory by 1                               | Example – INR K   |

| INX | R      | Increment register pair by 1              | Example – INX K |

|-----|--------|-------------------------------------------|-----------------|

| DCR | R<br>M | Decrement the register or the memory by 1 | Example – DCR K |

| DCX | R      | Decrement the register pair by 1          | Example – DCX K |

| DAA | None   | Decimal adjust accumulator                | Example – DAA   |

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=G3iUO96XhC4

# Important Books/Journals For Further Learning Including The Page Nos.:

➤ Gaonkar.R.S, Microprocessor Architecture Programming And Applications With 8085, Wiley Eastern Ltd, New Delhi 2013-Page No(12-16)

**Course Faculty**

(An Autonomous Institution)

L5

#### LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 16ECC09/MICROPROCESSORS AND MICROCONTROLLERS

Course Faculty : Mr.M.DURAISAMY

Unit : I - 8085 PROCESSOR Date of Lecture: 26.08.2021

**Topic of Lecture:** Addressing Modes

#### **Introduction:**

Each instruction requires some data on which it has to operate.

- ➤ There are different techniques to specify data for instructions.

- ➤ These techniques are called addressing modes.

# Prerequisite knowledge for Complete understanding and learning of Topic:

Instruction Sets

#### **Detailed content of the Lecture:**

Intel 8085 uses the following addressing modes:

# Direct Addressing

In this addressing mode, the address of the operand (data) is given in the instruction itself.

#### Example

STA 2400H: It stores the content of the accumulator in the memory location 2400H.

**32, 00, 24:** The above instruction in the code form.

In this instruction, 2400H is the memory address where data is to be stored.

It is given in the instruction itself. The 2nd and 3rd bytes of the instruction specify the address of the memory location.

Here, it is understood that the source of the data is accumulator.

### Register Addressing

In register addressing mode, the operand is in one of the general purpose registers. The Opcode specifies the address of the register(s) in addition to the operation to be performed.

#### **Example:**

MOV A, B: Move the content of B register to register A.

78: The instruction in the code form.

In the above example, MOV A, B is 78H. Besides the operation to be performed the opcode also specifies source and destination registers.

The opcode 78H can be written in binary form as 01111000. The first two bits, i.e. 0 1 are for MOV operation, the next three bits 1 1 1 are the binary code for register A, and the last three bits 000 are the binary code for register B.

# Register Indirect Addressing

In Register Indirect mode of addressing, the address of the operand is specified by a register pair.

### Example

- o **LXI H, 2500 H** Load H-L pair with 2500H.

- o **MOV A, M** Move the content of the memory location, whose address is in H-L pair (i.e. 2500 H) to the accumulator.

- o HLT Halt.

In the above program the instruction MOV A, M is an example of register indirect addressing. For this instruction, the operand is in the memory. The address of the memory is not directly given in the instruction. The address of the memory resides in H-L pair and this has already been specified by an earlier instruction in the program, i.e. LXI H, 2500 H.

#### Immediate Addressing

In this addressing mode, the operand is specified within the instruction itself.

### Example

LXI H, 2500 is an example of immediate addressing. 2500 is 16-bit data which is given in the instruction itself. It is to be loaded into H-L pair.

### o Implicit Addressing

There are certain instructions which operate on the content of the accumulator. Such instructions do not require the address of the operand.

#### Example

CMA, RAL, RAR, etc.

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=nJfTvmYjR90

| Import | ant Book | s/Iournals | for fu | rther lear | ning inc | luding t | the page nos.: |

|--------|----------|------------|--------|------------|----------|----------|----------------|

|        |          | 9,,00      |        |            |          |          | p <del></del>  |

Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (156-188)

**Course Faculty**

(An Autonomous Institution)

(Approved by AICTE, New Delhi, Accredited by NAAC & Affiliated to Anna University) Rasipuram - 637 408, Namakkal Dist., Tamil Nadu

**L6**

# LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

**Course Faculty** : Mrs. P.Subhasundari

**Date of Lecture: 24.08.2021** Unit : I - INTRODUCTION TO 80X86 PROCESSORS

**Topic of Lecture:** Interrupts ,Bus operations , Address pipelined

#### **Introduction**: □

- > Interrupt is signals send by an external device to the processor, to request the processor to perform a particular task or work.

- The processor will check the interrupts always at the 2nd T-state of last machine cycle.

- If there is any interrupt it accept the interrupt and send the INTA (active low) signal to the peripheral.

# Prerequisite knowledge for Complete understanding and learning of Topic:

Processors and controllers

П

# **Detailed content of the Lecture:**

- The processor executes an interrupt service routine (ISR) addressed in program

- It returned to main program by RET instruction.

# **Types of Interrupts:**

It supports two types of interrupts.

- Hardware

- Software

# **Software Interrupts:**

Interrupt number \* 8 = vector address

For RST 5.5 \* 8 = 40 = 28H

Vector addresses of all interrupts

#### Hardware interrupts:

If the interrupt is accepted then the processor executes an interrupt service routine.

The 8085 has five hardware interrupts

- (1) TRAP (2) RST 7.5

- (3) RST 6.5

- (4) RST 5.5

- (5) INTR

□ The

### **(1)TRAP:**

TRAP bas the highest priority and vectored interrupt.

In sudden power failure, it executes a ISR and send the data from main memory to backup memory.

There are two ways to clear TRAP interrupt.

- By resetting microprocessor (External signal)

- ➤ By giving a high TRAP ACKNOWLEDGE (Internal signal)

#### (2)RST 7.5:

- ➤ The RST 7.5 interrupt is a maskable interrupt highest priority.

- ➤ It is edge sensitive. ie. Input goes to high and no need to maintain high state until it recognized.

# Maskable interrupt:

It is disabled by,

- 1.DI instruction

- 2.System or processor reset.

- 3. After reorganization of interrupt.

### (3)RST 6.5 and 5.5:

The RST 6.5 has the third priority whereas RST 5.5 has the fourth priority. INTR is a maskable interrupt. It is disabled by,

- 1.DI, SIM instruction

- 2. System or processor reset.

- 3. After reorganization of interrupt

- 1. It has lowest priority. It is a level sensitive interrupts. ie. Input goes to high and it is necessary to maintain high state until it recognized. The following sequence of events occurs when INTR signal goes high. The 8085 checks the status of INTR signal during execution of each instruction.

- 2. If INTR signal is high, then 8085 complete its current instruction and sends active low interrupt acknowledge signal, if the interrupt is enabled.

- 3. In response to the acknowledge signal, external logic places an instruction OPCODE on the data bus. In the case of multibyte instruction, additional interrupt acknowledge machine cycles are generated by the 8085 to transfer the additional bytes into the microprocessor.

- 4. On receiving the instruction, the 8085 save the address of next instruction on stack and execute received instruction.

#### SIM and RIM for interrupts:

- The 8085 provide additional masking facility for RST 7.5, RST 6.5 and RST 5.5 using SIM instruction.

- The status of these interrupts can be read by executing RIM instruction.

- The masking or unmasking of RST 7.5, RST 6.5 and RST 5.5 interrupts can be performed by moving an 8-bit data to accumulator and then executing SIM instruction.

- The status of pending interrupts can be read from accumulator after executing RIM instruction.

| Video Content/Details of website for further learning (if any):                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| https://www.youtube.com/watch?v=nJfTvmYjR90                                                                                                                                                                  |

| Important Books/Journals for further learning including the page nos.:  Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (352-370) |

|                                                                                                                                                                                                              |

| Course Faculty                                                                                                                                                                                               |

| Course racuity                                                                                                                                                                                               |

| Verified by HOD                                                                                                                                                                                              |

|                                                                                                                                                                                                              |

|                                                                                                                                                                                                              |

|                                                                                                                                                                                                              |

(An Autonomous Institution)

#### LECTURE HANDOUTS

**L7**

# AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : I - INTRODUCTION TO 80X86 PROCESSORS Date of Lecture: 26.08.2021

**Topic of Lecture:** Bus operations, Address pipelined

#### Introduction:

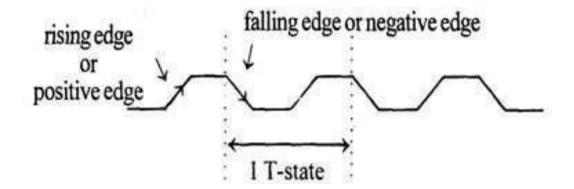

> Timing Diagram is a graphical representation.

➤ It represents the execution time taken by each instruction in a graphical format. The execution time is represented in T-states.

### Prerequisite knowledge for Complete understanding and learning of Topic:

#### **Detailed content of the Lecture:**

#### **Instruction Cycle**

The time required to execute an instruction is called instruction cycle.

#### **Machine Cycle**

The time required to access the memory or input/output devices is called machine cycle.

#### **T-State**

The machine cycle and instruction cycle takes multiple clock periods.

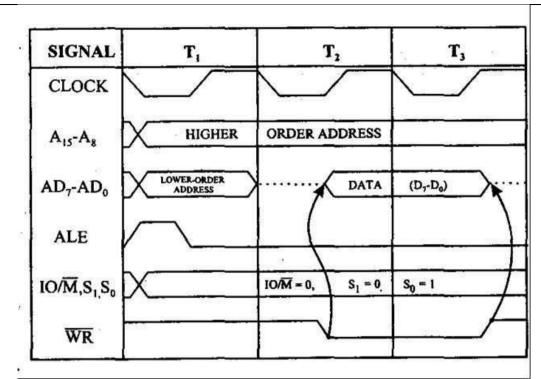

#### Machine cycles of 8085

The 8085 microprocessor has 5 (seven) basic machine cycles. They are

- 1. Opcode fetch cycle (4T)

- 2. Memory read cycle (3 T)

- 3. Memory write cycle (3 T)

- 4. I/O read cycle (3 T)

- 5. I/O write cycle (3 T)

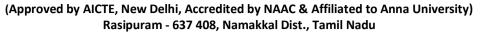

# 1.Opcode fetch machine cycle of 8085:

- Each instruction of the processor has one byte opcode

- In this time, the first, 3 T-states are used for fetching the opcode from memory and the remaining T-states are used for internal operations by the processor.

$T_4$ T, T, T, SIGNAL CLOCK ADDRESS A15-A8 HIGHER ORDER MEMORY UNSPECIFIED LOWER-ORDER MEMORY ADDR AD,-AD OPCODE (D7-D0) ALE  $IO/\overline{M}, S_1, S_0$  $10/\overline{M} = 0$  $S_1 = 1, S_0 = 1$ RD

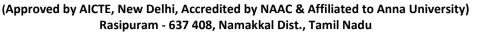

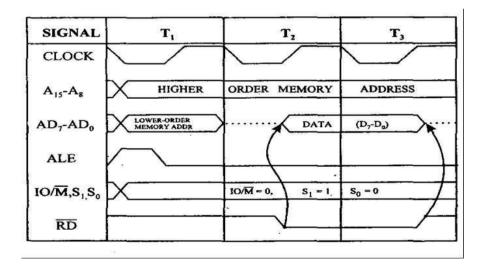

# 2.Memory Read Machine Cycle of 8085:

- The memory read machine cycle is executed by the processor to read a data byte from memory.

- The processor takes 3T states to execute this cycle.

- The instructions which have more than one byte word size will use the machine cycle after the opcode fetch machine cycle

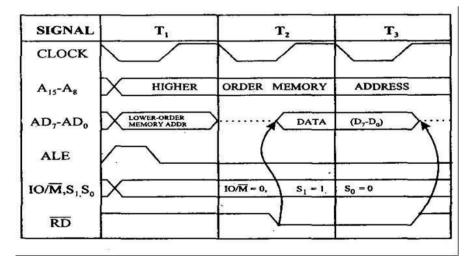

### 3. Memory Write Machine Cycle of 8085

The memory write machine cycle is executed by the processor to write a data byte in a memory location

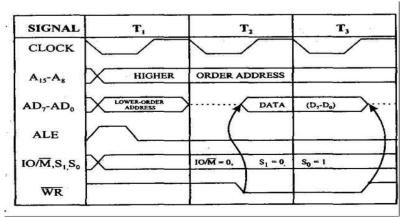

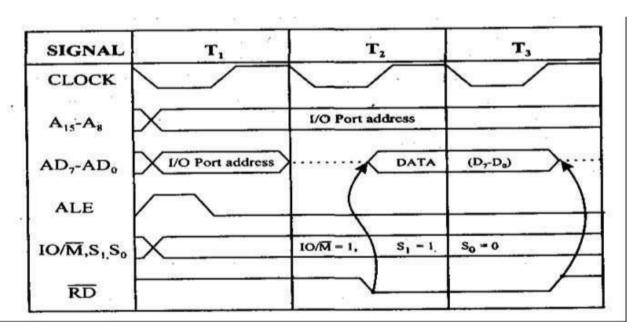

### 4. I/O Read Cycle of 8085

- The I/O Read cycle is executed by the processor to read a data byte from I/O port or from the peripheral, which is I/O, mapped in the system.

- The processor takes 3T states to execute this machine cycle.

- The IN instruction uses this machine cycle during the execution

I/O Read Cycle

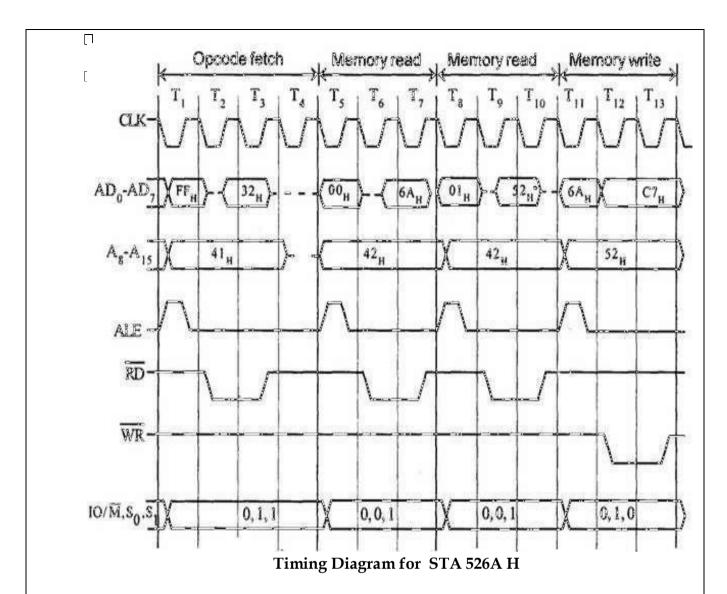

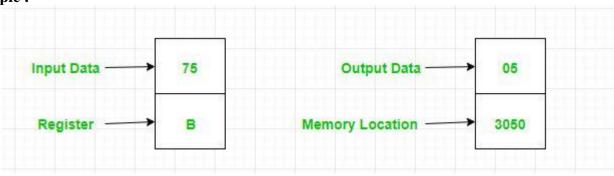

### Timing diagram for STA 526AH

- STA means Store Accumulator -The contents of the accumulator is stored in the specified address(526A).

- The opcode of the STA instruction is said to be 32H. It is fetched from the memory

- 41FFH(see fig). OF machine cycle

- Then the lower order memory address is read(6A). Memory Read Machine Cycle

- Read the higher order memory address (52).- Memory Read Machine Cycle

- The combination of both the addresses are considered and the content from accumulator is written in 526A. Memory Write Machine Cycle

# Timing diagram for INR M

- o Fetching the Opcode 34H from the memory 4105H. (OF cycle)

- o Let the memory address (M) be 4250H. (MR cycle -To read Memory address and data) Let the content of that memory is 12H.

- o Increment the memory content from 12H to 13H. (MW machine cycle)

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=EaRqC3dLoWY

# Important Books/Journals for further learning including the page nos.:

➤ Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (78-83)

**Course Faculty**

(An Autonomous Institution)

#### LECTURE HANDOUTS

**L8**

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : I - INTRODUCTION TO 80X86 PROCESSORS Date of Lecture: 27.08.2021

**Topic of Lecture:** Memory organization and I/O organization

#### **Introduction:**

- Memory-mapping is a mechanism that maps a portion of a file, or an entire file, on disk to a range of addresses within an application's address space.

- ➤ The application can then access files on disk in the same way it accesses dynamic memory.

## Prerequisite knowledge for Complete understanding and learning of Topic:

> Timing Diagram

#### **Detailed content of the Lecture:**

### Mapped Memory

- Simplicity is the advantage of mapping memory among the devices in a system:

- o There is no need to partition data. All devices see the complete memory image.

- There is no need to allocate space in device memory or to manually copy data.

All data transfers are implicitly performed by the kernel as needed.

- There is no need to use streams to overlap data transfers with kernel execution. All data transfers originate from the kernel and are asynchronous.

Application performance is the cost associated with this simplicity. Using mapped memory does mean that the programmer gives up control over the data movement between the host and devices. From the forums and experience, it is not unusual for kernel performance to drop when using mapped memory because there are no guarantees when or how often data will need to be transferred across the PCIe bus. Other considerations to using mapped memory include:

- If the contents of the mapped memory are modified, the application must synchronize memory accesses using streams or events to avoid any potential read-after-write, write-after-read, or write-after write hazards.

- The host memory needs to be page aligned. The simplest and most portable way to enforce this is to use when allocating mapped host memory.

The simplicity of using mapped memory is illustrated by which fills a mapped memory vector using one or more GPUs in the system. The highlighted command creates a mapped region of memory when passed the flag. This region is freed at the end of the program with Thrust was used to make this code concise and easy to read.

The device\_pointer\_cast method was used to correctly cast the mapped host memory for the thrust sequence method.

The highlighted call to ensures that the mapped data is synchronized between the host and devices prior to checking the results on the host. All data transfers occur transparently and asynchronously. Finally, the contents of the mapped region of memory are checked for correctness on the host and the mapped region is freed.

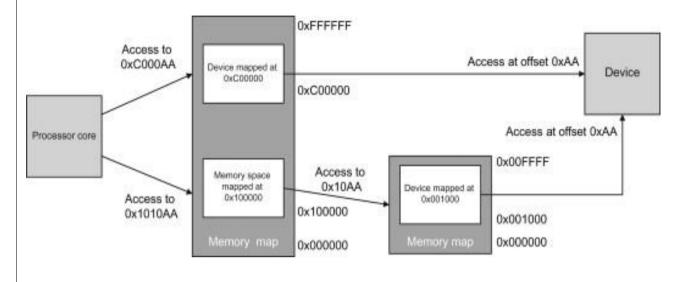

### Memory Maps

- The memory map is a fundamental service provided by the Simics framework and is a core component to enabling very fast simulation.

- Memory maps take care of routing memory accesses from their source to their destination, based on the address of the access.

- Memory maps replace the explicit modeling of buses in Simics. Memory maps provide the software view of the bus system, but not the hardware view.

- It is a typical transaction-level abstraction from the hardware behavior. Simics memory maps are dynamic and can be changed during the simulation, both by the user and more commonly from various devices and components that manipulate memory mappings to implement dynamic target behaviors.

An example of the memory map for a simple system. It is not a complete system, but instead it is just intended to show a few typical cases of memory mappings. The processor has a memory map that shows how RAM and a few devices are mapped, as well as a PCIe memory space in which PCIe devices are mapped.

The basic building block for creating memory maps are objects of the memory-space class. When a memory transaction is initiated from an origin, typically a processor model, the address a of the access is passed unmodified to the first memory space.

For a processor model, the first memory space typically represents the physical address space of the processor. If nothing is mapped at address *a*, an access error is signaled to the origin.

However, if the access falls within the range of a second memory space that is mapped in the first memory space at offset b, the transaction is passed on to the second memory space with the local address c=a-b. Memory spaces are traversed in this fashion until an unmapped address is reached or the transaction terminates in a device model. This process is shown in Figure.

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=jkT9Bgz8PAg

### Important Books/Journals for further learning including the page nos.:

➤ Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (41-45)

**Course Faculty**

(An Autonomous Institution)

LITE L9

LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : I - INTRODUCTION TO 80X86 PROCESSORS Date of Lecture: 30.08.2021

**Topic of Lecture:** 16/32 bit transfer

### **Introduction:**

- ➤ The memory is made up of semiconductor material used to store the programs and data.

- ➤ Data in Microprocessor can move from one location to another.

# Prerequisite knowledge for Complete understanding and learning of Topic:

Classification of Memories

ПП

#### **Detailed content of the Lecture:**

#### **Memory Interfacing**

Three types of memory is,

- Process memory

- Primary or main memory

- Secondary memory

#### Typical EPROM and Static RAM

- Having two power supply pins (one for connecting required supply voltage and the other for connecting ground).

- The control signals needed for static RAM are chip select (chip enable), read control(output enable) and write control (write enable).

- The control signals needed for read operation in EPROM are chip select (chip enable) and read control (output enable).

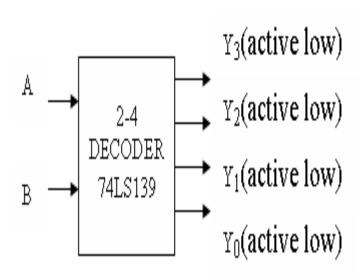

Block Diagram of 2-4 Decoder

**Example for Memory Interfacing**

address lines. So, n = 16.

П

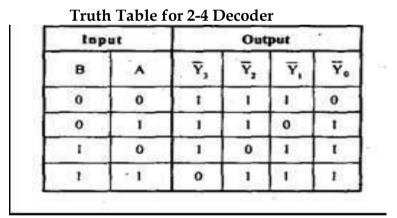

Consider a system in which the full memory space 64kb is utilized for EPROM memory. Interface the EPROM with 8085 processor.

The memory capacity is 64 Kbytes. i.e  $2^n = 64 \times 1000$  bytes where  $n = 64 \times 1000$

- In this system the entire 16 address lines of the processor are connected to address input pins of memory IC in order to address the internal locations of memory.

- The chip select (CS) pin of EPROM is permanently tied to logic low (i.e., tied to ground).

- Since the processor is connected to EPROM, the active low RD pin is connected to active low output enable pin of EPROM.

# Video Content / Details of website for further learning (if any):

https://www.youtube.com/watch?v=jkT9Bgz8PAg

# Important Books/Journals for further learning including the page nos.:

➤ Gaonkar.R.S, Microprocessor architecture programming and applications with 8085, wiley eastern ltd, New Delhi 2013-Page no (30-41)

**Course Faculty**

(An Autonomous Institution)

#### LECTURE HANDOUTS

L10

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : II - ASSEMBLY LANGUAGE PROGRAMMING

**Date of Lecture:** 01.09.2021

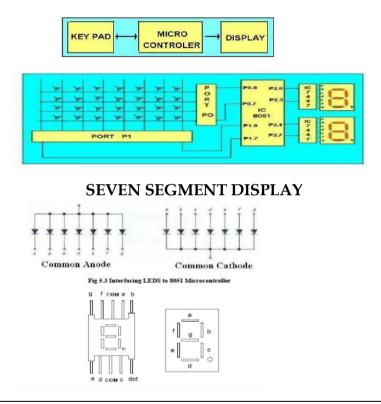

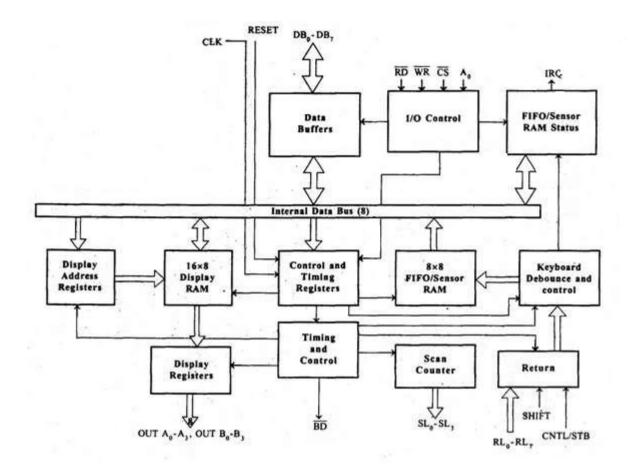

Topic of Lecture: Keyboard Interfacing

#### Introduction:

Keypads are a part of HMI or Human Machine Interface and play really important role in a small embedded system where human interaction or human input is needed. Matrix keypads are well known for their simple architecture and ease of interfacing with any microcontroller.

### Prerequisite knowledge for Complete understanding and learning of Topic:

Interfacing functions

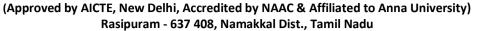

### Detailed content of the Lecture: Keyboard Interfacing

- ➤ The key board here we are interfacing is a matrix keyboard. This key board is designed with a particular rows and columns.

- ➤ These rows and columns are connected to the microcontroller through its ports of the micro controller 8051. We normally use 8\*8 matrix key board.

- ➤ So only two ports of 8051 can be easily connected to the rows and columns of the key board. Whenever a key is pressed, a row and a column gets shorted through that pressed key and all the other keys are left open.

- ➤ When a key is pressed only a bit in the port goes high. Which indicates microcontroller that the key is pressed. By this high on the bit key in the corresponding column is identified.

- ➤ Once we are sure that one of key in the key board is pressed next our aim is to identify that key. To do this we firstly check for particular row and then we check the corresponding column the key board.

- To check the row of the pressed key in the keyboard, one of the row is made high by making one of bit in the output port of 8051 high.

- ➤ This is done until the row is found out. Once we get the row next out job is to find out the column of the pressed key.

- ➤ The column is detected by contents in the input ports with the help of a counter. The content of the input port is rotated with carry until the carry bit is set.

- ➤ The contents of the counter is then compared and displayed in the display. This display is designed using a seven segment display and a BCD to seven segment decoder IC 7447.

- ➤ The BCD equivalent number of counter is sent through output part of 8051 displays the number of pressed key.

# Video Content / Details of website for further learning (if any):

www.youtube.com/watch?v=liRtPtvj7bFU&noredirect=1

# Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 (R1-363-370)

**Course Faculty**

(An Autonomous Institution)

# LECTURE HANDOUTS

L11

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : II - ASSEMBLY LANGUAGE PROGRAMMING

**Date of Lecture:** 02.09.2021

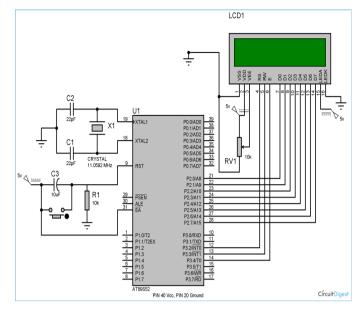

**Topic of Lecture:** LCD Interfacing

#### **Introduction:**

• LCD is one of the most used display unit.

- Interfacing LCD with 8051 microcontroller might look quite complex to newbie, but after understanding the concept it would look very simple and easy.

- Although it may be time taking because you need to understand and connect 16 pins of LCD to the microcontroller. So first let's understand the 16 pins of LCD module.

- Display units are the most important output devices in embedded projects and electronics products..

### Prerequisite knowledge for Complete understanding and learning of Topic:

➤ 8085 & 8051 Features

#### **Detailed content of the Lecture:**

- LCD display is an inevitable part in almost all embedded projects and this article is about interfacing a 16×2 LCD with 8051 microcontroller.

- Many guys find it hard to interface LCD module with the 8051 but the fact is that if

you learn it properly, it's a very easy job and by knowing it you can easily design

embedded projects like digital voltmeter / ammeter, digital clock, home automation

displays, status indicator display, digital code locks, digital speedometer/ odometer,

display for music players etc.

- Thoroughly going through this article will make you able to display any text (including the extended characters) on any part of the 16×2 display screen. In order to understand the interfacing first you have to know about the 16×2 LCD module.

We can divide it in five categories, Power Pins, contrast pin, Control Pins, Data pins and Backlight pins.

| Category                                | Pin<br>NO. | Pin Name                                                                      | Function                                                         |  |  |

|-----------------------------------------|------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

|                                         | 1          | VSS                                                                           | Ground Pin, connected to Ground                                  |  |  |

| Power Pins                              | 2          | VDD or<br>Vcc                                                                 | Voltage Pin +5V                                                  |  |  |

| Contrast Pin                            | 3          | V0 or VEE                                                                     | Contrast Setting, connected to Vcc thorough a variable resistor. |  |  |

|                                         | 4          | RS                                                                            | Register Select Pin, RS=0 Command mode, RS=1 Data mode           |  |  |

| Control Pins                            | 5          | RW                                                                            | Read/ Write pin, RW=0 Write mode,<br>RW=1 Read mode              |  |  |

|                                         | 6          | Е                                                                             | Enable, a high to low pulse need to enable the LCD               |  |  |

| 1 1 12 12 12 12 12 12 12 12 12 12 12 12 |            | Data Pins, Stores the Data to be displayed on LCD or the command instructions |                                                                  |  |  |

| Backlight                               | 15         | LED+ or A                                                                     | To power the Backlight +5V                                       |  |  |

| Pins                                    | 16         | LED- or K                                                                     | Backlight Ground                                                 |  |  |

All the pins are clearly understandable by their name and functions, except the control pins, so they are explained below:

**RS:** RS is the register select pin. We need to set it to 1, if we are sending some data to be displayed on LCD. And we will set it to 0 if we are sending some command instruction like clear the screen (hex code 01).

**RW:** This is Read/write pin, we will set it to 0, if we are going to write some data on LCD. And set it to 1, if we are reading from LCD module. Generally this is set to 0, because we do not have need to read data from LCD. Only one instruction "Get LCD status", need to be read some times.

**E:** This pin is used to enable the module when a high to low pulse is given to it. A pulse of 450 ns should be given. That transition from HIGH to LOW makes the module ENABLE.

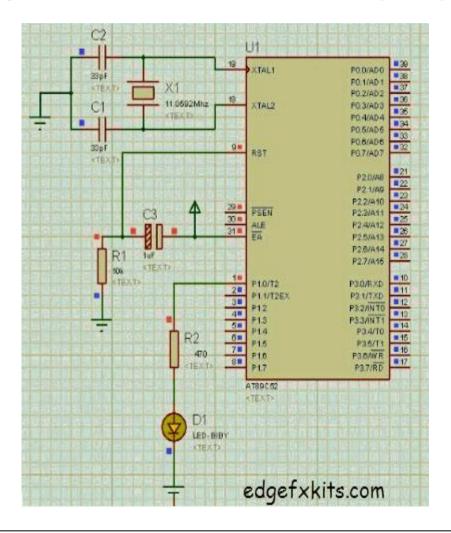

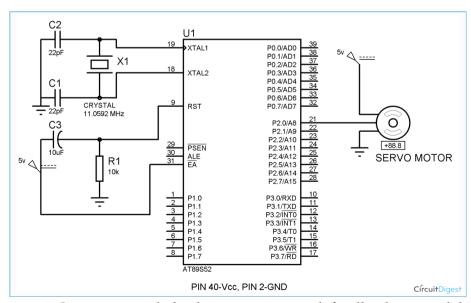

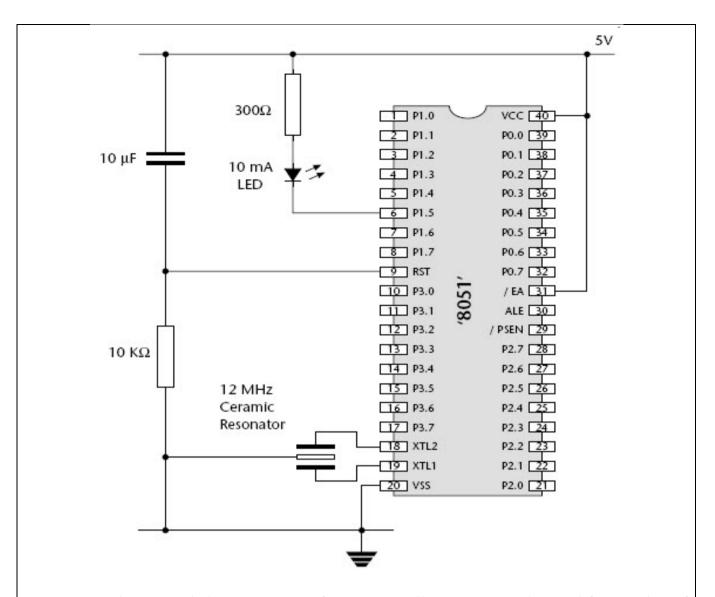

# Circuit Diagram and Explanation

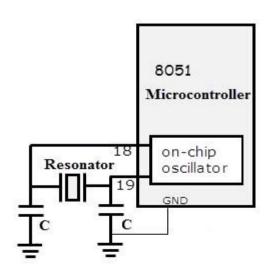

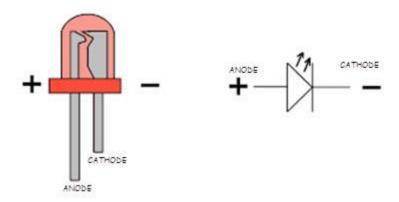

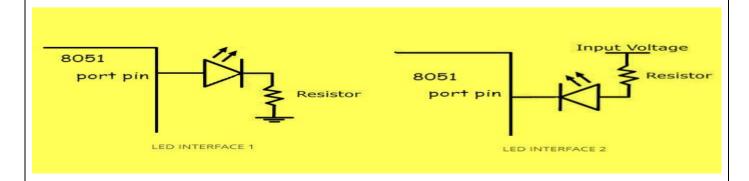

- Circuit diagram for LCD interfacing with 8051 microcontroller is shown in the above figure. If you have basic understanding of 8051 then you must know about EA(PIN 31), XTAL1 & XTAL2, RST pin(PIN 9), Vcc and Ground Pin of 8051 microcontroller. I have used these Pins in above circuit. If you don't have any idea about that then I recommend you to read this Article LED Interfacing with 8051 Microcontroller before going through LCD interfacing.

- So besides these above pins we have connected the data pins (D0-D7) of LCD to the Port 2 (P2\_0 P2\_7) microcontroller. And control pins RS, RW and E to the pin 12, 13, 14 (pin 2, 3, 4 of port 3) of microcontroller respectively.

- PIN 2(VDD) and PIN 15(Backlight supply) of LCD are connected to voltage (5v), and PIN 1 (VSS) and PIN 16(Backlight ground) are connected to ground.

- Pin 3(V0) is connected to voltage (Vcc) through a variable resistor of 10k to adjust the contrast of LCD. Middle leg of the variable resistor is connected to PIN 3 and other two legs are connected to voltage supply and Ground.

# Video Content / Details of website for further learning:

www.youtube.com/watch?v=liRtPtvj7bFU&noredirect=1

### Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 (R1-352-362)

**Course Faculty**

(An Autonomous Institution)

L12

## LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : II - ASSEMBLY LANGUAGE PROGRAMMING

**Date of Lecture:** 03.09.2021

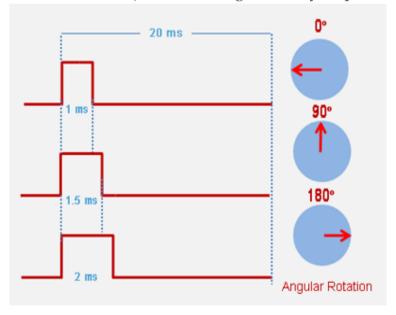

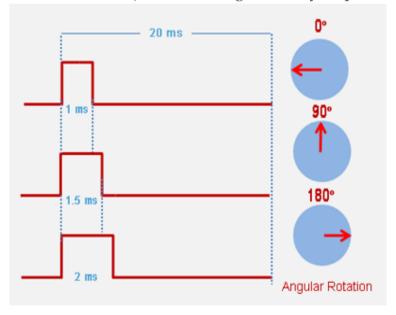

**Topic of Lecture:** Stepper Motor Control

#### **Introduction:**

Stepper Motor Control using 8051 Microcontroller. A stepper motor is a brushless and synchronous motor which divides the complete rotation into number of steps. Each stepper motor will have some fixed step angle and motor rotates at this angle.

# Prerequisite knowledge for Complete understanding and learning of Topic:

Stepper motor operation

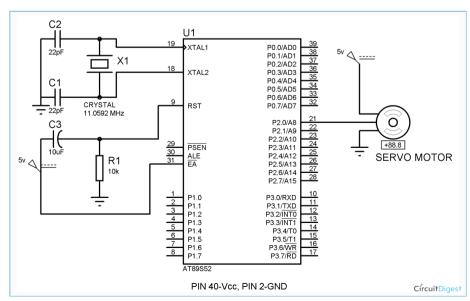

Detailed content of the Lecture: Stepper motor Interfacing/Control using 8085 and 8051

## **Stepper Motor**

A stepper motor is a device that translates electrical pulses into mechanical movement in steps of fixed step angle.

- The stepper motor rotates in steps in response to the applied signals.

- It is mainly used for position control.

- It is used in disk drives, dot matrix printers, plotters and robotics and process control circuits.

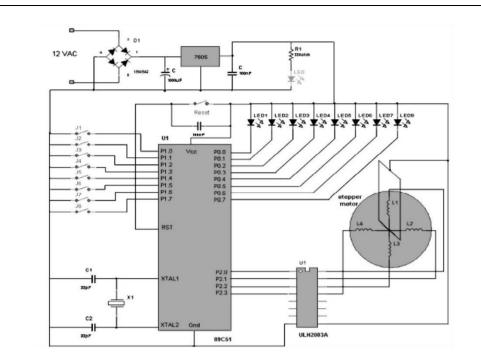

The complete board consists of transformer, control circuit, keypad and stepper motor as shown in snap.

The circuit has inbuilt 5 V power supply so when it is connected with transformer it will give the supply to circuit and motor both. The 8 Key keypad is connected with circuit through which user can give the command to control stepper motor. The control circuit includes micro controller 89C51, indicating LEDs, and current driver chip ULN2003A. One can program the controller to control the operation of stepper motor. He can give different commands through keypad like, run clockwise, run anticlockwise, increase/decrease RPM, increase/decrease revolutions, stop motor, change the mode, etc.

Unipolar stepper motor:- unipolar stepper motor has four coils. One end of each coil is tied together and it gives common terminal which is always connected with positive terminal of supply. The other ends of each coil are given for interface. Specific color code may also be given. Like in my motor orange is first coil (L1), brown is second (L2), yellow is third (L3), black is fourth (L4) and red for common terminal.

By means of controlling a stepper motor operation we can

- 1. Increase or decrease the RPM (speed) of it

- 2. Increase or decrease number of revolutions of it

- 3. Change its direction means rotate it clockwise or anticlockwise

To vary the RPM of motor we have to vary the PRF (Pulse Repetition Frequency). Number of applied pulses will vary number of rotations and last to change direction we have to change pulse sequence.

So all these three things just depends on applied pulses. Now there are three different modes to rotate this motor

- 1. Single coil excitation

- 2. Double coil excitation

- 3. Half step excitation

The table given below will give you the complete idea that how to give pulses in each mode

| Single coil excitation |               | Double coil excitation |               | Half step excitation |               |

|------------------------|---------------|------------------------|---------------|----------------------|---------------|

| Clockwise              | Anticlockwise | Clockwise              | Anticlockwise | Clockwise            | Anticlockwise |

| L4 L3 L2 L1            | LA L3 L2 L1   | L4 L3 L2 L1            | L4 L3 L2 L1   | L4 L3 L2 L1          | L4 L3 L2 L1   |

| 0 0 0 1                | 0 0 0 1       | 0 0 1 1                | 0 0 1 1       | 0001                 | 0001          |

| 0 0 1 0                | 1 0 0 0       | 0 1 1 0                | 1 0 0 1       | 0011                 | 0011          |

| 0 1 0 0                | 0 1 0 0       | 1 1 0 0                | 1 1 0 0       | 0010                 | 1000          |

| 1 0 0 0                | 0 0 1 0       | 1 0 0 1                | 0 1 1 0       | 0110                 | 1001          |

|                        |               |                        | •             | 0100                 | 0100          |

|                        |               |                        | Ī             | 1100                 | 1100          |

|                        |               |                        | Ī             | 1000                 | 0010          |

|                        |               |                        | Ī             | 1001                 | 0110          |

The circuit consists of very few components. The major components are 7805, 89C51 and ULN2003A.

## Connections:-

- 1. The transformer terminals are given to bridge rectifier to generate rectified DC.

- 2. It is filtered and given to regulator IC 7805 to generate 5 V pure DC. LED indicates supply is ON.

- 3. All the push button micro switches J1 to J8 are connected with port P1 as shown to form serial keyboard.

- 4. 12 MHz crystal is connected to oscillator terminals of 89C51 with two biasing capacitors.

- 5. All the LEDs are connected to port P0 as shown

- 6. Port P2 drives stepper motor through current driver chip ULN2003A.

- 7. The common terminal of motor is connected to Vcc and rest all four terminals are connected to port P2 pins in sequence through ULN chip.

Video Content / Details of website for further learning (if any):

www.youtube.com/watch?v=liRtPtvj7bFU&noredirect=1

Important Books/Journals for further learning including the page nos.:

R.S. Gaonkar, 'Microprocessor Architecture Programming and Application', with 8085, Wiley Eastern Ltd., New Delhi, 2013 (R3 498-507)

**Course Faculty**

(An Autonomous Institution)

LECTURE HANDOUTS L13

AI&DS

II / III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : II - ASSEMBLY LANGUAGE PROGRAMMING

**Date of Lecture:** 06.09.2021

**Topic of Lecture: Stepper motor Control**

#### **Introduction:**

- A stepper motor is a device that translates electrical pulses into mechanical movement in steps of fixed step angle.

- The stepper motor rotates in steps in response to the applied signals.

- It is mainly used for position control.

- It is used in disk drives, dot matrix printers, plotters and robotics and process control circuits.

## Prerequisite knowledge for Complete understanding and learning of Topic:

- Interfacing

- Motor Driver Circuit

- Stepper motor and its operation

# Detailed content of the Lecture: Stepper motor Control

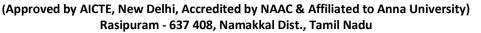

- Stepper motors have a permanent magnet called rotor (also called the shaft) surrounded by a stator. The most common stepper motors have four stator windings that are paired with a center-tap. This type of stepper motor is commonly referred to as a four-phase or unipolar stepper motor.

- The center tap allows a change of current direction in each of two coils when a winding is grounded, thereby resulting in a polarity change of the stator.

# Interfacing

- Even a small stepper motor require a current of 400 mA for its operation.

- But the ports of the microcontroller cannot source this much amount of current. If such a motor is directly connected to the microprocessor/microcontroller ports, the motor may draw large current from the ports and damage it. So a suitable driver circuit is used with the microprocessor/microcontroller to operate the motor.

## **Motor Driver Circuit (ULN2003)**

Stepper motor driver circuits are available readily in the form of ICs. ULN2003 is one such driver IC which is a High-Voltage High-Current Darlington transistor array and can give a current of 500mA. This current is sufficient to drive a small stepper motor. Internally, it has protection diodes used to protect the motor from damage due to back emf and large eddy currents. So, this ULN2003 is used as a driver to interface the stepper motor to the microcontroller.

## Operation

- The important parameter of a stepper motor is the step angle.

- It is the minimum angle through which the motor rotates in response to each excitation pulse. In a four phase motor if there are 200 steps in one complete rotation then then the step angle is 360/200 = 1.8O. So to rotate the stepper motor we have to apply the excitation pulse. For this the controller should send a hexa decimal code through one of its ports.

- The hex code mainly depends on the construction of the stepper motor. So, all the stepper motors do not have the same Hex code for their rotation. (refer the operation manual supplied by the manufacturer.) For example, let us consider the hex code for a stepper motor to rotate in clockwise direction is 77H, BBH, DDH and EEH. This hex code will be applied to the input terminals of the driver through the assembly language program

```

ASSEMBLY LANGUAGE PROGRAM (8051)

Main: MOV A, # 0FF H

; Initialization of Port 1

MOV P1, A

MOV A, #77 H

; Code for the Phase 1

MOV P1, A

ACALL DELAY

; Delay subroutine

MOV A, # BB H

; Code for the Phase II

MOV P1, A

ACALL DELAY

; Delay subroutine.

MOV A, # DD H

; Code for the Phase III

MOV P1, A

ACALL DELAY

; Delay subroutine

MOV A, # EE H

: Code for the Phase 1

MOV P1, A

; Delay subroutine SJMP

ACALL DELAY

MAIN; Keep the motor rotating continuously.

DELAY Subroutine

MOV R4, #0FF H

; Load R4 with FF

MOV R5, # 0FF

; Load R5 with FF

LOOP1: DJNZ R4, LOOP1

; Decrement R4 until zero, wait

LOOP2: DINZ R5, LOOP2

; Decrement R5 until zero, wait

RET

; Return to main program.

Video Content / Details of website for further learning (if any):

https://www.zseries.in > 8085 microprocessor > stepper motor

Important Books/Journals for further learning including the page nos.:

```

R.S. Gaonkar, 'Microprocessor Architecture Programming and Application', with 8085,

Wiley Eastern Ltd., New Delhi, 2013 (R3 498-507)

**Course Faculty**

(An Autonomous Institution)

L14

# LECTURE HANDOUTS

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : II - ASSEMBLY LANGUAGE PROGRAMMING

**Date of Lecture:** 08.09.2021

# **Topic of Lecture: Washing Machine Control**

#### **Introduction:**

AT89S51 microcontroller is used to control the process of washing cycle and to drive the external output devices such as water inlet valve, wash motor, water drain valve. The control strategy program for AT89S51 microcontroller is implemented by using assembly language.

# Prerequisite knowledge for Complete understanding and learning of Topic:

➤ Basic operations of 8085 & 8051

## Detailed content of the Lecture: Washing Machine Control

- Many washing m/c shell in the market has mechanical controlled sequence for activated the timer and the sequence back and forth for their motor; washing motor or spinning motor. Spinning motor control only has one direction only, and its simple could be changed to the discrete mechanical timer which sells on the market. But washing motor control has 2 direction

- for this purpose, it means to squeeze the clothes, it must go to forward and then reversed. The sequence is like this:

First, go to forward direction for about a few seconds

Than stop, while the chamber is still rotate

Second, go back to reverse direction for about a few seconds

Than stop, while the chamber is still rotate

And so on, back and forth, until the the timer elapsed

#### **SCHEMATIC**

- Timing sequence like the above description, can be implemented with many way, by using discrete electronic components, timer, using a program or a microcontroller or microprocessor, etc.

- Because I am learning the PIC microcontroller for right now, I will implement this function using this microcontroller, but for you who familiar with another kind of microcontroller my adapted it to your purpose.

- By using PIC micro, it can be made more compact. First I plan to make 2 buttons,

- 1 for set the timer and another for reset the timer or for the emergency stop push button. Then to know the timer works or not, I need a visual display. For this purpose I will use

- 7-segmen display showing the rest of the timer. To run the motor sequence of course I need a pair of relays (power relays, about 3 Amperes output), one for forward and another for reverse option.

- I will use the very common family of PIC micro, ie: 16F84A, because this is the most popular type and very simples used and very much used. Also can be obtained easily in the market. But this is the medium type of PIC micro family.

- It has 1kByte of memory (EEPROM type) and 13 I/O pins. It can be reprogrammable thousands times. Because the I/O just only 13 pins, I used a BCD to 7-segmen chip. So it will left a few I/O pins for expanded in the future. You can omitted this chip for timing sequence purpose and save one IC price, because the I/O just exactly enough.

```

I/O port A-0 = SET push button

I/O port A-1 = RST push button

I/O port A-2 = Reserved

I/O port A-3 = Reserved

I/O port A-4 = Reserved

I/O port B-0 = Forward Relay (Run motor forward)

I/O port B-1 = Reverse Relay (Run motor reverse)

I/O port B-2 = Activated unit 7-segmen (multiplexed)

I/O port B-3 = Activated ten 7-segmen (multiplexed)

I/O port B-4 = BCD data A (for 7-segmen)

I/O port B-5 = BCD data B (for 7-segmen)

I/O port B-6 = BCD data C (for 7-segmen)

I/O port B-7 = BCD data D (for 7-segmen)

Also integrated power supply to run it modularly

```

## Working of Washing Machine

- The direction of rotation can be controlled When switchS1 is in position A, coil L1 of the motor receives the current directly, whereas coil L2 receives the current with a phase shift due to capacitor C. So the rotor rotates in clockwise direction (see Fig. 2(a)).

- When switch S1 is in position B, the reverse happens and the rotor rotates in anticlockwise direction Thus switch S1 can change the rotation direction. The motor cannot be reversed instantly.

- It needs a brief pause between switching directions, or else it may get damaged. For this purpose, another spin direction control timer (IC2) is employed. It is realised with an IC 555. This timer gives an alternate "on" and "off" time duration of 10 seconds and 3 seconds, respectively.

- So after every 10 seconds of running (either in clockwise or anticlockwise direction),

the motor stops for a brief duration of 3 seconds. The values of R3 and R4 are calculated accordingly. The master timer is realised with monostable IC555 (IC1) and its "on" time is decided by the resistance of 1-megaohm potmeter VR. A 47-kilo-ohm resistor is added in series so that even when the VR knob in zero resistance position, the net series resistance is not zero.

# Video Content / Details of website for further learning (if any):

www.youtube.com/watch?v=liRtPtvj7bFU&noredirect=1

# Important Books/Journals for further learning including the page nos.:

Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely, The 8051 Micro Controller and Embedded Systems, PHI Pearson Education, 5th Indian reprint, 2003 (Page No: 465-472)

**Course Faculty**

(An Autonomous Institution)

LECTURE HANDOUTS L15

AI&DS

II/III

Course Name with Code: 19ADC03/ PROCESSOR ARCHITECTURE

Course Faculty : Mrs. P.Subhasundari

Unit : II - ASSEMBLY LANGUAGE PROGRAMMING

**Date of Lecture:** 09.09.2021

## **Topic of Lecture: Washing Machine Control**

#### Introduction:

AT89S51 microcontroller is used to control the process of washing cycle and to drive the external output devices such as water inlet valve, wash motor, water drain valve. The control strategy program for AT89S51 microcontroller is implemented by using assembly language.

# Prerequisite knowledge for Complete understanding and learning of Topic:

➤ Basic operations of 8085 & 8051

## Detailed content of the Lecture: Washing Machine Control

- Many washing m/c shell in the market has mechanical controlled sequence for activated the timer and the sequence back and forth for their motor; washing motor or spinning motor. Spinning motor control only has one direction only, and its simple could be changed to the discrete mechanical timer which sells on the market. But washing motor control has 2 direction

- for this purpose, it means to squeeze the clothes, it must go to forward and then reversed. The sequence is like this:

First, go to forward direction for about a few seconds

Than stop, while the chamber is still rotate

Second, go back to reverse direction for about a few seconds

Than stop, while the chamber is still rotate

And so on, back and forth, until the the timer elapsed

#### **SCHEMATIC**

- Timing sequence like the above description, can be implemented with many way, by using discrete electronic components, timer, using a program or a microcontroller or microprocessor, etc.

- Because I am learning the PIC microcontroller for right now, I will implement this

function using this microcontroller, but for you who familiar with another kind of

microcontroller my adapted it to your purpose.

- By using PIC micro, it can be made more compact. First I plan to make 2 buttons,

- 1 for set the timer and another for reset the timer or for the emergency stop push button. Then to know the timer works or not, I need a visual display. For this purpose I will use

- 7-segmen display showing the rest of the timer. To run the motor sequence of course I need a pair of relays (power relays, about 3 Amperes output), one for forward and another for reverse option.

- I will use the very common family of PIC micro, ie: 16F84A, because this is the most popular type and very simples used and very much used. Also can be obtained easily in the market. But this is the medium type of PIC micro family.

- It has 1kByte of memory (EEPROM type) and 13 I/O pins. It can be reprogrammable thousands times. Because the I/O just only 13 pins, I used a BCD to 7-segmen chip. So it will left a few I/O pins for expanded in the future. You can omitted this chip for timing sequence purpose and save one IC price, because the I/O just exactly enough.

```

I/O port A-0 = SET push button

I/O port A-1 = RST push button

I/O port A-2 = Reserved

I/O port A-3 = Reserved

I/O port A-4 = Reserved

I/O port B-0 = Forward Relay (Run motor forward)

I/O port B-1 = Reverse Relay (Run motor reverse)

I/O port B-2 = Activated unit 7-segmen (multiplexed)

I/O port B-3 = Activated ten 7-segmen (multiplexed)

I/O port B-4 = BCD data A (for 7-segmen)

I/O port B-5 = BCD data B (for 7-segmen)

I/O port B-6 = BCD data C (for 7-segmen)

I/O port B-7 = BCD data D (for 7-segmen)

Also integrated power supply to run it modularly

```

## Working of Washing Machine

- The direction of rotation can be controlled When switchS1 is in position A, coil L1 of the motor receives the current directly, whereas coil L2 receives the current with a phase shift due to capacitor C. So the rotor rotates in clockwise direction (see Fig. 2(a)).

- When switch S1 is in position B, the reverse happens and the rotor rotates in anticlockwise direction Thus switch S1 can change the rotation direction. The motor cannot be reversed instantly.

- It needs a brief pause between switching directions, or else it may get damaged. For this purpose, another spin direction control timer (IC2) is employed. It is realised with an IC 555. This timer gives an alternate "on" and "off" time duration of 10 seconds and 3 seconds, respectively.

- So after every 10 seconds of running (either in clockwise or anticlockwise direction),

the motor stops for a brief duration of 3 seconds. The values of R3 and R4 are calculated accordingly. The master timer is realised with monostable IC555 (IC1) and its "on" time is decided by the resistance of 1-megaohm potmeter VR. A 47-kilo-ohm resistor is added in series so that even when the VR knob in zero resistance position, the net series resistance is not zero.

# Video Content / Details of website for further learning (if any):